# IDENTIFICATION AND OPTIMIZATION OF SHARING PATTERNS FOR SCALABLE SHARED-MEMORY MULTIPROCESSORS

by

#### **STEFANOS KAXIRAS**

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy (Computer Sciences)

at the

UNIVERSITY OF WISCONSIN-MADISON

1998

#### **Abstract**

Distributed shared-memory architectures typically employ a directory-based protocol to maintain cache coherence. Identifying sharing patterns in parallel programs and applying specialized optimizations can increase cache-coherence protocol efficiency and yield performance improvements. In this thesis, I propose and study both optimizations to sharing patterns and techniques to identify sharing patterns.

The main thrust of the thesis is GLOW, a comprehensive optimization for wide sharing—a sharing pattern that is a serious obstacle to scalability to large numbers of processors. I present GLOW in the form of extensions to the SCI ANSI/IEEE standard. GLOW is implemented in special network switches and incorporates characteristics that are not found together in previous proposals: scalable writes *and* scalable reads, network locality (by exploiting the abundance of widely-shared data to satisfy requests locally), simplicity, transparency to the base protocol, and network topology independence. With simulation, I show that for programs with wide sharing, GLOW can be more than twice as fast as SCI in large systems.

Furthermore, I examine techniques to identify sharing patterns. I propose a novel approach based on maintaining the history of load and store instructions in relation to coherence events (e.g., cache-misses) and predicting their future behavior. This *instruction-based* approach, differs from previously proposed adaptive protocols (*address-based techniques*) which maintain data-access history and predict future accesses. Instruction-based prediction can offer accurate detection of sharing patterns using few resources in the form of small predictors per node.

I examine instruction-based prediction for three sharing patterns: wide sharing, migratory

sharing, and producer-consumer sharing. For wide sharing, instruction-based prediction compares favorably to static identification and to two novel dynamic address-based identification schemes. For migratory sharing, instruction-based prediction matches or exceeds the performance of previously proposed adaptive protocols (for seven benchmark programs). For producer-consumer sharing, instruction-based prediction is coupled with *speculative pre-send*—a novel optimization based on speculative execution. The low mis-speculation rates of this scheme show promise for performance improvements.

#### **Acknowledgments**

I dedicate this thesis to the memory of my father Vasileios, my mother Ekaterini and my beloved partner Angeliki. The love of my mother, my brother Efthimios, my sister Eleni and her family, as well as Angeliki's family kept us going through graduate school.

I would like to thank my advisor and mentor, professor James R. Goodman for supporting me. I am grateful to professor David A. Wood for his insight, professor Gurindar S. Sohi for his support, and professor Mark D. Hill for his help. Their sound advice helped me to complete my Ph.D.

Also, I would like to thank all my friends and colleagues at the University of Wisconsin, especially Scott Breach, Doug Burger, Babak Falsafi, Alain Kägi, Andreas Moshovos, Shubu Mukherjee, Dionisios Pnevmaticatos, Yannis Schoinas, and T.N. Vijaykumar for the many technical conversations, assistance, and advice. My thanks to Todd Bezenek who has proofread an entire version of this thesis. All remaining errors are solely my responsibility.

This work was supported in part by NSF Grants CCR-9207971 and CCR-9509589, funding from the Apple Computer Advanced Technology Group, an unrestricted grant from the Intel Research Council, and equipment donations from Sun Microsystems. Our Thinking Machines CM-5 was purchased through NSF Institutional Infrastructure Grant No. CDA-9024618, with matching funding from the University of Wisconsin Graduate School. This work was also partially supported by the National Center for Supercomputing Applications and utilized the Thinking Machines CM-5 at NCSA, University of Illinois at Urbana-Champaign.

## **Table of Contents**

| Abstract     |                                                                                                                                     | i                                |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Acknowled    | gments                                                                                                                              | iii                              |

| Table of Co  | ontents                                                                                                                             | iv                               |

| List of Figu | ires                                                                                                                                | viii                             |

| List of Tab  | les                                                                                                                                 | xiii                             |

| Chapter 1    | Introduction                                                                                                                        | 1                                |

| 1.1          | Sharing patterns and optimizations                                                                                                  | 4<br>4                           |

| 1.2          | Identification of sharing patterns                                                                                                  | 9<br>10<br>10                    |

| 1.3          | Contributions                                                                                                                       |                                  |

| 1.4          | Thesis roadmap                                                                                                                      | 17                               |

| Chapter 2    | Evaluation Methodology                                                                                                              | 19                               |

| 2.1          | Wisconsin Wind Tunnel                                                                                                               | 20                               |

| 2.2          | Network                                                                                                                             | 23                               |

| 2.3          | Benchmarks  2.3.1 GAUSS  2.3.2 SPARSE  2.3.3 APSP, TC  2.3.4 CG  2.3.5 BARNES  2.3.6 CHOLESKY  2.3.7 MP3D  2.3.8 PTHOR  2.3.9 OCEAN | 27<br>28<br>29<br>29<br>30<br>31 |

| Chapter 3    | Wide Sharing                                                                                                                        |                                  |

| 3.1          | Widely-shared data                                                                                                                  |                                  |

| 3.2<br>3.3   | The idea behind GLOW: exploit redundancy of widely-shared data  Related work                                                        |                                  |

|              | 3.3.1 Sharing trees                                                                                                                 | 40                               |

|           |        |                                                            | v   |

|-----------|--------|------------------------------------------------------------|-----|

|           |        | 3.3.1.1 STEM kiloprocessor extensions to SCI               | 41  |

|           |        | 3.3.1.2 STP and TD                                         |     |

|           | 3.3.2  | Request combining                                          | 47  |

|           | 3.3.3  | Caching in the network                                     | 48  |

|           |        | Hierarchical directories                                   |     |

| 3.4       | GLOW   |                                                            | 51  |

|           |        | GLOW features                                              |     |

|           |        | An overview of the GLOW extensions                         |     |

| 3.5       | GLOW o | on SCI                                                     | 56  |

|           |        | SCI GLOW Agents                                            |     |

|           |        | Creation of sharing trees                                  |     |

|           |        | Multilevel inclusion                                       |     |

|           |        | Invalidation of sharing trees                              |     |

|           |        | Latency of reads and writes                                |     |

|           |        | Replacements in sharing trees                              |     |

|           |        | Replacements and GLOW cache size                           |     |

|           |        | Update of sharing trees                                    |     |

| 3.6       | Memor  | y consistency and GLOW                                     | 88  |

|           | •      | Memory models                                              |     |

|           |        | GLOW and relaxed memory models                             |     |

|           |        | Update protocols and memory models                         |     |

| 3.7       |        | ossible GLOW implementations                               |     |

| 3.7       |        | Full-map directory protocols                               |     |

|           |        | 3.7.1.1 The agent addressing problem in full-map protocols |     |

|           |        | 3.7.1.2 A sample GLOW design for Dir <sub>n</sub> NB       |     |

|           |        | 3.7.1.3 Summary of GLOW on Dir <sub>n</sub> NB             |     |

|           |        | Limited pointer directory protocols                        |     |

|           |        | GLOW and pruning caches                                    |     |

|           |        | Software GLOW (SOFTGLOW)                                   |     |

|           |        | 3.7.4.1 SOFTGLOW and software combining                    |     |

|           |        | 3.7.4.2 Related work                                       |     |

| 3.8       | Summa  | ry                                                         | 108 |

| Chapter 4 |        | and Dynamic Optimizations for Wide Sharing                 |     |

| 4.1       |        | ptimizations for wide sharing                              |     |

|           |        | Static address-based GLOW                                  |     |

|           |        | Static instruction-based GLOW                              |     |

| 4.2       |        | nance of static optimizations                              |     |

| 7.2       |        | Basic performance: GLOW with and without data cache        |     |

|           |        | Dataset                                                    |     |

|           |        | Analysis of read and write performance                     |     |

|           |        | Relaxed consistency                                        |     |

|           |        | Update protocol                                            |     |

| 4.3       |        |                                                            |     |

| 4.3       | Dynaim | ic address-based optimizations for wide sharing            | 134 |

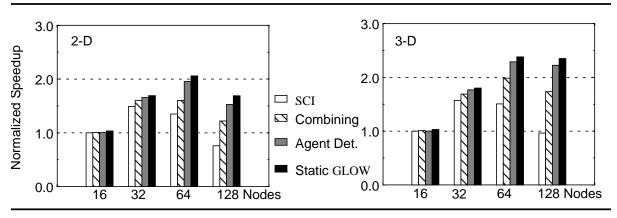

|           | 4.3.1 Congestion-based detection of widely-shared data             | 135  |

|-----------|--------------------------------------------------------------------|------|

|           | 4.3.1.1 Request-combining in GLOW                                  | 135  |

|           | 4.3.1.2 AGENT DETECTION of widely-shared data                      | 136  |

|           | 4.3.1.3 Performance of congestion-based optimizations              | 138  |

|           | 4.3.2 DIRECTORY DETECTION of widely-shared data                    | 144  |

|           | 4.3.2.1 Adapting back                                              | 148  |

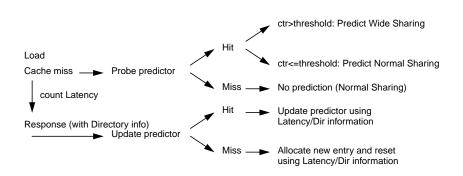

| 4.4       | Dynamic instruction-based optimizations for wide sharing           | 152  |

|           | 4.4.1 Latency                                                      | 154  |

|           | 4.4.2 Directory feedback                                           | 155  |

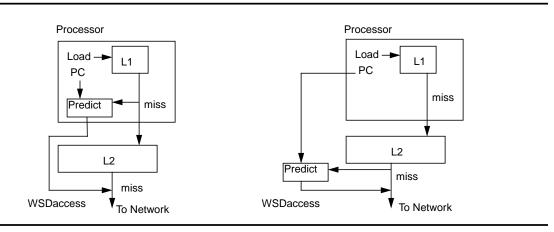

|           | 4.4.3 Implementation issues                                        | 157  |

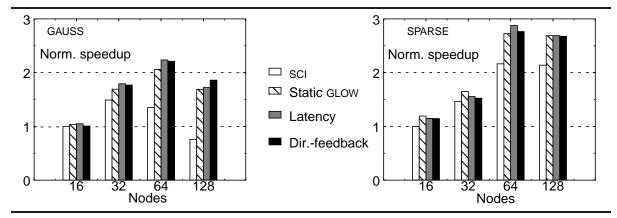

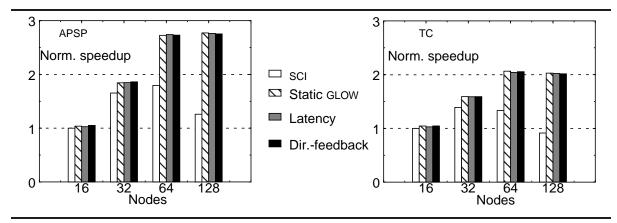

|           | 4.4.4 Results                                                      |      |

|           | 4.4.5 Static instruction-based optimizations for widely-shared dat | a160 |

| 4.5       | Performance comparisons and read-run analysis                      | 163  |

| 4.6       | Summary                                                            | 174  |

| Chapter 5 | Migratory Sharing                                                  | 177  |

| 5.1       | Address-based optimizations for migratory sharing                  | 181  |

| 5.2       | Instruction-based optimizations for migratory sharing              | 183  |

|           | 5.2.1 QOLB                                                         | 183  |

|           | 5.2.2 Static instruction-based optimizations                       | 183  |

|           | 5.2.3 Dynamic instruction-based optimizations                      |      |

|           | 5.2.4 Cache-block anti-dependence prediction                       |      |

|           | 5.2.5 Migratory sharing optimization on SCI                        | 192  |

|           | 5.2.6 Results                                                      | 194  |

| 5.3       | Summary                                                            | 197  |

| Chapter 6 | Producer-Consumer Sharing                                          | 199  |

| 6.1       | Related work                                                       | 201  |

|           | 6.1.1 Address-based optimizations                                  | 201  |

|           | 6.1.2 Instruction-based optimizations                              | 201  |

| 6.2       | Dynamic instruction-based optimizations                            | 203  |

|           | 6.2.1 Pairwise-sharing prediction                                  |      |

|           | 6.2.2 Producer-consumer prediction with                            |      |

|           | speculative-execution optimization                                 | 204  |

|           | 6.2.3 In search of the consumers                                   | 205  |

|           | 6.2.4 Prediction                                                   | 206  |

|           | 6.2.5 A novel optimization: speculative pre-send                   | 208  |

|           | 6.2.6 How can a processor read external speculative data?          | 209  |

|           | 6.2.7 Results                                                      | 211  |

| 6.3       | Predictor interactions                                             | 216  |

| 6.4       | Summary                                                            | 218  |

| Chapter 7 | Summary and Future Directions                                      | 219  |

| 7.1       | The GLOW optimization for wide sharing                             | 220  |

| 7.2         | Instruction-based prediction                    | 222 |

|-------------|-------------------------------------------------|-----|

| 7.3         | Future directions                               | 224 |

| References  |                                                 | 227 |

| Appendix 1  | SCI Cache Coherence                             | 237 |

| Appendix 2  | Enhancements for the Construction of GLOW Trees | 243 |

| Appendix 3: | : Critical Section Detection                    | 245 |

# **List of Figures**

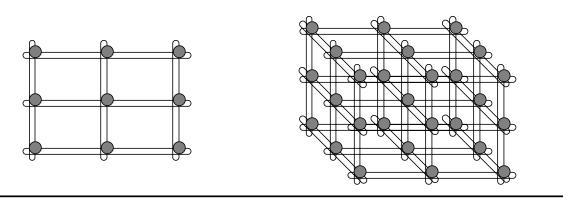

| Figure 2.1.  | 2-dimensional and 3-dimensional networks made of SCI rings           | 22 |

|--------------|----------------------------------------------------------------------|----|

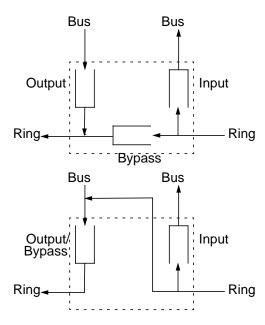

| Figure 2.2.  | SCI ring interface assumptions.                                      | 24 |

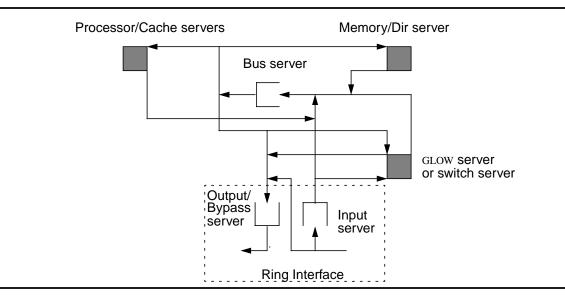

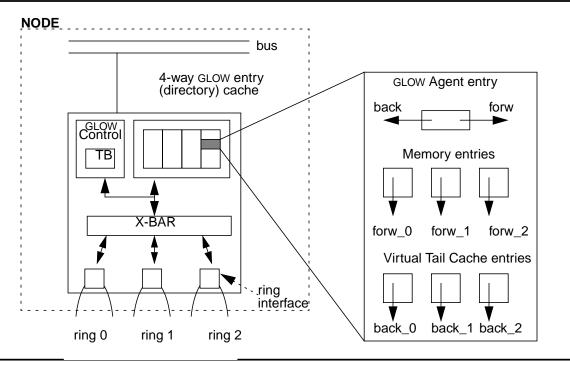

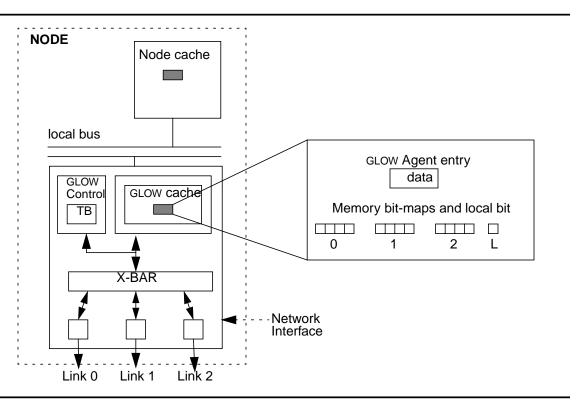

| Figure 2.3.  | Queueing in a node (only one ring interface shown for clarity).      |    |

|              | The GLOW server is close to the ring interface and does not          |    |

|              | have to go through the bus to communicate with other nodes.          |    |

|              | This is because the GLOW server represents the switch that           |    |

|              | connects multiple ring interfaces together and transfers messages    |    |

|              | from one to the other                                                | 24 |

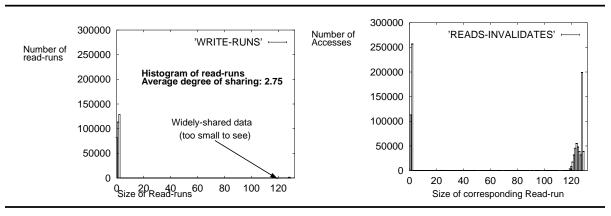

| Figure 3.1.  | Read-run histogram and corresponding Reads/Invalidations             |    |

|              | for GAUSS running in 128 nodes.                                      | 35 |

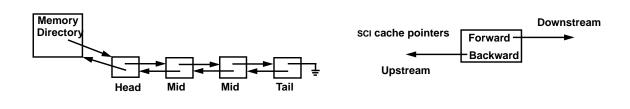

| Figure 3.2.  | STEM cache pointers                                                  | 42 |

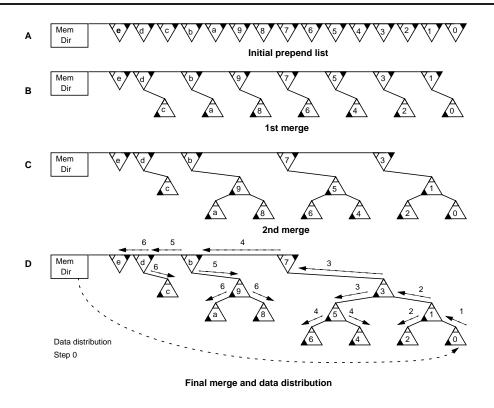

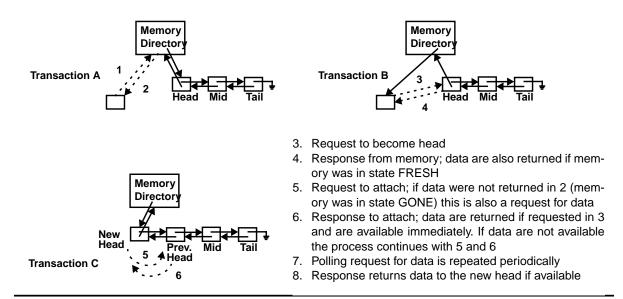

| Figure 3.3.  | STEM sharing tree construction.                                      | 43 |

| Figure 3.4.  | STEM sharing tree invalidation.                                      | 45 |

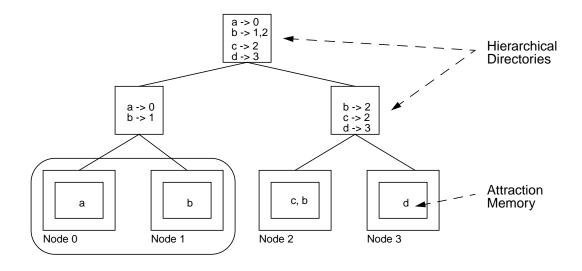

| Figure 3.5.  | COMA architectures. A request for non-local data traverses           |    |

|              | the hierarchical directories until it locates a directory entry      |    |

|              | that specifies the location of the data. For example, when           |    |

|              | node 0 requests data block "b" it will find it in its immediate      |    |

|              | vicinity; when it requests data block "d" it has to ascend to        |    |

|              | the root of the hierarchical directory structure to find the data    |    |

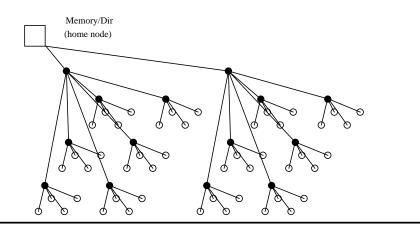

|              | block in the remote node 3.                                          | 49 |

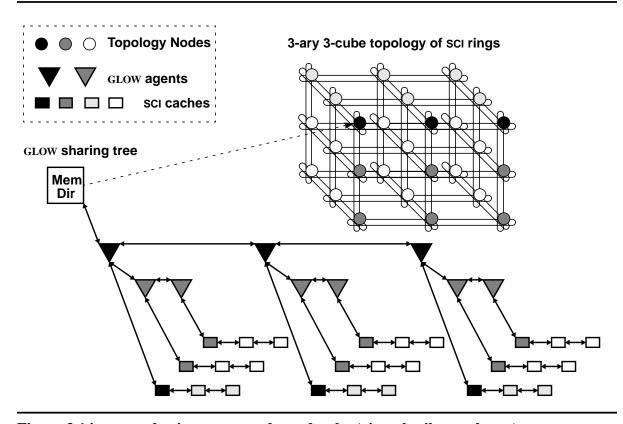

| Figure 3.6.  | Logical k-ary sharing tree. Black nodes are GLOW agents,             |    |

|              | white nodes are sharing nodes.                                       | 55 |

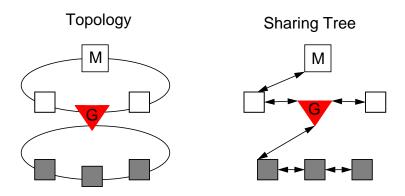

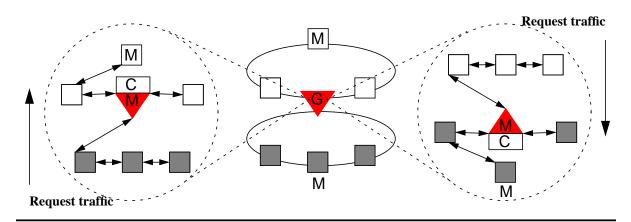

| Figure 3.7.  | A GLOW agent in a 2-ring SCI system.                                 | 57 |

| Figure 3.8.  | The behavior of a GLOW agent is independent of topological           |    |

|              | information; it depends only on the direction of the request traffic | 58 |

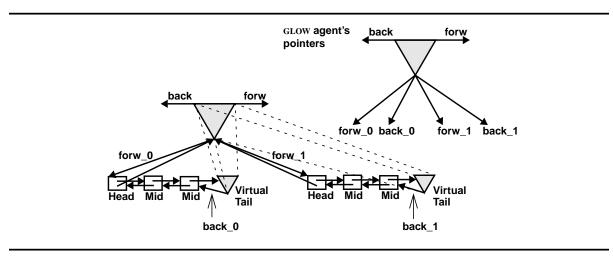

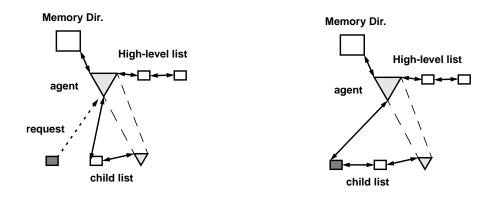

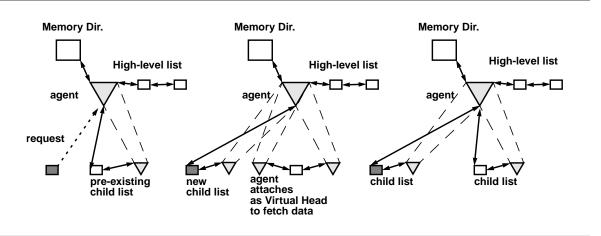

| Figure 3.9.  | Schematic representation of a GLOW agent holding 2 child lists       | 59 |

| Figure 3.10. | Internals of a GLOW agent. The right scheme is a representation      |    |

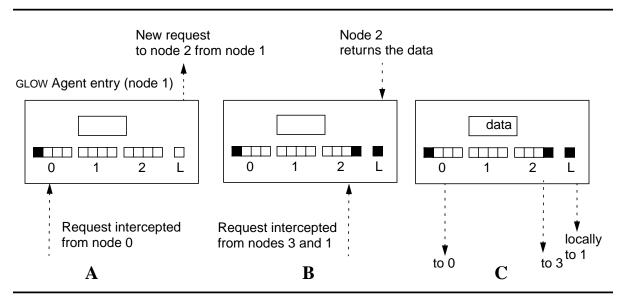

|              | of an uncompressed GLOW entry in the directory cache                 | 60 |

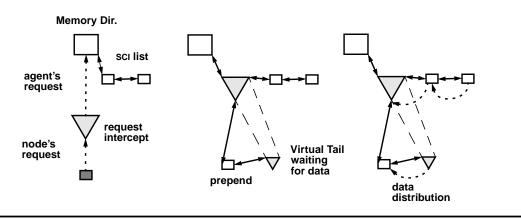

| Figure 3.11. | GLOW agent intercepts node's request and generates its own           |    |

|              | request (miss in the agent's directory)                              | 62 |

| Figure 3.12. | Hit in agent; node joins a pre-existing child list                   | 63 |

| Figure 3.13. | Hit in agent, node joins a new child list.                           | 63 |

| Figure 3.14. | GLOW sharing tree on a 3-ary 3-cube (virtual tails not shown)        | 65 |

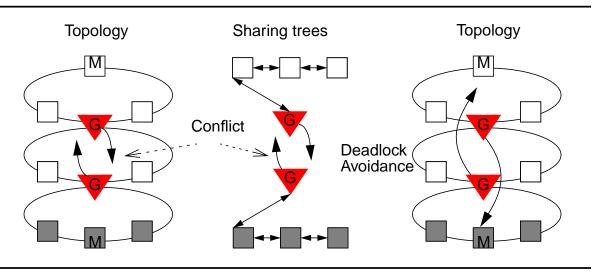

| Figure 3.15.  | Deadlock! Two expanding sharing trees (shown in the middle)          |     |

|---------------|----------------------------------------------------------------------|-----|

| _             | conflict in a pair of GLOW agents (topology shown in the left).      |     |

|               | Each tree needs the GLOW entry of the other tree to continue         |     |

|               | building toward its target home node memory directory.               |     |

|               | To break the deadlock each agent ignores the request of the          |     |

|               | other agent and passes it toward its destination                     |     |

|               | (shown in the right)                                                 | 66  |

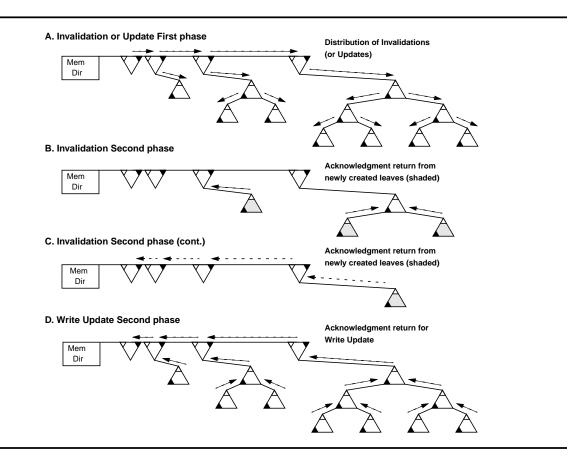

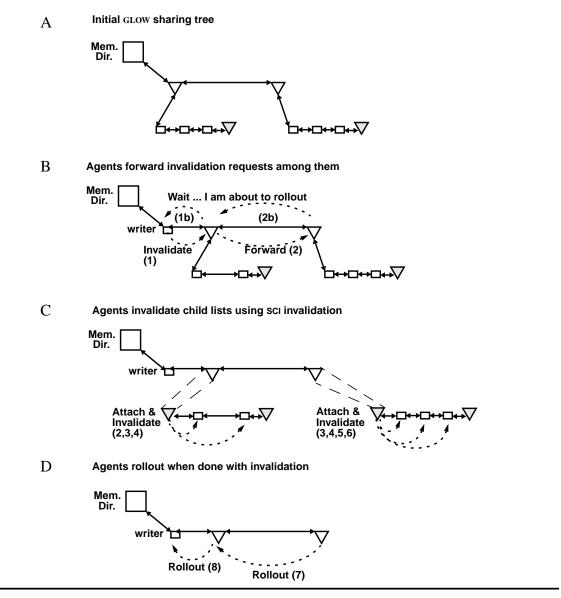

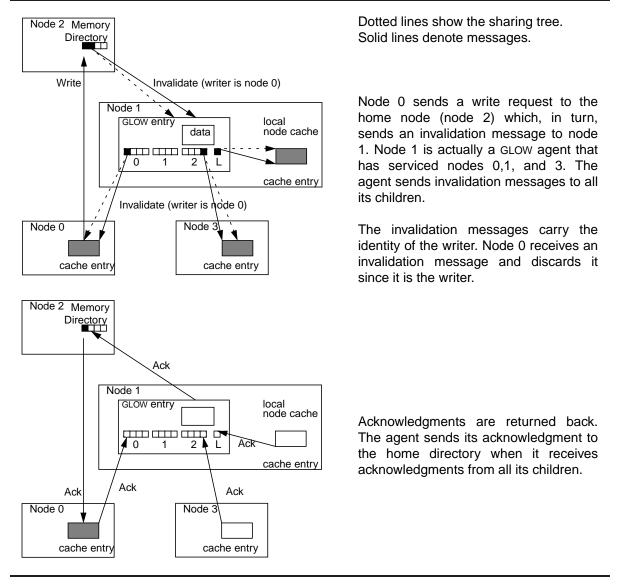

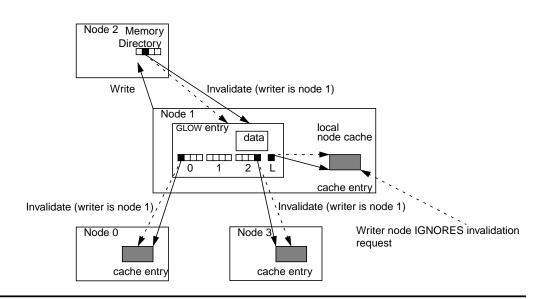

| Figure 3.16.  | Invalidation of a GLOW sharing tree                                  |     |

| Figure 3.17.  | Read latency micro-benchmark results in 2-dimensional topologies     |     |

| Figure 3.18.  | Read latency micro-benchmark results in 3-dimensional topologies     |     |

| Figure 3.19.  | Write latency results in 2-dimensional topologies.                   |     |

| Figure 3.20.  | Write latency results in 3-dimensional topologies.                   |     |

| Figure 3.21.  | Micro-benchmark for writes.                                          |     |

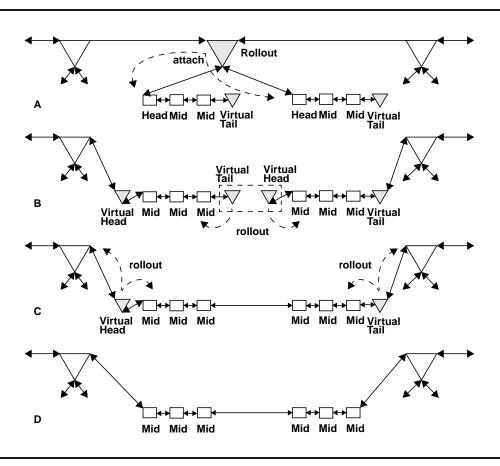

| Figure 3.22.  | LINEARIZING ROLLOUT                                                  | 80  |

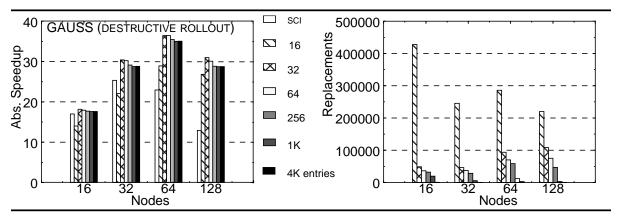

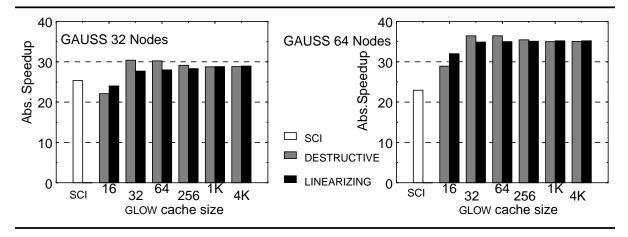

| Figure 3.23.  | Sensitivity to directory cache size for GAUSS                        | 82  |

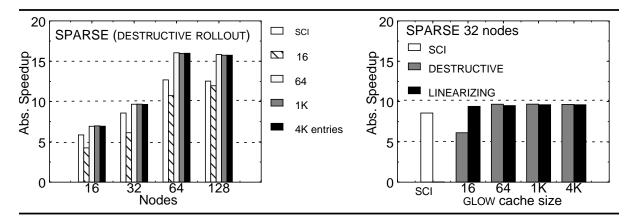

| Figure 3.24.  | DESTRUCTIVE vs. LINEARIZING ROLLOUT for GAUSS                        |     |

| Figure 3.25.  | Sensitivity to directory cache size for SPARSE                       | 83  |

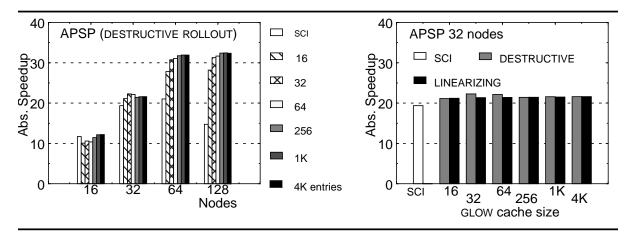

| Figure 3.26.  | Sensitivity to directory cache size for APSP                         |     |

| Figure 3.27.  | Internals of a GLOW agent in a Dir <sub>n</sub> NB-based system.     |     |

| C             | The right scheme is a representation of a GLOW entry in the          |     |

|               | directory cache.                                                     | 95  |

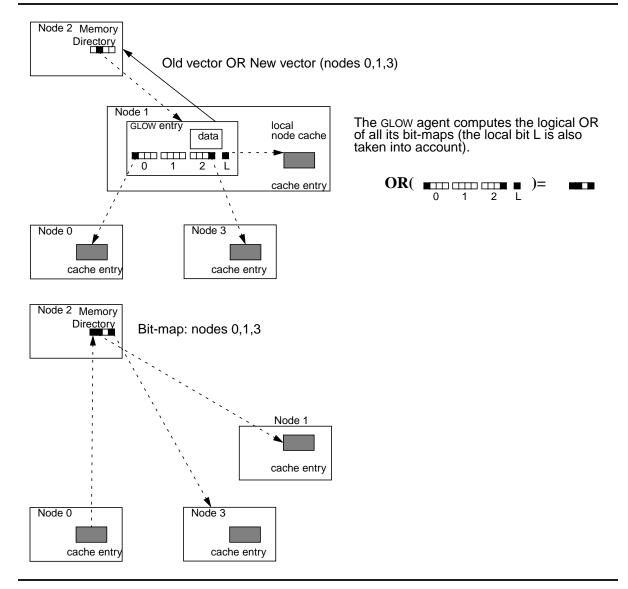

| Figure 3.28.  | Hypothetical example of a four node system. A GLOW agent             |     |

| 8             | assumes the identity of node 1 for widely-shared data and            |     |

|               | intercepts requests from nodes 0 and 3 as well as locally            |     |

|               | from node 1                                                          | 97  |

| Figure 3.29.  | Invalidation of a GLOW sharing tree in a Dir <sub>n</sub> NB system. |     |

| C             | The hypothetical four node example of figure (3.28) is used          | 98  |

| Figure 3.30.  | Invalidation message returns to the writer node which is             |     |

| 1180110 01001 | also a GLOW agent                                                    | 99  |

| Figure 3.31.  | Replacement of a GLOW agent in a Dir <sub>n</sub> NB system.         |     |

| C             | The hypothetical four node example of figure (3.28) is used          | 100 |

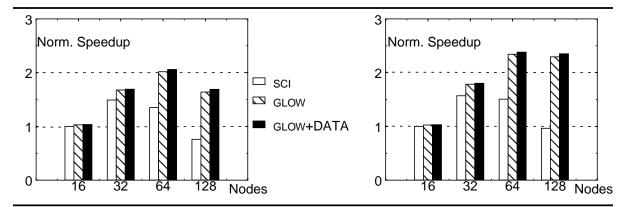

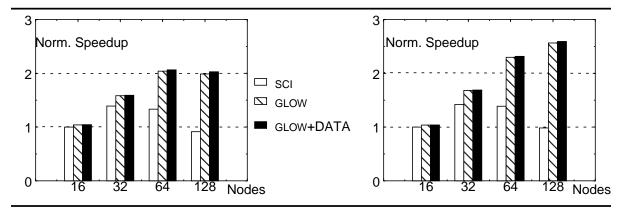

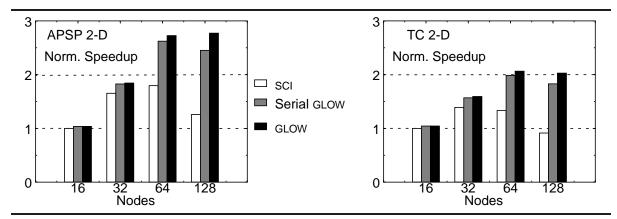

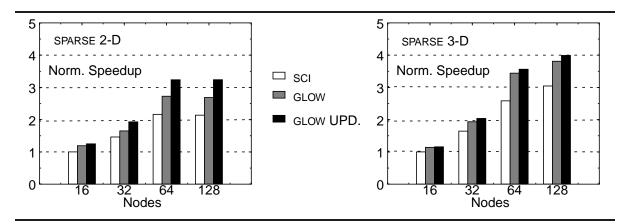

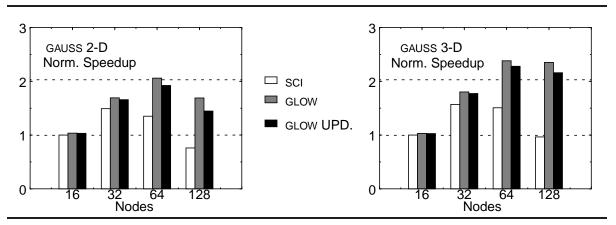

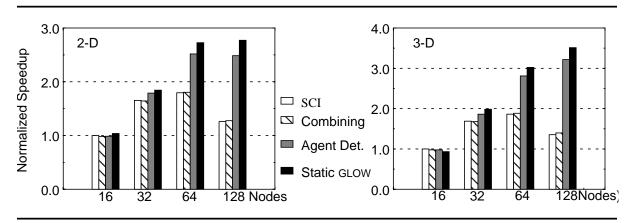

| Figure 4.1.   | GAUSS: Normalized speedup (base system is SCI on 16 nodes)           | 100 |

| 1.80.10       | for 2- and 3- dimensional networks. GLOW with and without            |     |

|               | data cache.                                                          | 121 |

| Figure 4.2.   | SPARSE: Normalized speedup (base system is SCI on 16 nodes)          | 121 |

| .6            | for 2- and 3- dimensional networks. GLOW with and without            |     |

|               | data cache.                                                          | 122 |

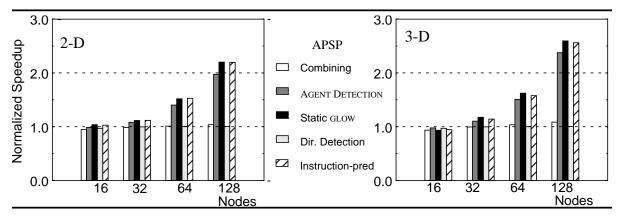

| Figure 4.3.  | APSP: Normalized speedup (base system is SCI on 16 nodes)        |    |

|--------------|------------------------------------------------------------------|----|

|              | for 2- and 3- dimensional networks. GLOW with and without        |    |

|              | data cache 1                                                     | 22 |

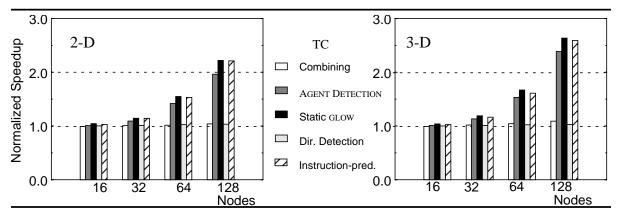

| Figure 4.4.  | TC: Normalized speedup (base system is SCI on 16 nodes)          |    |

|              | for 2- and 3- dimensional networks. GLOW with and without        |    |

|              | data cache 1                                                     | 22 |

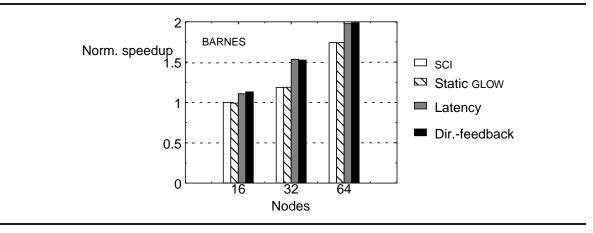

| Figure 4.5.  | BARNES: Normalized speedup (base system is SCI on 16 nodes)      |    |

|              | for 2- and 3- dimensional networks.                              |    |

|              | GLOW with and without data cache                                 | 23 |

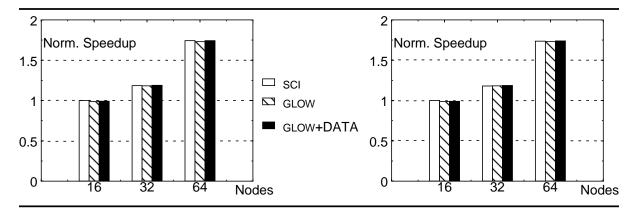

| Figure 4.6.  | CG: Normalized speedup (base system is SCI on 16 nodes)          |    |

|              | for 2-dimensional network. GLOW with and without data cache 1    | 23 |

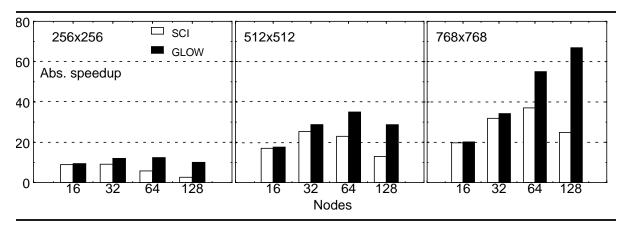

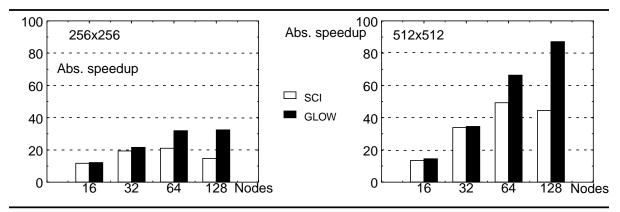

| Figure 4.7.  | Absolute speedup (over a single node) for GAUSS in 2 dimensions  |    |

|              | with three input set sizes: 256x256, 512x512, 768x768            | 25 |

| Figure 4.8.  | Absolute speedup (over a single node) for APSP in                |    |

|              | 2 dimensions with two input set sizes: 256x256 and 512x512       | 25 |

| Figure 4.9.  | Absolute speedup (over a single node) for TC in                  |    |

|              | 2 dimensions with two input set sizes: 256x256 and 512x512       | 26 |

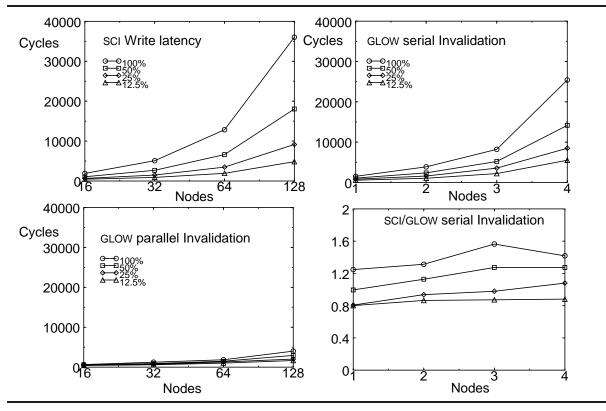

| Figure 4.10. | Write latency micro-benchmark results for GLOW with              |    |

| C            | serial invalidation                                              | 28 |

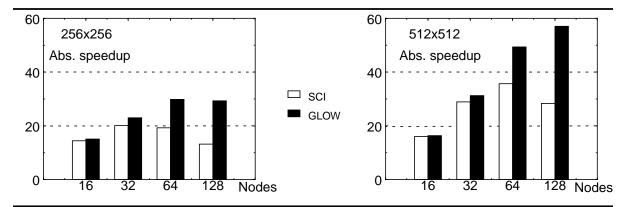

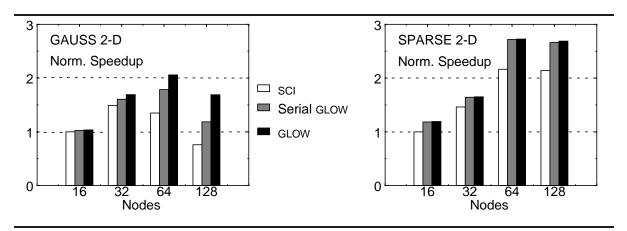

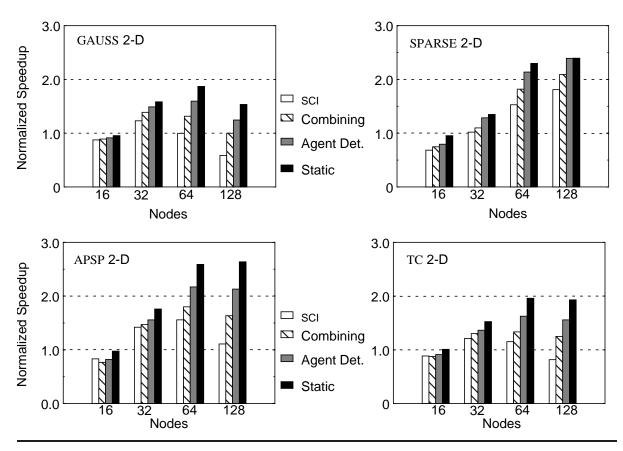

| Figure 4.11. | Normalized speedup for GAUSS and SPARSE with serial GLOW.        |    |

|              | Base system is SCI on 16 nodes                                   | 28 |

| Figure 4.12. | Normalized speedup for APSP and TC with serial GLOW.             |    |

|              | Base system is SCI on 16 nodes                                   | 29 |

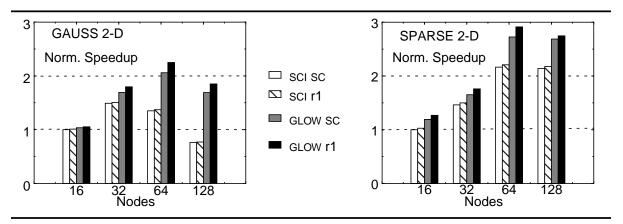

| Figure 4.13. | Normalized speedup for GAUSS and SPARSE with relaxed-consistency |    |

|              | memory model. Base system is SCI on 16 nodes                     | 30 |

| Figure 4.14. | Normalized speedup for APSP and TC with relaxed-consistency      |    |

|              | memory model. Base system is SCI on 16 nodes                     | 31 |

| Figure 4.15. | Normalized speedup for BARNES with relaxed-consistency           |    |

|              | memory model. Base system is SCI on 16 nodes,                    | 31 |

| Figure 4.16. | Normalized speedup for full update in SPARSE.                    |    |

|              | Base system is SCI on 16 nodes                                   | 33 |

| Figure 4.17. | Normalized speedup for full update in GAUSS.                     |    |

|              | Base system is SCI on 16 nodes                                   | 33 |

| Figure 4.18. | Speedup for GAUSS (with respect to SCI on 16 nodes)              |    |

|              | in 2 and 3 dimensions (16 to 128 nodes)                          | 39 |

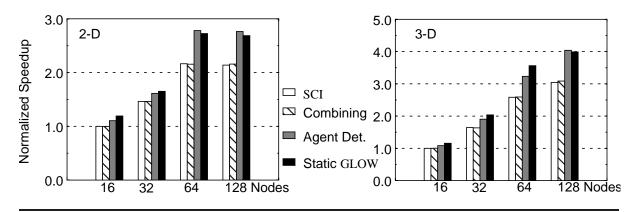

| Figure 4.19. | Speedup for SPARSE (with respect to SCI on 16 nodes)             |    |

|              | in 2 and 3 dimensions (16 to 128 nodes)                          | 40 |

| Figure 4.20. | Speedup for APSP (with respect to SCI on 16 nodes)               |    |

|              | in 2 and 3 dimensions (16 to 128 nodes)                          | 40 |

| Figure 4.21. | Speedup for TC (with respect to SCI on 16 nodes)                |     |

|--------------|-----------------------------------------------------------------|-----|

|              | in 2 and 3 dimensions (16 to 128 nodes).                        | 140 |

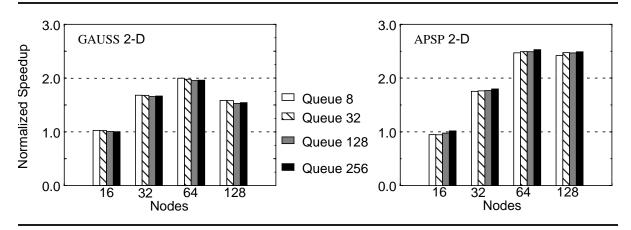

| Figure 4.22. | Sensitivity analysis for the size of the recent-addresses queue |     |

|              | (speedup of AGENT DETECTION with respect to SCI on 16 nodes)    | 141 |

| Figure 4.23. | Speedup results with slower switches. Contention in the switch  |     |

|              | nodes makes ordinary combining competitive but it also slows    |     |

|              | down the whole system. Speedups for SCI, combining, dynamic     |     |

|              | and static GLOW are shown with respect to SCI on 16 nodes       |     |

|              | with fast switches.                                             | 143 |

| Figure 4.24. | Instruction-based prediction for wide sharing                   | 153 |

| Figure 4.25. | Datapaths for the prediction mechanisms                         |     |

| C            | (according to its location)                                     | 157 |

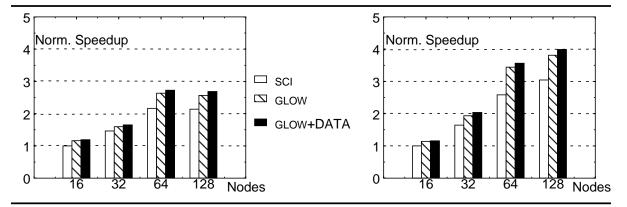

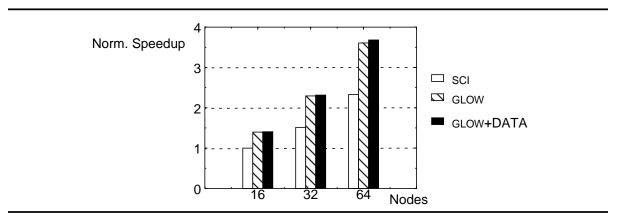

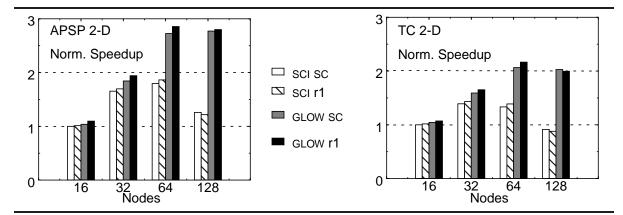

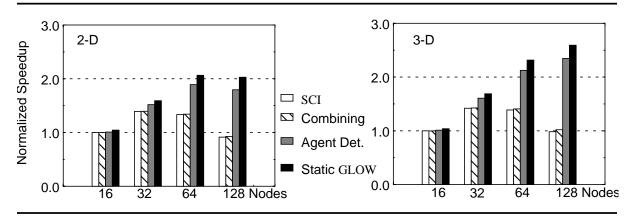

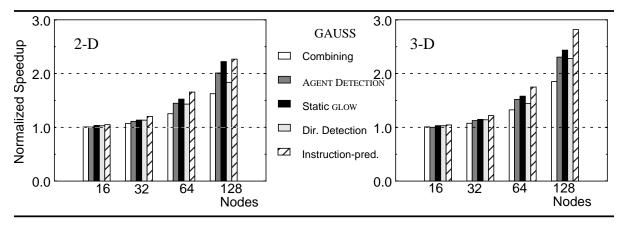

| Figure 4.26. | Comparison of SCI, static GLOW, and the two dynamic             |     |

|              | instruction-based schemes for GAUSS and SPARSE.                 |     |

|              | Base system is SCI on 16 nodes.                                 | 161 |

| Figure 4.27. | Comparison of SCI, static GLOW, and the two dynamic             |     |

|              | instruction-based schemes for APSP and TC.                      |     |

|              | Base system is SCI on 16 nodes.                                 | 161 |

| Figure 4.28. | Comparison of SCI, static GLOW, and the two dynamic             |     |

|              | instruction-based schemes for BARNES.                           |     |

|              | Base system is SCI on 16 nodes.                                 | 161 |

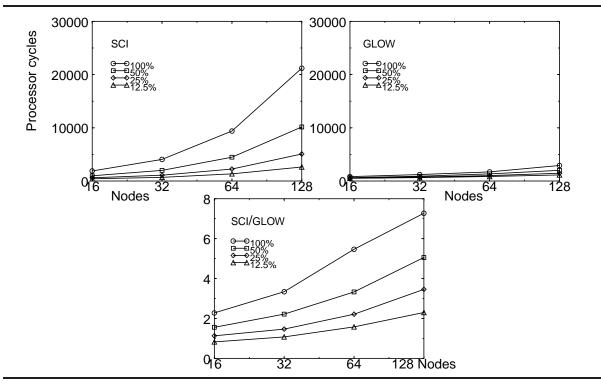

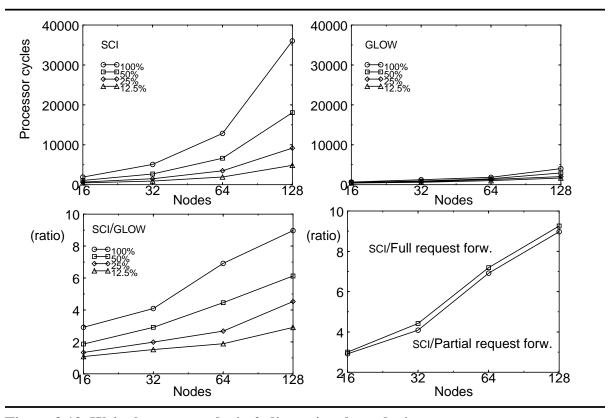

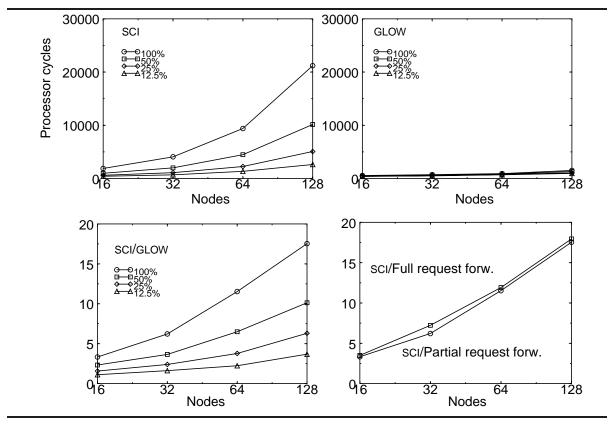

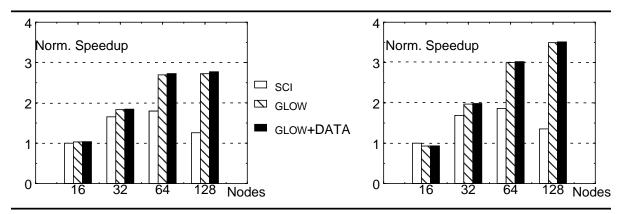

| Figure 4.29. | Normalized speedup (over SCI) for GAUSS in 2 and 3              |     |

|              | dimensions (16 to 128 nodes)                                    | 164 |

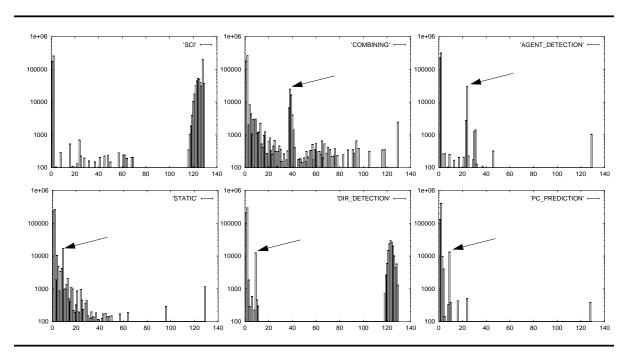

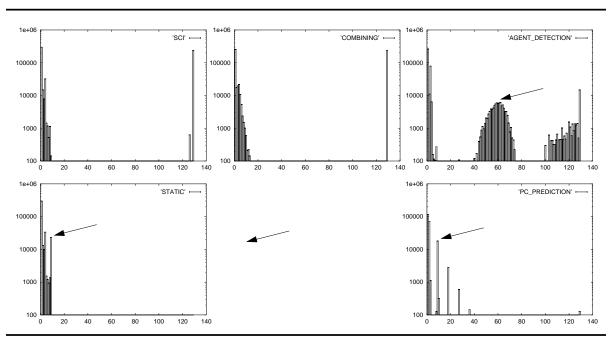

| Figure 4.30. | Read-run compression for GAUSS (128 nodes 2-dimensions).        |     |

|              | Accesses corresponding to large read-runs are shifted toward    |     |

|              | smaller read-runs using GLOW extensions.                        | 165 |

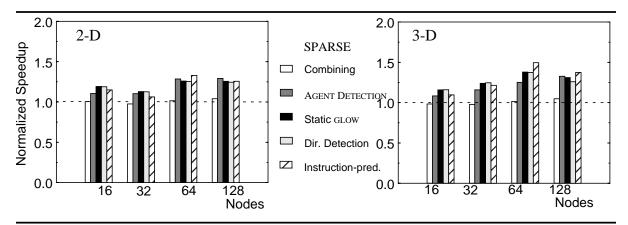

| Figure 4.31. | Normalized speedup (over SCI) for SPARSE in 2 and 3             |     |

|              | dimensions (16 to 128 nodes)                                    | 167 |

| Figure 4.32. | Compression of read-runs for SPARSE (128 nodes, 2 dimensions).  |     |

|              | Accesses corresponding to large read-runs are shifted toward    |     |

|              | smaller read-runs using GLOW extensions.                        | 167 |

| Figure 4.33. | Normalized speedup (over SCI) for APSP for 2 and 3              |     |

|              | dimensions (16 to 128 nodes)                                    | 168 |

| Figure 4.34. | Normalized speedup (over SCI) for TC in 2 and 3                 |     |

|              | dimensions (16 to 128 nodes)                                    | 168 |

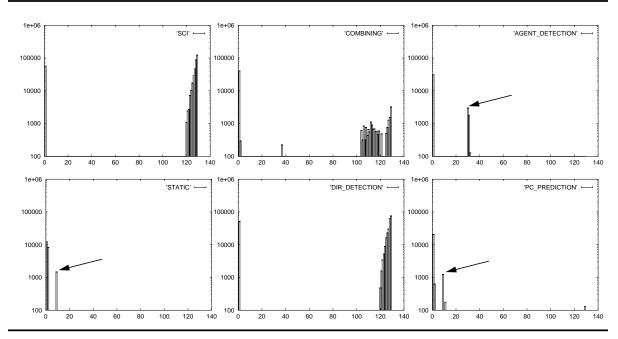

| Figure 4.35. | Read-run compression for APSP (128 nodes, 2 dimensions).        |     |

| _            | Accesses corresponding to large read-runs are shifted toward    |     |

|              | smaller read-runs using GLOW extensions.                        | 169 |

|              |                                                                 |     |

|           | ٠ | ٠ |

|-----------|---|---|

| v         | 1 | 1 |

| $\Lambda$ | 1 | 1 |

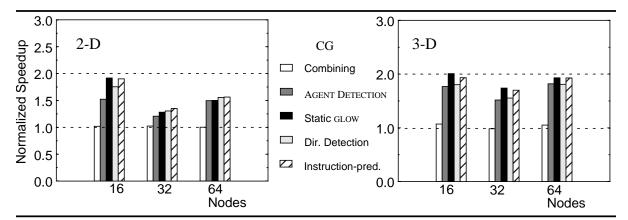

| Figure 4.36. | Normalized speedup (over SCI) for CG in 2 and 3                   |     |

|--------------|-------------------------------------------------------------------|-----|

|              | dimensions (16 to 64 nodes)                                       | 170 |

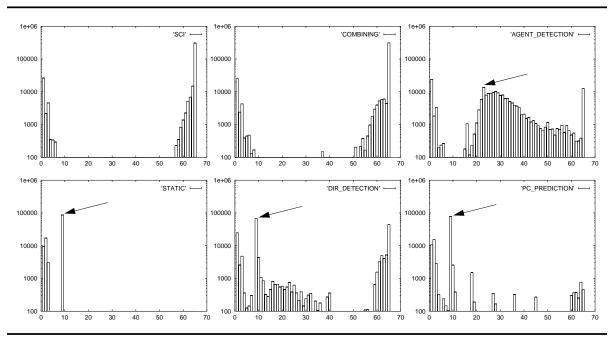

| Figure 4.37. | Read-run compression for CG (64 nodes, 2 dimensions).             |     |

|              | Accesses corresponding to large read-runs are shifted toward      |     |

|              | smaller read-runs using GLOW extensions.                          | 170 |

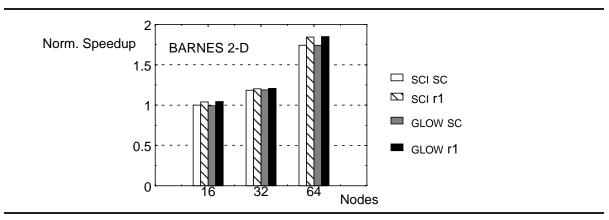

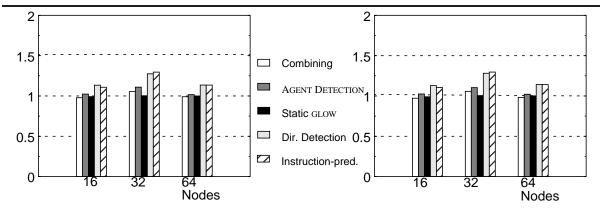

| Figure 4.38. | Normalized speedup (over SCI) for BARNES for 2 and 3              |     |

|              | dimensions (16 to 128 nodes)                                      | 171 |

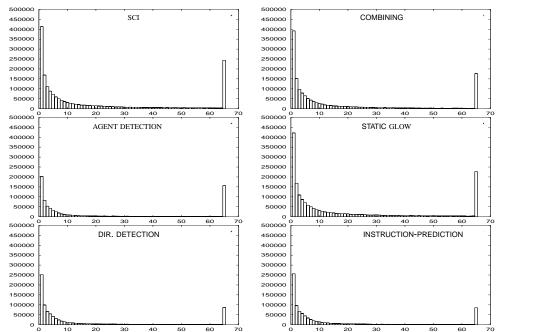

| Figure 4.39. | Read-run compression for BARNES (64 nodes, 2 dimensions).         |     |

|              | Y-axis (no. of accesses) <i>not</i> in logarithmic scale          | 172 |

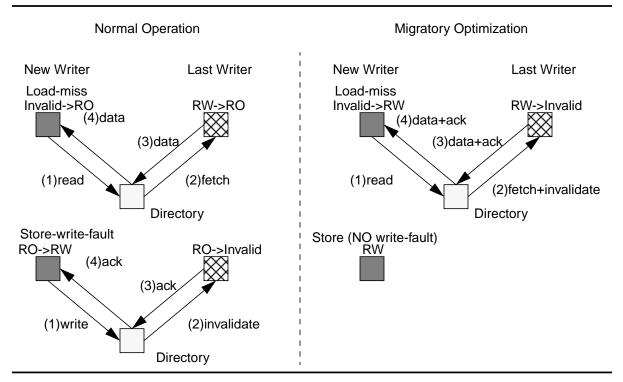

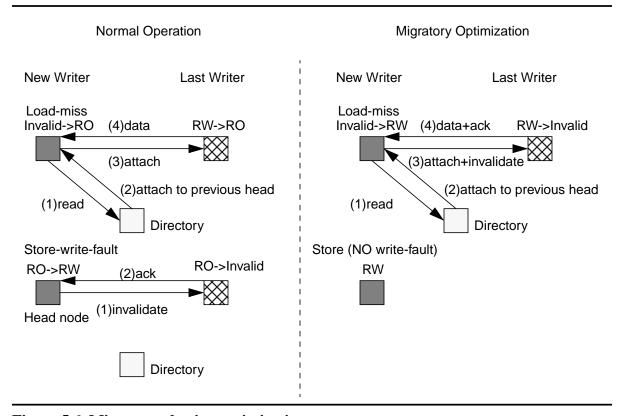

| Figure 5.1.  | Migratory sharing optimization.                                   | 178 |

| Figure 5.2.  | Typical critical sections in MP3D and OCEAN.                      | 184 |

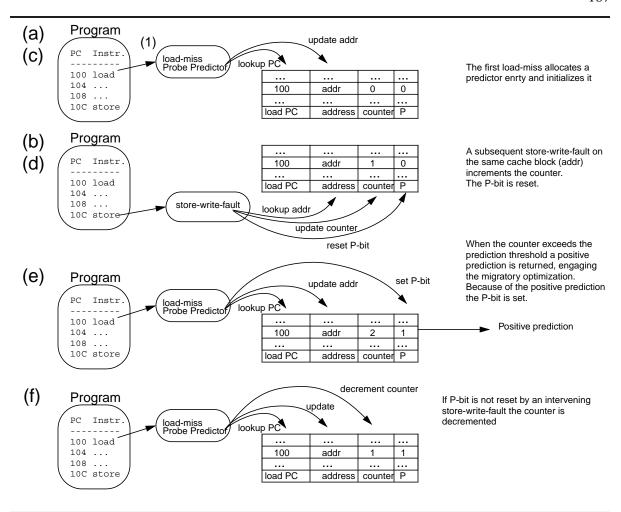

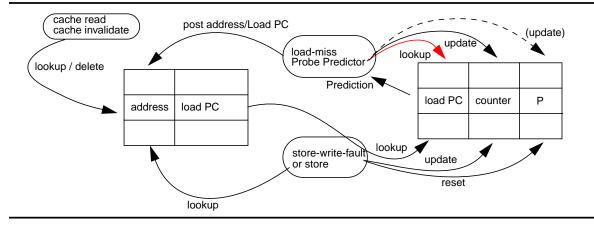

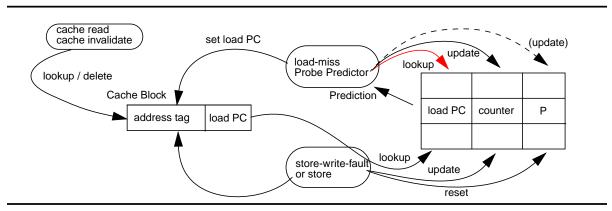

| Figure 5.3.  | Cache block anti-dependence prediction mechanism                  | 187 |

| Figure 5.4.  | Alternative implementation for the prediction mechanism:          |     |

|              | Correspondence of a load and a store is established               |     |

|              | via an external structure                                         | 190 |

| Figure 5.5.  | Alternative implementation for the prediction mechanism:          |     |

| _            | Correspondence of a load and a store is established               |     |

|              | via the cache block.                                              | 190 |

| Figure 5.6.  | Migratory sharing optimization on SCI                             | 193 |

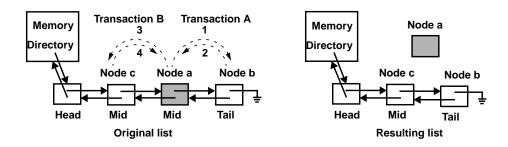

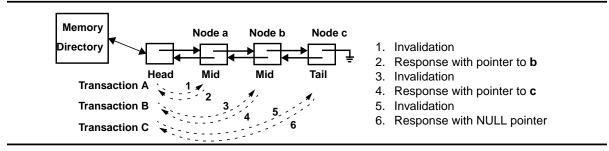

| Figure 8.1.  | SCI sharing list.                                                 |     |

| Figure 8.2.  | Creation of a sharing list                                        |     |

| Figure 8.3.  | Additions to a SCI sharing list                                   |     |

| Figure 8.4.  | SCI cache rollout.                                                |     |

| Figure 8.5.  | SCI sharing list invalidation                                     | 241 |

| Figure 8.6.  | Example of an MP3D critical section with migratory data.          |     |

| C            | Entry is through a number of different synchronization algorithms |     |

|              | based on different atomic/synchronization primitives: Swap,       |     |

|              | Test&Swap, and QOLB. The MCS algorithm is implemented using       |     |

|              | Test&Swap. The USE_WITH algorithm is based on QOLB.               |     |

|              | Special writes (implementing memory fences) or the QOLB release   |     |

|              | primitive are used to exit the critical section.                  | 246 |

|              |                                                                   |     |

## **List of Tables**

| Table 1.  | Techniques to identify a sharing pattern                           | 9   |

|-----------|--------------------------------------------------------------------|-----|

| Table 2.  | Previously proposed identification techniques for three sharing    |     |

|           | patterns (shaded cells).                                           | 15  |

| Table 3.  | Identification techniques proposed in this thesis                  | 16  |

| Table 4.  | Benchmarks used in this work. For each benchmark, the input size,  |     |

|           | the cache and block size, and prominent sharing patterns are       |     |

|           | described. The references point to papers where the benchmarks are |     |

|           | described or used in the same way as in this work                  | 26  |

| Table 5.  | Wide sharing: static and dynamic, address-based and                |     |

|           | instruction-based methods to apply the GLOW optimizations.         |     |

|           | Related work is shown in the shaded cells                          | 111 |

| Table 6.  | Actual speedups (over a single node) for SCI. The shaded rows      |     |

|           | are speedups for the 16-node systems with 2- and 3-dimensional     |     |

|           | topologies that are used as the base cases for normalizing         |     |

|           | GLOW speedups                                                      | 118 |

| Table 7.  | Speedup of static GLOW (S) over SCI on 16 to 128 nodes,            |     |

|           | 2 and 3 dimensions.                                                | 119 |

| Table 8.  | GLOW speedup over SCI for (running on the same number of nodes)    |     |

|           | for GAUSS for three inputs.                                        | 124 |

| Table 9.  | Speedup using combining (C), AGENT DETECTION (A), and              |     |

|           | static GLOW (S) over SCI on 16 to 128 nodes, 2 and 3 dimensions    | 138 |

| Table 10. | Speedup using fast and slow switches for SCI (SCI), combining (C), |     |

|           | AGENT DETECTION (D), and static GLOW (S).                          |     |

|           | The base case is SCI on 16 nodes with fast switches.               | 144 |

| Table 11. | Results for wide sharing optimizations (speedup over SCI)          | 160 |

| Table 12. | Statistics for wide sharing prediction (directory-feedback scheme) | 160 |

| Table 13. | Techniques to apply the migratory sharing optimization             | 179 |

| Table 14. | Simulation results for migratory sharing optimizations             |     |

|           | (32 nodes, speedup over SCI)                                       | 196 |

| Table 15. | Statistics for instruction-based prediction.                       | 199 |

| Table 16. | Producer-consumer sharing optimizations                            | 194 |

| Table 17. | Statistics for producer-consumer LAST-PREDICTION with              |     |

|           | speculative pre-send (32 nodes).                                   | 212 |

| Table 18. | Statistics for producer-consumer INTERSECTION-PREDICTION with      |     |

|           | speculative pre-send (32 nodes).                                   | 213 |

### 1 Introduction

The shared-memory multiprocessing paradigm is well established for small-scale parallel machines such as bus-based multiprocessors. The uniform global address space of the shared-memory model, through which all data communication is performed, leads to a clean and elegant programming model that is preferable in many situations over the message-passing programming model.

Larger shared-memory machines built of smaller bus-based symmetric multiprocessors (SMP nodes) are also advancing in the marketplace. Because buses do not scale beyond a small number of processors (usually up to 16), larger shared-memory machines are built by physically distributing the memory among a number of nodes connected with a network. To drive development costs down and shorten time-to-market, distributed shared-memory systems leverage existing commodity parts such as processors, main-boards, and networks designed to support fine-grain communication [41].

Typically, in such architectures, a directory-based coherence protocol is employed to maintain *cache coherence* (*CC*) among the SMP nodes. Contemporary examples of such architectures include the HP/Convex Exemplar [26] and Sequent STiNG [68] that use Scalable Coherent Interface (SCI) networks and SCI cache coherence [41], and the SGI Origin 2000 [62] that uses a directory-based cache coherence protocol originating in Stanford's DASH multiprocessor [65].

The widespread use of hardware shared-memory systems (especially SMP's) presents an

opportunity to promote shared-memory parallel programming to a much larger audience of programmers than ever before. However, for widespread use of shared-memory, we need to address performance issues that arise in distributed shared-memory machines. Weber and Gupta's research [100] has revealed the existence of various sharing patterns in shared-memory programs. For example, sharing patterns such as migratory sharing and producer-consumer sharing have been identified and optimizations specific to such patterns have been proposed.

In this thesis I examine optimizations for hardware distributed shared-memory architectures and for various sharing patterns. The main thrust of the thesis is on wide sharing, but I also examine migratory sharing, and producer-consumer sharing. I propose a new optimization for wide sharing called GLOW and a new optimization based on speculative execution for producer-consumer sharing. For migratory sharing I study an optimization inspired by previous work [28,93].

Because these optimizations are specific to a sharing pattern they should not be applied indiscriminately for all accesses. Doing so may result in performance loss. Therefore, we need to identify the data affected by a sharing pattern, or the accesses that belong to a sharing pattern, and selectively apply the corresponding optimization.

Identification of the sharing pattern is orthogonal to the optimization for the sharing pattern. In this thesis I examine the identification of sharing patterns in two dimensions. The first dimension corresponds to the time the identification takes place. Identification can take place at compile-time, or **statically**. In this case the programmer or the compiler identifies the sharing pattern. Alternatively, identification can take place at run-time, or **dynamically**. In this

case, run-time mechanisms identify a sharing pattern and invoke the corresponding optimization.

The second dimension corresponds to the method used for the identification. Either the data that are affected by a sharing pattern can be identified, henceforth called **address-based identification**, or the memory instructions that are involved in a sharing pattern can be identified, henceforth called **instruction-based identification**. Dynamic instruction-based identification, using prediction is one of the major contributions of this thesis.

In the rest of this chapter I introduce the optimizations to the three sharing patterns (Section 1.1) and the corresponding dynamic/static and address-based/instruction-based identification techniques (Section 1.2).

#### 1.1 Sharing patterns and optimizations

Several classes of sharing patterns in shared-memory applications have been identified (migratory, read-only, frequently-written sharing, etc. [22,100]). In this thesis I examine wide sharing, and to a lesser degree migratory sharing and producer-consumer sharing. The characteristics of these sharing patterns and the optimizations I propose are introduced below.

#### 1.1.1 Wide sharing

Widely-shared data that are read simultaneously by many—usually all—processors is a distinct sharing pattern that imposes increasingly significant overhead as systems increase in size. When all processors read widely-shared data there is much contention in the home node for servicing the requests as well as in the network around the home node which becomes a *hot spot* [78]. Similarly, when the widely-shared data are written, there is a large number of invalidations (or updates) to be sent all over the system (*i.e.*, non-locally). For systems with no provision for efficient broadcast or multicasts, these invalidations consume much network bandwidth, in a wasteful manner.

In this thesis, I argue that in fact, widely-shared data inherent in some parallel algorithms are a more serious problem than previously recognized, and that furthermore, it is possible to provide support that gives an advantage to widely-shared data. The idea of read-combining [36,95] evolved because of the concern for network contention for widely-shared data. Read-combining is highly dynamic, and reduces traffic in the network by recognizing that simultaneous requests can be merged. The probability of occurrence of simultaneous requests only becomes a factor when serious network contention extends the latency of individual requests,

and in general, the best that combining can hope to achieve is a reduction in latency of access to widely-shared data to the latency that would be experienced in an unloaded network.

Alternatively, it is possible to access widely-shared data even faster than non-widely-shared data. The presence of redundant copies of a datum in multiple caches throughout the system offers this possibility: if data are widely shared there has to be network (*geographical*) locality—if some data that are needed by a node are widely shared, it is likely that a cached copy of the data is closer than the original data in the home node. This situation has some resemblance to cache-only memory (COMA) machines [37], where data are quickly accessed if they reside in a cache close to the requester. If an architecture can exploit this fact to improve accessibility of widely-shared data, programmers would find that the best algorithms make extensive use of widely-shared data rather than eschewing it. Thus, the potential for systems that provide high-quality support for widely-shared data may be much larger than would be indicated by a sample of current shared-memory programs, which generally avoid such data wherever possible.

Previous proposals for a wide sharing optimization, such as the STEM Kiloprocessor Extensions to SCI [44] and others [17,69,76] have largely ignored network locality in the network or they are closely tied to a network that is physically hierarchical. In this thesis, I propose a comprehensive solution to optimize wide sharing that borrows from the best attributes of previous proposals. The solution is given in the form of extensions (called GLOW extensions) to other directory-based cache-coherence protocols. The GLOW extensions offer scalable reads and scalable writes to widely-shared data. Scalable reads are achieved by caching directory information in the network, a technique inspired by the request combining proposed for CHoPP [95] and subsequently for the NYU Ultracomputer [36]. Because the directory infor-

mation is more long-lived, this technique can be effective even when multiple requests are not generated simultaneously. Scalable writes are achieved by exploiting the topology to invalidate or update sharing nodes in logarithmic time. The three main goals that guided the design of GLOW were:

- TO CREATE SHARING TREES THAT MAP WELL ONTO ARBITRARY TOPOLOGIES, thus achieving low-latency protocol messages. To achieve this goal, GLOW builds *logical* sharing trees that follow the request patterns in the network. Multilevel inclusion Appendix 13 is not enforced thus, GLOW is topology independent and effectively avoids deadlocks in arbitrary topologies.

- TO PROVIDE SCALABLE READS by exploiting request combining, independent of the timing of requests.

- TO PROVIDE SCALABLE WRITES by using the tree structure to invalidate or update sharing nodes in parallel.

The GLOW cache-coherence protocol extensions are specifically designed to handle accesses to widely-shared data. GLOW should not be applied to non widely-shared data because in this case the overhead of building a sharing tree may outweigh the benefit.

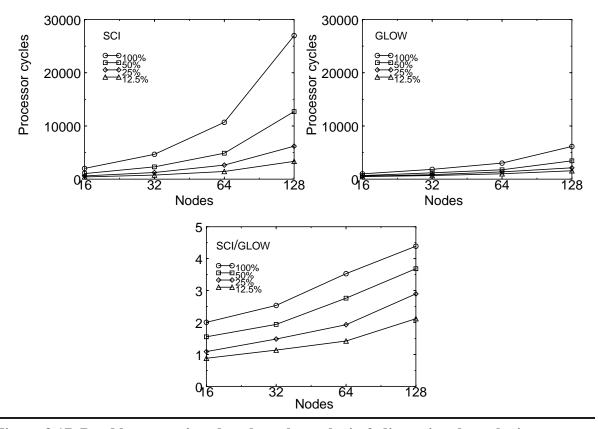

Through detail execution-driven simulation I study a GLOW implementation on top the SCI IEEE/ANSI standard cache-coherence protocol for six programs that do have widely-shared data and for various system configurations. For the systems and the workload I have studied, I found:

GLOW provides scalable reads and writes lacking in the base coherence protocol (SCI).

- Widely-shared data start to become detrimental to performance for large systems (for 16 nodes and up).

- In systems with GLOW, the six programs I have studied scale better even with a fixed input size. Increasing the input size increases the performance difference more than linearly among systems with support for wide sharing (GLOW) and systems without.

- Relaxed memory models improve performance by hiding write latencies but cannot replace GLOW which directly reduces both read and write latencies. Thus, GLOW on a strict memory model such as sequential consistency is significantly better than SCI with a relaxed memory model.

I have also studied two sharing-tree replacement algorithms for GLOW and to a limited extent update protocols in GLOW.

#### 1.1.2 Migratory sharing

Migratory sharing refers to data that are read, modified, and written by a single processor at time. Typically, such data are accessed within critical sections. In previous work (by Cox and Fowler [28], and by Stenström, Brorsson, and Sandberg [93]) the optimization is to collapse the coherent read (that first accesses the migratory data) and the coherent write (that updates the migratory data) in a single transaction. This optimization is performed by the home node directory, which is responsible to dynamically detect migratory sharing. For migratory data the directory simply returns a *writable* copy to a read request (after invalidating any older copies). The optimization used in this work is initiated by a node that is accessing migratory data by simply converting the first coherent read of the migratory data to a coherent write. This first appeared in the form of a specialized coherence protocol for migratory sharing in the Munin

software Distributed Shared Memory (DSM) system [22].

#### 1.1.3 Producer-consumer sharing

Producer-consumer sharing is one of the more difficult sharing patterns to optimize because conceptually, all sharing can be classified under this pattern. However, optimizations have been proposed for *stable* producer-consumer sharing. The goal of such optimizations is to transfer newly created values from the producer to the consumer as soon as possible. The optimizations are various update protocols and variations of Data Forwarding [59,3,62]. Update protocols have well known problems such as superfluous update messages and implementation constraints with sequential consistency [61,5]. Data Forwarding totally relies on the programmer/compiler for correctness.

In this thesis, I propose a novel optimization for producer-consumer sharing that is both transparent and independent of the memory model. The idea is to *pre-send* data speculatively to potential consumers. The consumers can use the data speculatively, provided that they eventually verify the correctness of the data through the cache-coherence protocol. In this way, processors can race ahead speculatively, while coherence enforcement follows behind.

This optimization trades bandwidth for latency. Because the simulation environment I use in this thesis does not allow speculative execution, I only report mis-speculation statistics (analogous to branch prediction studies). The low mis-speculation rates for four programs indicate that there is potential for performance gains but further research is needed to quantify the performance of this optimization.

#### 1.2 Identification of sharing patterns

Along with the sharing pattern optimizations (primarily the GLOW extensions for wide sharing but also the speculative pre-send for producer-consumer sharing) the major contribution of this thesis is a thorough examination of techniques to identify sharing patterns and selectively apply optimizations. I divide the techniques into dynamic and static and into address-based and instruction-based. Table 1 shows all possible cases.

|      |             | Тіме                     |                           |

|------|-------------|--------------------------|---------------------------|

|      |             | Compile-time (Static)    | Run-time (Dynamic)        |

|      |             | (user/compiler)          | (run-time mechanisms)     |

| ТүрЕ | Address     | Static address-based     | Dynamic address-based     |

|      | Instruction | Static instruction-based | Dynamic instruction-based |

Table 1. Techniques to identify a sharing pattern.

Static vs. Dynamic: To change the interface or not?—The choice between static and dynamic depends on: (i) whether it is possible to change the software/hardware interface and (ii) implementation costs. Static methods require an interface to pass information from the program to the hardware. Various reasons may render such an interface infeasible. For example, compatibility reasons or commodity hardware may pose problems. Additionally, the static methods require the involvement of the user (programmer) or, at the very least, the compiler. Static methods may also be undesirable since they subtract from the elegance of the shared-memory programming paradigm. On the other hand, dynamic methods require more expensive mechanisms at run-time to detect sharing patterns. The advantage of dynamic approaches is that they are transparent to the architecture and to the user/compiler. However, they require

custom hardware and incur hardware costs.

Address vs. Instruction: Examine what happens to the data or what the program is trying to do?—The choice between address-based or instruction-based approaches depends on many factors. Static address-based and static instruction-based methods are comparable: both require involvement of the user and/or compiler, both have the same implementation problems (software/hardware interface) and their performance depends on the ability to correctly define a sharing pattern using addresses or instructions. Dynamic address-based and dynamic instruction-based techniques differ considerably. In this thesis, I will show that the dynamic instruction-based techniques require few hardware resources and can outperform the more expensive dynamic address-based techniques.

#### 1.2.1 Static techniques

Static address-based techniques have been proposed for all three sharing patterns (Table 2). I discuss previous work and describe static instruction-based techniques to distinguish sharing patterns. However, I evaluate only the dynamic counterparts of these techniques (instruction-based prediction).

#### 1.2.2 Dynamic address-based techniques

Dynamic address-based detection has been previously proposed for migratory sharing and producer-consumer sharing (Table 2). I propose and evaluate two dynamic address-based identification techniques for wide sharing:

AGENT DETECTION: This scheme is inspired by request combining [36] and is based on observing requests in the network switch nodes that implement the GLOW extensions (also called GLOW agents). The switch nodes (agents) observe requests and intercept the ones that appear to repeat frequently. This dynamic scheme tracks closely the performance of the static address-based GLOW while it outperforms ordinary request combining for the programs and the systems I have examined.

• **DIRECTORY DETECTION**: In this scheme, the memory directory discovers widely-shared data by counting the number of reads between writes. Information about widely-shared data is distributed to the nodes which subsequently use the GLOW extensions to access them. In the evaluation I show that this scheme works well when the nature of the widely-shared data is persistent over time.

# 1.2.3 Dynamic Instruction-based techniques: Instruction-based prediction

Prediction is used for the three dynamic instruction-based techniques to identify sharing patterns. The main idea of *instruction-based prediction* is to examine—at run-time—the behavior of load and store instructions in relation to coherence events. In every node, the past behavior of its load and store instructions is stored in a *small* predictor table. Whenever dynamic instances of load and store instructions generate coherence events (such as misses, or writefaults on read-only cache blocks) we consult the predictors for optimization hints. This means that the optimizations affect the behavior of the processor toward the cache-coherence protocol (*e.g.*, on a load-miss the processor may ask for permission to write) in contrast to address-based prediction optimizations that affect the behavior of the cache-coherence protocol toward the processor (*e.g.*, the cache-coherence protocol—on its own—may decide to return a writable block to a processor that asks for a read-only block).

Instruction-based prediction is not new in the uniprocessor world: it is established research that already appears in commercial processors. Branch prediction is the pioneering instruction-based prediction method studied extensively by many researchers including Smith [92] and Yeh and Patt [105]. Abraham et al. showed that very few loads are responsible for most cache misses [4] and subsequently Tyson et al. proposed instruction-based prediction to selectively bypass the cache for such loads [98]. Gonzalez, Aliagas, and Valero used instructionbased prediction to steer data on caches optimized differently for spatial and temporal locality [33]. Moshovos, Breach, Vijaykumar, and Sohi introduced memory-dependence prediction [72]. They proposed dependence predictors accessed using the address of memory instructions. Subsequently, Moshovos and Sohi proposed memory optimizations based on dependence predictions [73]. Tyson and Austin also proposed similar memory optimizations [97]. This thesis is the first research effort to bring these techniques in the world of parallel sharedmemory architectures. Although I believe that such techniques can be generally applicable (from bus-based cache coherence to software-based coherence), in this thesis I present the techniques for hardware directory-based coherence.

The benefits of instruction-based prediction/optimization can be significant:

- Concise representation of history: Code is much smaller than datasets—static loads and stores can be only so many while the dataset can be arbitrarily large—and keeping track of the history of load and store instructions rather than memory blocks and/or cache blocks consumes far fewer resources.

- 2. A single technique for many optimizations: The technique I propose can be used to optimize several sharing patterns using a common, small predictor structure per node. In con-

trast, each address-based prediction scheme is tailored for a specific sharing pattern. Each may require its own states in the coherence protocol and its own storage (usually on a per block basis) for history information. Although Mukherjee and Hill showed how to generalize address-based prediction [75], the issue of excessive storage for history information remains.

However, there are important issues involved with instruction-based prediction in sharedmemory:

- Implementation issues: Instruction-based prediction calls for a tight integration of the processor core and the coherence mechanisms because information from both places is needed in the predictor.

- Performance issues: Address-based prediction inherently keeps large amounts of history information and in some situations this might be preferable to the "concise" information we can gather regarding load and store instructions.

The instruction-based prediction techniques I examine for the three sharing patterns are:

- Wide sharing: Predict whether a load will access widely-shared data. I propose and

evaluate two schemes to predict whether a load instruction will access widely-shared data.

These schemes consistently outperform both the AGENT DETECTION and DIRECTORY

DETECTION dynamic address-based schemes for the programs studied (Chapter 4).

- Migratory sharing: Predict whether a load-miss will be followed by a store-write-fault. This prediction can lead to optimization of migratory sharing patterns. The reasoning is that migratory sharing patterns often generate load-misses closely followed by

store-write-faults. For a set of seven programs studied for this sharing pattern, instruction-based prediction requires far less resources than the (dynamic address-based) adaptive migratory protocols while performing comparably (Chapter 5).

Producer-consumer sharing: Predict which node is going to consume a value generated by a store. This scheme examines store instructions that generate write-faults and keeps track of the potential readers of the newly written cache-blocks. The goal is to predict upon seeing a store-write-fault, whether there is a stable producer-consumer relationship and to predict the identity of the consumer(s). This scheme is inspired by uniprocessor dependece prediction work Appendix 72. There are three degrees of optimization (from conservative to aggressive): (i) Using a simple predictor we can initiate pairwise sharing with direct cache-to-cache transfers without involving the home directory, (ii) switch to an update protocol—though this is not transparent in the case of a sequential consistent memory system—, and (iii) using enhanced predictors we can *speculatively pre-send* the newly created values to the predicted consumers. In this thesis I examine the first and third cases (Chapter 6).

#### 1.3 Contributions

Here, I summarize the contributions of this thesis. Table 2 illustrates how previous work maps into the optimization space. Table 3 illustrates the contributions of this thesis. The union of these two tables covers all possible cases.

| WIDE SHARING      | Static           | Dynamic                                        |

|-------------------|------------------|------------------------------------------------|

| Address           | EC [17]          | STEM [44]                                      |

|                   | PROXIES [96][15] | Combining [36]                                 |

|                   |                  |                                                |

| Instruction       | _                | _                                              |

| MIGRATORY SHARING | Static           | Dynamic                                        |

| Address           | Munin [22]       | Adaptive protocols for migratory data [28][93] |

| Instruction       | _                | _                                              |

| PRODUCER-<br>CONSUMER SHARING | Static                      | Dynamic            |

|-------------------------------|-----------------------------|--------------------|

| Address                       | Munin [22]                  | Competitive Update |

|                               | Update protocols            |                    |

| Instruction                   | Data Forwarding [59][3][62] | _                  |

Table 2. Previously proposed identification techniques for three sharing patterns (shaded cells).

#### In brief, I propose:

For wide sharing: the GLOW optimization; a static address-based, a static instruction-based, two dynamic address-based, and two dynamic instruction-based methods to selectively apply the optimization.

- For migratory sharing: a dynamic instruction-based method to apply an optimization (which is inspired by previous work). Additionally, I discuss a static instruction-based method.

- For producer-consumer sharing: a dynamic instruction-based method to apply a novel optimization based on speculative execution. I discuss three variations of this method.

| WIDE SHARING      | Static                  | Dynamic                       |

|-------------------|-------------------------|-------------------------------|

| Address           | Static GLOW-address     | 1) Agent Detection            |

|                   |                         | 2) Directory Detection        |

| Instruction       | Static GLOW-Instruction | Instruction-based prediction: |

|                   |                         | 1) Latency                    |

|                   |                         | 2) Directory feed-back.       |

| MIGRATORY SHARING | Static                  | Dynamic                       |

| Address           | _                       | _                             |

| 11dd1 CSS         |                         |                               |

| PRODUCER-<br>CONSUMER SHARING | Static | Dynamic                           |

|-------------------------------|--------|-----------------------------------|

| Address                       | _      | _                                 |

| Instruction                   | _      | Instruction-based prediction with |

|                               |        | Speculative pre-send:             |

|                               |        | 1) Last prediction                |

|                               |        | 2) Intersection prediction        |

|                               |        | 3) Two-level adaptive             |

Table 3. Identification techniques proposed in this thesis.

#### 1.4 Thesis roadmap

Following the Introduction, in Chapter 2 I present the evaluation methodology used throughout this thesis. In Chapter 3, I present the GLOW extensions to optimize wide sharing. GLOW is independent of how wide sharing is defined statically or detected dynamically. Thus, in Chapter 4 I describe a set of techniques (static, dynamic, address-based and instruction-based) to distinguish wide sharing and selectively apply the GLOW optimizations. Chapter 5 describes the dynamic instruction-based prediction for migratory sharing. Chapter 6 presents instruction-based prediction for producer-consumer sharing and the optimization based on speculative execution. Finally, in Chapter 7, I summarize this thesis and conclude.

**Nomenclature:** In this thesis I use the following naming conventions: *load*, *store* are the actual instructions; *read*, *write* are the cache coherence actions resulting from loads and stores. A cache block that is not *Invalid* can be either *ReadOnly* (*RO*) or *ReadWrite* (*RW*). A load or store can experience a cache *miss* which results in a coherent read or write; furthermore a store can experience a *write fault* on a RO cache block which results in a coherent write.

# Evaluation Methodology

This section presents the experimental methodology used for all evaluations in this thesis. Simulation is applied to study the effects of optimizations for wide sharing, migratory sharing and producer-consumer sharing. In Section 2.1, I discuss the Wisconsin Wind Tunnel (wwt) [79] simulation environment. To study optimizations for wide sharing, I enhanced wwt with detailed network simulation described in Section 2.2. Finally, in Section 2.3, I describe the benchmark programs used throughout this thesis.

## 2.1 Wisconsin Wind Tunnel

A detailed study of the optimizations proposed in this thesis requires execution driven simulation because of the complex interactions among the processors, their caches, the memory modules, and the network. The Wisconsin Wind Tunnel [79] is a well-established tool for evaluating large-scale parallel systems through the use of massive, detailed simulation. wwT simulates shared-memory systems on a message-passing host system (a Thinking Machines Corp. CM-5 [40]). It executes target parallel programs at hardware speeds (without intervention) for the common case when there is a hit in the simulated coherent cache. In the case of a miss, the simulator takes control and executes the appropriate actions defined by the simulated protocol. WWT keeps track of virtual time in processor cycles. The direct execution nature of WWT poses certain limitations: only instructions that generate coherence events are observable; the coherent caches are blocking; the cache-block size must be a power-of-two multiple of the hardware cache-block size (32 bytes) of the host system (CM-5); and finally speculative execution is not supported.

Kägi, Aboulenein, Burger, and Goodman have simulated SCI extensively under WWT [47] and all the optimizations I study (for wide sharing, for migratory sharing, and for producer-consumer sharing) have been applied to this simulation environment. I simulated systems that resemble SCI systems made of readily available components such as SCI rings and workstation nodes.

For the evaluations in Chapters 3 and 4—which require detailed network simulation—I have simulated k-ary n-cube systems (such as the Wisconsin Multicube proposed by Goodman and

Woest [34]) from 16 to 128 nodes in two and three dimensions. For practical reasons, in the evaluations of Chapters 5 and of 6—where accurate network simulation is not critical—I simulated a constant latency (100 processor cycles) network.

The nodes comprise a processor, an SCI cache, memory, a memory directory, a GLOW agent that implements the GLOW extensions, and a number of ring interfaces. The processors run at 500MHz and execute one instruction per cycle in the case of a hit in their cache. Each processor is serviced by a 64K 4-way set-associative cache with a cache-block size of either 32 or 64 bytes (see the discussion of cache parameters in Section 2.3). Processor, memory, and network interface (including GLOW agents) communicate through a 166 MHz 64-bit *split-transaction* bus (1.266 GB/s peak bandwidth). The bus transfers 64 bits per bus cycle (every 3 processor cycles). Memory and directory accesses require 4 bus cycles (12 processor cycles) before the start of the data transfer while cache access requires 1 bus cycle (3 processor cycles).

The GLOW agents are enhanced switches that connect the ring interfaces and pass messages from one to the other. To implement the GLOW optimizations for widely-shared data each GLOW agent is equipped with a 1024-entry directory cache and 64K of data storage. To minimize conflicts, the agent's directory is organized as a 4-way set-associative cache. Although I assume uniprocessor nodes, GLOW applies equally well to symmetrical multiprocessor (SMP) nodes. In this case, the GLOW agent resides in the network interface of the SMP node and is responsible for servicing the set of processors inside the node.

## 2.2 Network

For the evaluation of the wide-sharing optimizations it is imperative to accurately simulate the network of a parallel system. This is because the effect of widely-shared data on the network performance is critical. Although the GLOW extensions described in the next chapter can be applied to many different topologies, I use the k-ary n-cube networks of SCI rings in 2 and 3 dimensions. Because of its scalability, this topology has great appeal in real world systems such as the CRAY T3D [21] and T3E [87], SGI Origin 2000 [62], Convex Exemplar 2000 [1]. The rings use a 500 MHz clock; 16 bits of data can be transferred every clock cycle through every link, giving a total of 1GB/sec bandwidth. This is equivalent to the actual IEEE 1596 standard which describes a 250 MHz network that sends 16 bits of data at both clock edges.

Figure 2.1. 2-dimensional and 3-dimensional networks made of SCI rings.

I simulate contention throughout the network, but messages are never dropped since I assume infinite queues. The model I use deviates from the SCI specification in that I do not simulate SCI's bandwidth allocation algorithms (based on the so-called "Go-bits" [41]), nor SCI's scheduling between ring traffic and outgoing traffic from the nodes. As can be seen in Figure

2.2, the SCI interface specifies three classes of queues: the Input queues, the Output queues and the Bypass buffer. The Input and Output queues are actually pairs of queues, each pair comprises a queue for requests and a queue for responses. The Bypass buffer captures the ring traffic while the output link is busy with outgoing traffic from the Output queue. SCI specifies that while the Bypass buffer is not empty, the Output queue cannot be drained. SCI guarantees fairness in bandwidth allocation with Go-bits that throttle the outgoing traffic of nodes. Eventually, the Bypass buffer will be empty and the Output queue can transmit. I do not model the arbitration between the Output queue and the Bypass buffer. Any messages in these queues are interleaved with a total FIFO order. I do not model the Go-bits algorithm for bandwidth allocation. However, since both the Output queue and the Bypass buffer have equal access to the output link, there is no starvation of the Output queue.

Queues are simulated using WWT's servers. A WWT server keeps autonomous virtual time and can generate and accept messages. A server's virtual time is updated on message arrivals and also internally, by advancing its virtual clock by some cycles. The WWT has three default servers per node: the CPU server, the cache server, and the directory server. WWT orders messages in virtual time and delivers them to the appropriate server. In the network model, each queue is a different server with its own virtual time. The queueing in a node is shown in Figure 2.3. The ring interfaces are connected to the processor, cache, memory, and directory through the system bus. However, the GLOW agent and the ring switch are directly connected to the ring interfaces. I simulate all queues with a fixed latency of 10 processor cycles and a transfer latency of 1 processor cycle per 16 bits.

I performed comparisons with a different model of the SCI network developed by Burger

In the standard SCI ring Interface, messages in the Output buffer are not transmitted while the Bypass buffer is not empty. Eventually the Bypass buffer will empty because of the bandwidth allocation algorithms of the SCI ring.

In the simplified model the arbitration between the Bypass and Output buffer is missing, hence a single queue for both.

Figure 2.2. SCI ring interface assumptions.

Figure 2.3. Queueing in a node (only one ring interface shown for clarity). The GLOW server is close to the ring interface and does not have to go through the bus to communicate with other nodes. This is because the GLOW server represents the switch that connects multiple ring interfaces together and transfers messages from one to the other.

[19,20]. This model uses finite queues and retransmissions. It takes into account the arbitration between the Output queues and the Bypass buffers, but it does not implement the Go-bit algorithm for bandwidth allocation on the rings (hence it does not guarantee forward progress for the Output queues). The difference of the execution time of two benchmarks (GAUSS and SPARSE benchmarks described in Section 2.3) for 32- and 64-node 2-dimensional systems using the two network models—setting all other parameters to equivalent values—is less than 5% (Burger's simulation model is consistently faster). Since the two network models produce similar read and write latencies, the discrepancy in execution time is due to other simulator differences, such as the modeling of contention in the local bus. Burger's network simulation is centralized in one node: messages are routed to a single node for the purpose of network simulation and then to their final destination. Unfortunately, this is unsuitable for studying wide-sharing optimizations (discussed in the next chapter) which require the availability of the messages in many places along their network path.

## 2.3 Benchmarks

Here, I describe the ten benchmark programs used in this thesis to study optimizations for three types of sharing: wide sharing, migratory sharing and producer-consumer sharing. The benchmarks were chosen because they exhibit one or more of the sharing patterns. Benchmarks that do not exhibit a sharing pattern are used as *control* benchmarks to study potential negative effects on performance. The ten programs are:

- GAUSS, SPARSE, APSP, TC, CG, BARNES (wide sharing)

- CHOLESKY, MP3D, PTHOR (various degrees of migratory sharing)

- OCEAN (producer-consumer sharing)

| Benchmark | Input Size  | Cache<br>size/<br>Block<br>size | Wide<br>Sharing | Migratory<br>Sharing | Prod<br>Cons.<br>Sharing | References   |

|-----------|-------------|---------------------------------|-----------------|----------------------|--------------------------|--------------|

| CHOLESKY  | bsstk14     | 64K/32                          |                 | Yes                  |                          | [91][28][93] |

| MP3D      | 10K/10 iter | 64K/32                          |                 | Yes                  |                          | [91][28][93] |

| PTHOR     | risc        | 64K/32                          |                 | Little               |                          | [91][28][93] |

| GAUSS     | 512x512     | 64K/64                          | Yes (dyn.)      |                      | Yes                      | [17][25][50] |

| SPARSE    | 512x512     | 64K/64                          | Yes (static)    |                      |                          | [50]         |

| APSP      | 256x256     | 64K/64                          | Yes (dyn.)      |                      |                          | [17][50]     |

| TC        | 256x256     | 64K/64                          | Yes (dyn.)      |                      |                          | [50]         |

| BARNES    | 4K part.    | 64K/64                          | Yes (static)    |                      |                          | [91][50]     |

| CG        | 128x128     | 256K/64                         | Yes             |                      |                          | [14]         |

| OCEAN     | 130x130     | 64K/32                          |                 |                      | Yes                      | [91][47]     |

Table 4. Benchmarks used in this work. For each benchmark, the input size, the cache and block size, and prominent sharing patterns are described. The references point to papers where the benchmarks are described or used in the same way as in this work.

Table 4 summarizes the benchmarks. The input size describes the input data set of the programs. Because I use detailed network simulation, multiple WWT servers per node (eight or

more compared to WWT's default of three), and because I simulate multiple target nodes perhost node (I simulate target systems of up to 128 nodes on 32 host nodes) it is feasible to simulate only small datasets. Large datasets either exceed the memory capacity of the host system or take an unreasonably long time to simulate. Nevertheless, I simulated a limited number of cases with large datasets to examine scalability. I used 64K caches for all benchmarks. This size is somewhat large for most of the small datasets of the benchmarks. Although capacity misses are not eliminated, the emphasis is on coherence misses. I used 64-byte cache blocks for studying wide-sharing optimizations. SCI defines 64-byte cache blocks and this size generally results in good performance for the base SCI case. I used 32-byte cache blocks for the migratory and producer-consumer optimizations where finer-grain sharing works better.

#### 2.3.1 GAUSS