### **Processor Implementation**

Forecast -- heart of course -- key to project

- Sequential logic design review

- Clocking methodology

- Datapath -- 1 CPI

- single instruction, 2's complement, unsigned

- Control

- Multiple cycle implementation

- Microprogramming

- Exceptions

© 2000 by Mark D. Hill

CS/ECE 552 Lecture Notes: Chapter 5

# **Review Sequential Logic**

Logic is combinational if output is solely function of inputs

e.g., ALU of previous lecture

Logic is sequential or "has state" if output function of

- past and current inputs

- past inputs "remembered" in "state"

- but no magic!

© 2000 by Mark D. Hill

CS/ECE 552 Lecture Notes: Chapter 5

# **Review Sequential Logic**

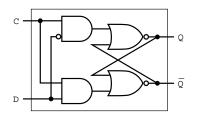

E.g., D latch

Clock high Q = D,  $\overline{Q} = \overline{D}$  after some min to max propagate delay

clock low Q,  $\overline{Q}$  remain unchanged

sensitive to clock level

# **Review Sequential Logic**

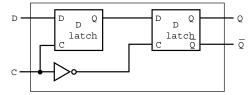

E.g., D flip-flop

While clock high, D flows into 1<sup>st</sup> latch, but not 2<sup>nd</sup>

There Q retains old value

Remebmer D at falling edges and propagates through 2<sup>nd</sup> latch

© 2000 by Mark D. Hill

#### **Review Sequential Logic**

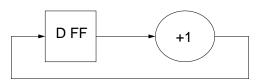

Can build

Why does this fail for latch?

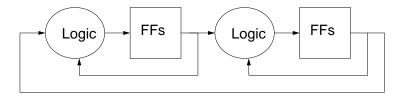

## **Clocking Methodology**

Motivation

- Design datapath/control without thinking about clocks

- Use convention called clocking methodology

- restricts design freedom

- hides complexity

| © 2000 by Mark D. Hill | CS/ECE 552 Lecture Notes: Chapter 5 | 5 | © 2000 by Mark D. Hill | CS/ECE 552 Lecture Notes: Chapter 5 | ( |

|------------------------|-------------------------------------|---|------------------------|-------------------------------------|---|

|                        |                                     |   |                        |                                     |   |

## **Our Methodology**

Only Flip-flops

All on same edge (e.q., falling)

All with same clock (omit from pictures)

All logic finishes in one clock cycle

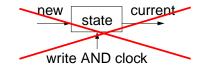

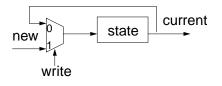

#### Our Methodology, cont.

Do \*NOT\* use qualified clocks:I

CorrectI

#### Datapath - 1 CPI

Assumption: Get whole instruction done in one long cycle

Instructions: add, sub, and, or, slt, lw, sw, & beq

To do

- For single instruction

- Put it together

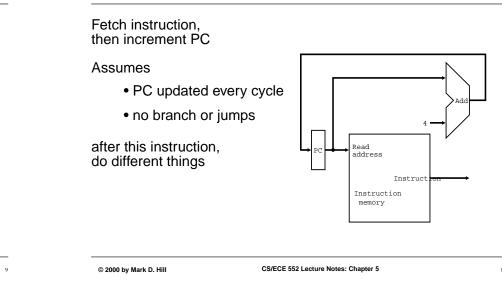

#### **Fetch Instructions**

© 2000 by Mark D. Hill

CS/ECE 552 Lecture Notes: Chapter 5

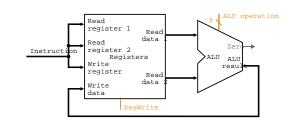

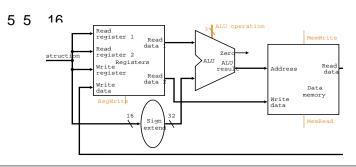

#### **ALU Instructions**

And \$1, \$2, \$3 # \$1 destination

Use R-format

opcode rs rt rd shamt funct

6 5 5 5 5 6

### Load/Store Instructions

xw \$1, immed(\$2) # \$1 <-> M[SE(immed)+\$2]

Use I-format

6

11

opcode rs rt immed

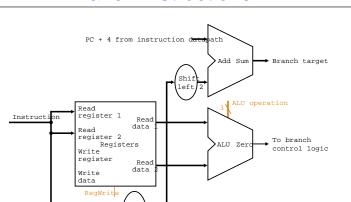

#### **Branch Instructions**

beq \$1, \$2, addr # if (\$1 == \$2) PC = PC + addr<<2

Actually

- newPC = PC + 4

- target = newPC + addr<<2 # in MIPS offset from newPC

- if (\$1-\$2 == 0)

- PC = target

- else

- PC = newPC

Sign 32

CS/ECE 552 Lecture Notes: Chapter 5

14

16

© 2000 by Mark D. Hill

**Branch Instructions**

| © 2000 by Mark D. Hill | CS/ECE 552 Lecture Notes: Chapter 5 | 13 |

|------------------------|-------------------------------------|----|

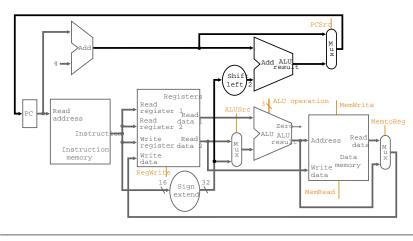

## All Together

15