## Cache Organization III

March 30, 2016 . Ganesh Kumar

## Code

```

int dotproduct(int x[8], int y[8]) {

int sum = 0;

int i;

for (i = 0; i < 8; i++)

sum += x[i] * y[i];

return sum;

}</pre>

```

Good spatial locality?

Assume a 6-bit address space with t=1, s=1 and b=4.

Say x[0] is stored at address 0.... and x[7] at address 28. And y[0] starts immediately after at address 32 .... and y[7] at 60.

| Element | Address | Set index | Element | Address | Set index |

|---------|---------|-----------|---------|---------|-----------|

| x[0]    | 0       | 0         | у[0]    | 32      | 0         |

| x[1]    | 4       | 0         | y[1]    | 36      | 0         |

| x[2]    | 8       | 0         | y[2]    | 40      | 0         |

| x[3]    | 12      | 0         | y [3]   | 44      | 0         |

| x[4]    | 16      | 1         | y[4]    | 48      | 1         |

| x[5]    | 20      | 1         | y [5]   | 52      | 1         |

| x[6]    | 24      | 1         | y [6]   | 56      | 1         |

| x[7]    | 28      | 1         | y[7]    | 60      | 1         |

$$x[0]$$

- Address  $0 = 0$  0000 -> Maps to Set 0

$$x[3]$$

- Address 12 = 0 0 1100 -> Maps to Set 0

The first four element addresses in X map to set 0.

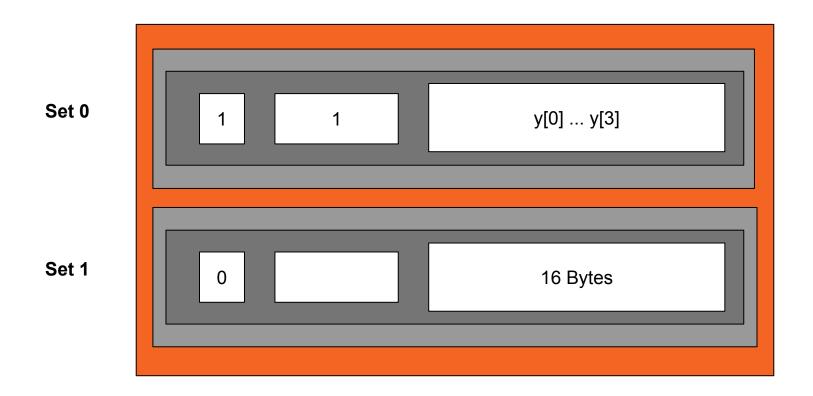

$$y[0] - Address 32 = 1 0 0000 -> Maps to Set 0$$

$$y[3] - Address 44 = 1 0 1100 -> Maps to Set 0$$

The first four element addresses in Y map to set 0.

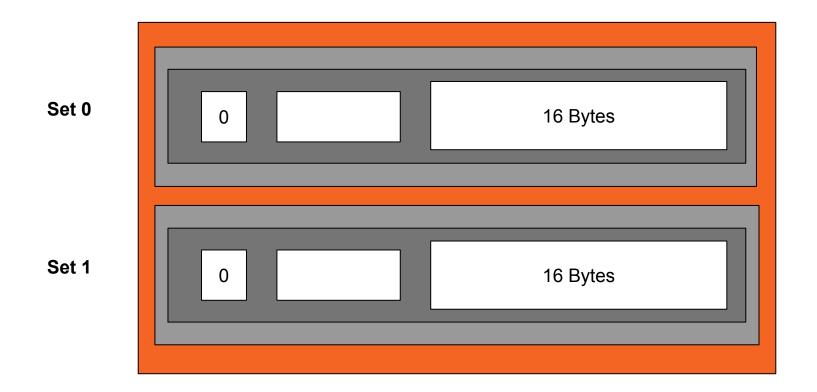

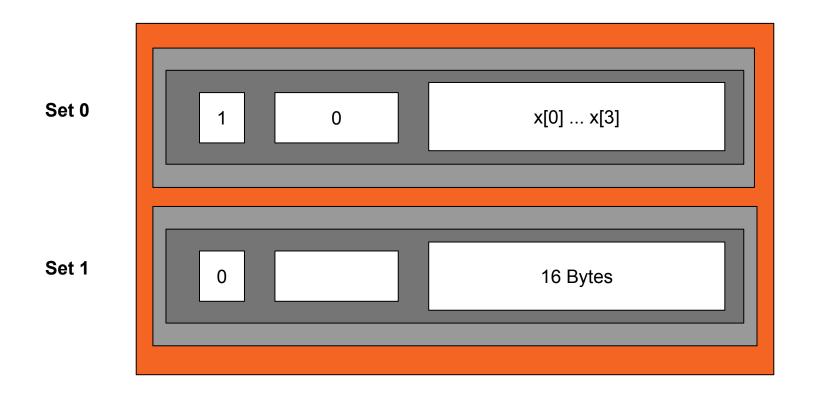

In 1st iteration, Search for x[0] in cache.... Valid bit not set... Cache miss! Read the block containing x[0] onto the cache.

Still in 1st iteration,

Search for y[0] in cache... Address 32 - 10 0000... Set 0

Tag bits don't match... Cache miss!

So, read the block containing y[0] onto the cache.

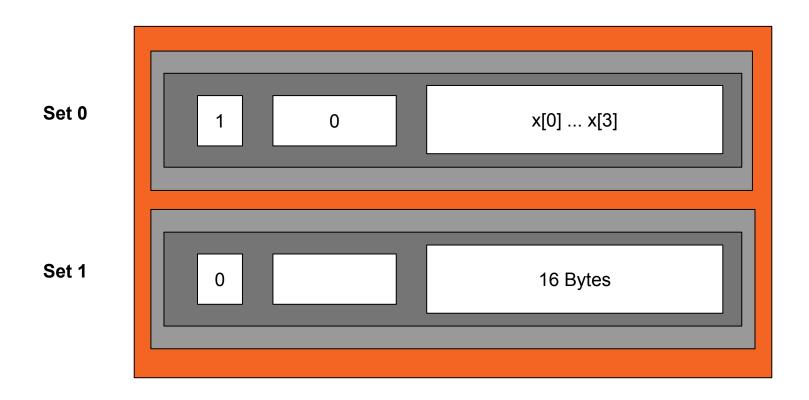

Still in 1st iteration,

Search for y[0] in cache... Address 32 - 10 0000

Tag bits don't match... Cache miss!

So, read the block containing y[0] onto the cache.

Replace existing line in Set 0

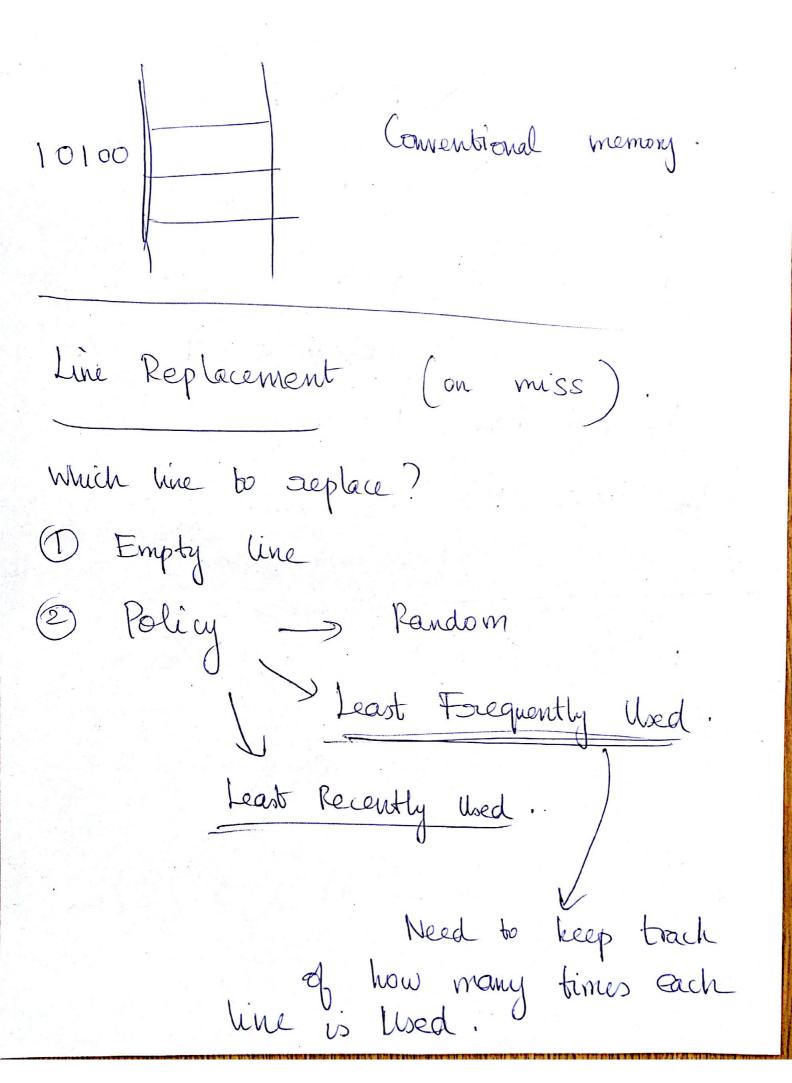

3 / 30 Edution to these problems? In Grease E ! Set Associate Cache L/B 1/2 × 4 E -> two-way associative cache -> Three - way associative cache. E is also called associativity. Set Matching Line Matching (key, value) Date Block. valid + tag bits (Associative memosy)

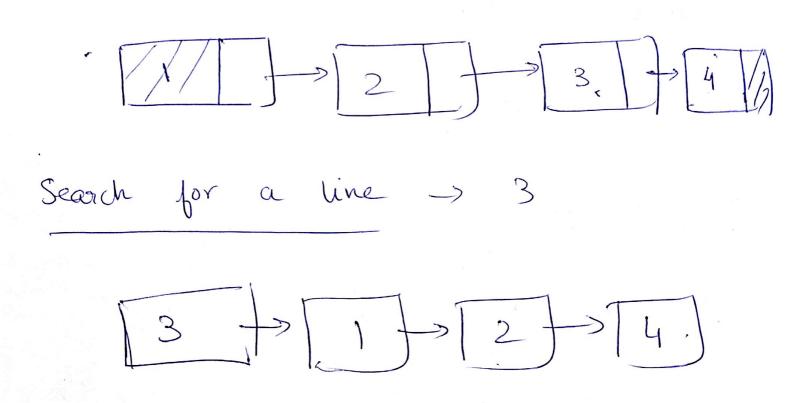

LRU.

Fully Associative Cache

E = C/B/

SXEXB SXE S = 1-> We just have I set ! > We have no set bits (s=0) Not possible

So far reads Writes? Say we write to a word the cache (write hit) when should we update the value of w in MM K the Disk? 1) Write - through Main Mem Disk Do it immediately! Drawback 7

## Scanned by CamScanner

1 Super slow !

@ Bus traffic!

the updated 2 Waite - back write only so when a line is going to be replaced. Drawbacks. Need an extra bit! Dirty bit > If updated, to 1,

It not, set bo

Write misses? Need to write to W 1) Write - allocate. Load w onto the

Cache and then Main Mamory

update it

(Assumes good spatial locality) Main Marrory 2 No-write allocate Bypass the cache and write directly to the not memory. Write thorough / No - write - allocate. Write back, / Write - allocate Cache levels at lower memory hierarchy

Scanned by CamScanner

Cache diagram core core 2 core 3 core O Registers 2 cache L3 cache Main memory could be only !