0x00C

## CS 354: Lecture 28 - Notes

- 1. Suppose we have a system with the following properties:

- a. The memory is byte addressable.

- b. Memory accesses are to 1-byte words (not to 4-byte words).

- c. Addresses are 12 bits wide.

- d. The cache is two-way set associative (E = 2), with a 4-byte block size (B = 4)

and four sets (S = 4).

5=2

$B = 4 = 2^{2}$

The contents of the cache are as follows, with all numbers given in hexadecimal

notation.

b = 2

|           |      |        | ()0    | U      | 10/ 1 .  |          |

|-----------|------|--------|--------|--------|----------|----------|

| Set index | Tag  | (Valid | Byte 0 | Byte 1 | Byte 2   | Byte 3   |

| 0         | 00   | , 1    | 40     | 41     | 42       | 43       |

| , 0       | (83) | 1)     | FE     | 97/    | CC       | D0       |

| 1         | 00   | 1      | 44     | 45     | 46       | 47       |

| 1 .       | 83   | 100X   | 0x-v   |        |          |          |

| 2         | 00   | 1      | 48     | 49     | 4A       | 4B       |

| 2         | 40   | 0      | -      |        | <b>*</b> | <b>1</b> |

| 3         | ( FF |        | 9A     | (C0)   | . 03     | FF       |

| 3         | 00   | 0      | 944    | *      | 444      |          |

- A. The following figure shows the format of an address (one bit per box). Indicate (by labeling the diagram) the fields that would be used to determine the following:

- CO The cache block offset

- CI The cache set index

- CT The cache tag

| 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3  | 2 | 1  | 0  |

|----|----|---|---|----|---|---|---|----|---|----|----|

| ,  |    |   |   | 1. |   |   |   | CI | J | CO | CO |

CT

ORFFC - F

Suppose a program running on the machine references the 1-byte word at address 0x831. Indicate the cache entry accessed and the cache byte value returned in hex. Indicate whether a cache miss occurs. If there is a cache miss, enter "-" for "Cache byte returned."

| returr             | ied."    |           |           |     |   | D   | V ( | 221 |    |          |    | 11   | L .1 | 0. |

|--------------------|----------|-----------|-----------|-----|---|-----|-----|-----|----|----------|----|------|------|----|

| . В                | . Addres | ss Form   | at        |     | - | U,  | Λ ζ | 331 | Se | <u> </u> |    | blo  | UR O | N  |

|                    | 5        |           |           | Υ   |   |     | 1   |     | 1  |          |    | T    |      |    |

| 11                 | 10       | 9         | 8         | 7   | 6 | 5   |     | 4   | 3  | 2        |    | 1    | 0    |    |

|                    | D        | 0         | 0         | 0   | D |     |     | 1   | 0  | D        |    | 0    | 1    |    |

| C                  | . Memor  | y Refer   | ence      | >   | 3 | Š   |     |     |    |          | JĮ |      |      | 1  |

|                    | Parar    | neter     |           |     |   |     | Va  | lue |    |          |    | 4    |      |    |

|                    | Cache    | e block   | offset (C | CO) |   | ž   | 0x_ | 01  | 0  | R        | C  | )X ( |      |    |

|                    | Cache    | e set inc | lex (CI)  |     |   |     | 0x_ | 00  | 0  | R        | 0  | ×Ο   |      |    |

|                    | Cache    | e tag (C  | T)        |     |   | ō   | 0x_ | 83  |    |          |    |      |      |    |

| Cache hit? (Y / N) |          |           |           |     |   | Y   | 1   |     |    |          |    |      |      |    |

|                    | Cache    | e byte re | eturned   |     |   | 141 | 0x_ | 97  |    |          |    |      | -    |    |

D. For each of the following memory accesses indicate if it will be a cache hit or miss when carried out in sequence as listed. Also give the value of a read if it can be inferred from the information in the cache.

| ) | -X OXFFC, OXFFD, OXFFE, OXFFF |         |            |                            |  |  |  |  |  |

|---|-------------------------------|---------|------------|----------------------------|--|--|--|--|--|

| _ | Operation                     | Address | Hit / Miss | Read Value<br>(or unknown) |  |  |  |  |  |

|   | Read                          | 0x834   | Miss       | unknown.                   |  |  |  |  |  |

|   | Write                         | 0x836   | Hit        | 11                         |  |  |  |  |  |

|   | Read                          | 0xFFD   | 141        | OXCD                       |  |  |  |  |  |

E. What are the different addresses that have their tag bits as 0xFF and that would map to set 3?

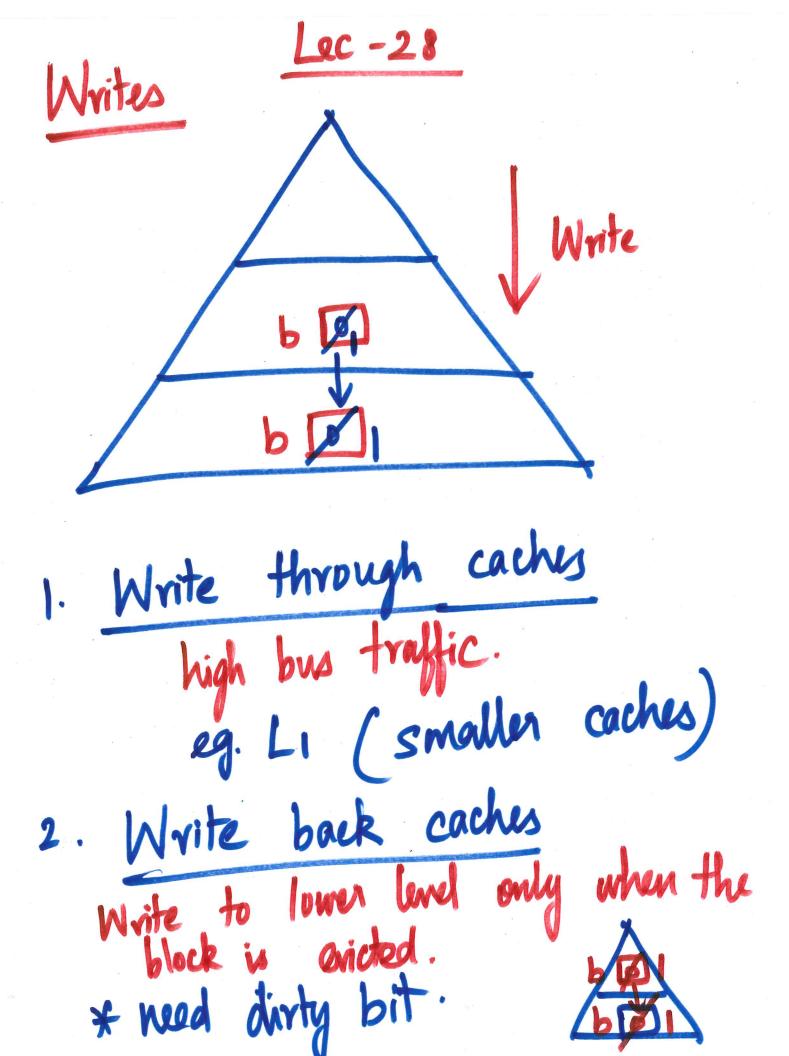

Writes no-write allocate write - allocati written in the cache. diretly write

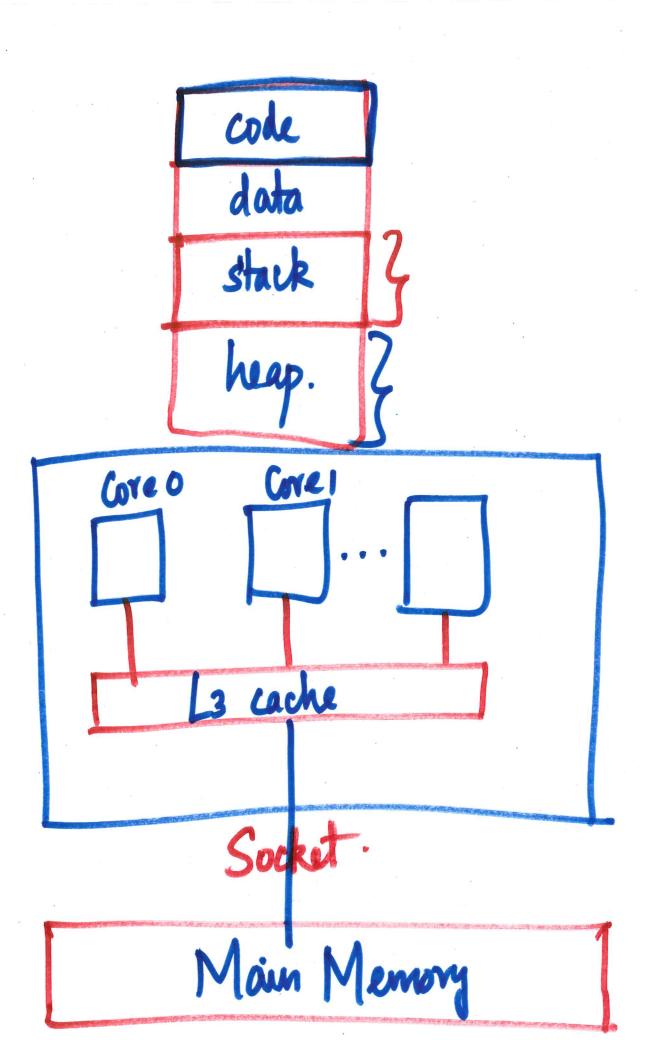

Real Cache Hierarchy Core O read only 32 KB 256 KB L2-unified cache 3-unified. 8 MB

Cache params

miss rate = # missus #-references. 1 - miss vate 2. hit rate = 3. but time = time to deliver a word in the cache to the CPU. = tsetselection + time selection + twoord identification.

4. miss penalty.