## Enhancing Transistor Sizing in Analog IC Design using a Circuit-Focused Semi-Supervised Learning

ESIB – USJ

Meta

Virgil systems

Rayan Mina, Houssam Nassif, George Sakr Beirut, December 2023

## Machine Learning in IC Design

> Novelty of this Work

### Conclusions and Perspectives

1/19/2024 Rayan MINA

## Context

> Machine Learning in IC Design

> Novelty of this Work

> Conclusions and Perspectives

# **The Analog Challenge**

Analog IC Design is a 2-step process

**Front-End Design (50%):** Schematic, computer simulations to tune component dimensions

**Back-End Design (50%):** Layout, schematic to physical representation of devices

➤ Scope of this work → Front-End Design

Analog circuit performance depends heavily on physical dimensions of circuit components

Analog IC designers are rare

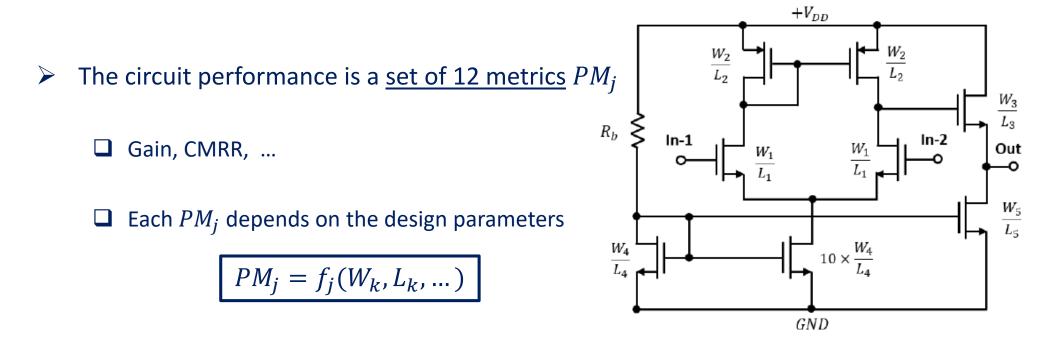

# **Analog IC Design Example**

A simple CMOS 2-stage op-amp has 11 design parameters

#### ▶ 12 mathematical functions of 11 variables $\in \mathbb{R}^+$ each → The design space is huge

# Agenda

## Machine Learning in IC Design

> Novelty of this Work

> Conclusions and Perspectives

1/19/2024 Rayan MINA

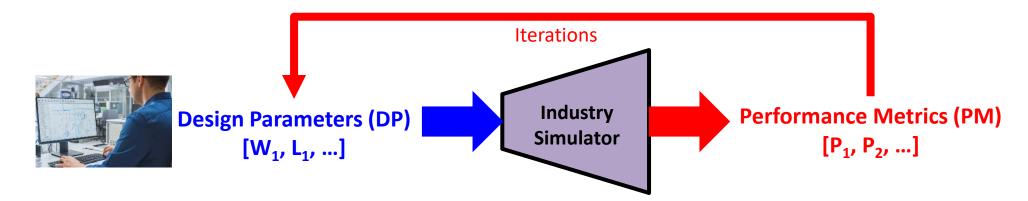

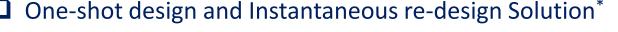

# **ML Application in IC Design**

### Time-consuming <u>Iterative</u> Analog IC design approach:

ML offers a solution by solving the Inverse-Problem in analog circuit design

# Agenda

## > Machine Learning in IC Design

> Novelty of this Work

> Conclusions and Perspectives

# First Attempt: Joint Approach (1)

- Target Circuit: 2-stage CMOS op-amp showed in slide #6, 11 DP

- Dataset: 150,000 samples = 120k +10k + 10k

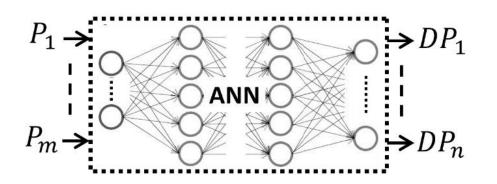

- Idea: PM are inputs to one ANN, trained to predict all the DP <u>simultaneously</u>

This joint approach is intuitive and straightforward

| Av               | Open-loop voltage Gain                      |  |  |  |

|------------------|---------------------------------------------|--|--|--|

| CMRR             | Common-mode rejection ratio                 |  |  |  |

| PSRR+            | Positive supply rejection ratio             |  |  |  |

| NSRR-            | Negative supply rejection ratio             |  |  |  |

| IIN              | Integrated noise level                      |  |  |  |

| NTH              | Thermal noise floor                         |  |  |  |

| Fc               | Noise corner frequency                      |  |  |  |

| GBW              | Gain-bandwidth product                      |  |  |  |

| PhM              | Phase margin                                |  |  |  |

| Ibs              | Current consumption                         |  |  |  |

| V <sub>OUT</sub> | dc output level                             |  |  |  |

| IIP <sub>3</sub> | 3 <sup>rd</sup> order Input-intercept point |  |  |  |

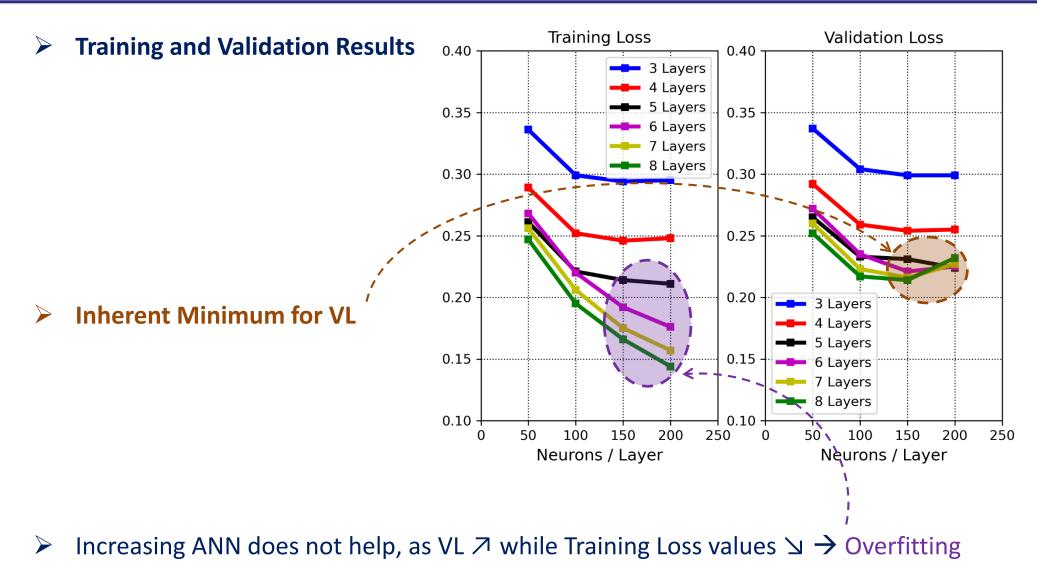

# First Attempt: Joint Approach (2)

**IMCET 2023**

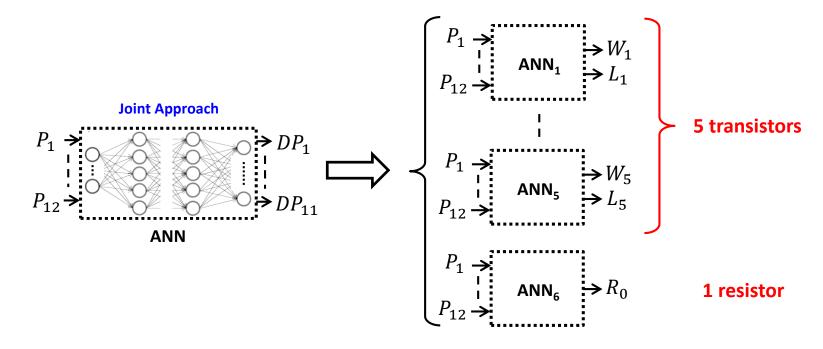

# **Investigation: Single Approach (1)**

To understand why we reached a minimum for VL, <u>investigation</u> is carried out

### Idea

- Each component is tuned as a standalone entity

- Width and Length of MOS transistors should be tuned together

- □ Assign a different ANN for each transistor to predict its W/L simultaneously

# **Investigation: Single Approach (2)**

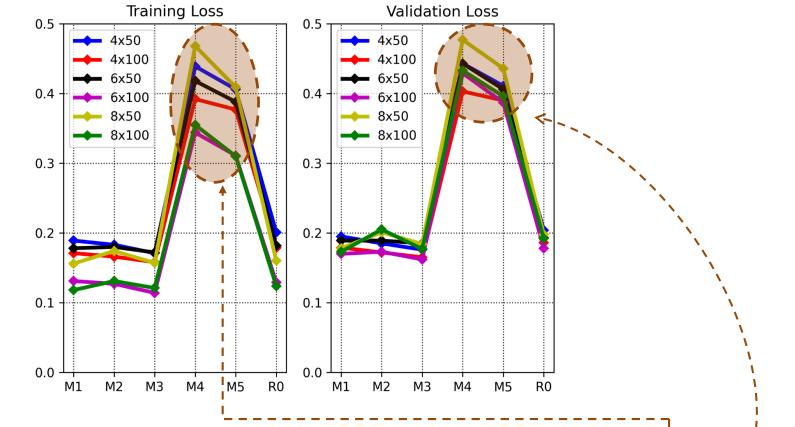

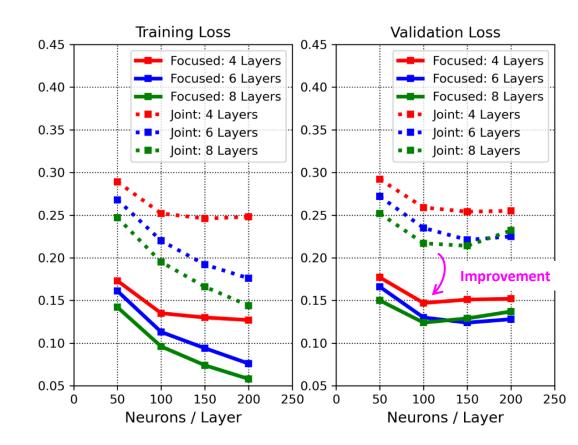

### $\succ$ Training and Validation Loss results of the investigation $\rightarrow$ two loss patterns

### **Conclusions:**

- Transistors M<sub>4</sub> & M<sub>5</sub> are challenging components for ANN to learn, high Training Loss & VL

- **D** Relationships between PM &  $M_4$  /  $M_5$  are less meaningful than those with the remaining DP

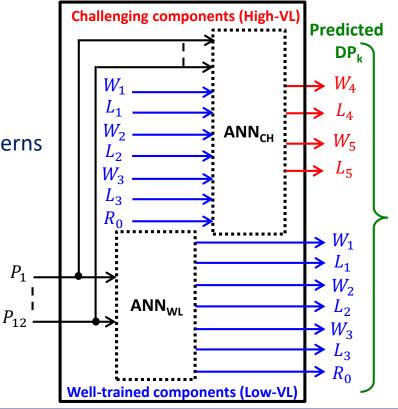

# **Innovative Focused Approach (1)**

- Based on VL results, we identified 2 patterns:

- Well-trained components with low VL values

- Challenging components with significant high VL values

- ➢ Solution → propose a Focused Learning Approach

- □ Target  $\rightarrow$  enhance the VL results

- Split the DP prediction into 2 ANNs based on VL patterns

- □ Challenging ANN<sub>CH</sub> has more inputs than ANN<sub>WL</sub>  $\checkmark$  Inputs = PM + DP<sub>well-trained</sub>

# **Innovative Focused Approach (2)**

For the challenging transistors, VL decreased by ~3.5 compared to the single approach

#### □ 6-layer ANN, 100 neurons/layer: VL ↘ from ~0.4 to ~0.11

| ANN Architecture |                      | Investigative Approach<br>(ANN for each transistor) |      | Focused<br>Approach |      |

|------------------|----------------------|-----------------------------------------------------|------|---------------------|------|

|                  |                      | VL                                                  | VL   | VL                  | TL   |

| Layers           | Neurons<br>per Layer | M4                                                  | M5   | M5                  |      |

| 4                | 50                   | 0.44                                                | 0.41 | 0.16                | 0.18 |

| 4                | 100                  | 0.40                                                | 0.39 | 0.12                | 0.13 |

| 6                | 50                   | 0.44                                                | 0.41 | 0.15                | 0.16 |

| 6                | 100                  | 0.43                                                | 0.39 | 0.11                | 0.12 |

| 8                | 50                   | 0.48                                                | 0.44 | 0.13                | 0.13 |

| 8                | 100                  | 0.43                                                | 0.40 | 0.10                | 0.11 |

### Joint vs Focused:

50% VL improvement on all ANN complexities

# Agenda

## Context

## > Machine Learning in IC Design

> Novelty of this Work

### Conclusions and Perspectives

# **Conclusions and Perspectives**

Evaluate the component predicting difficulty by training 1 ANN for each, using PM as inputs

Classify components into two categories, challenging (high VL) and straightforward (low VL)

Split the learning process into an ANN for each category, the challenging having a modified input structure incorporating DP of remaining components

Future work: test and validate the proposed focused approach on more analog circuits