# U. Wisconsin CS/ECE 552 Introduction to Computer Architecture

Prof. Karu Sankaralingam

Miscellaneous (5.5, 5.7, 5.6, & 6.8) www.cs.wisc.edu/~karu/courses/cs552

Slides combined and enhanced by Karu Sankaralingam from work by Falsafi, Hill, Marculescu, Nagle, Patterson, Roth, Rutenbar, Schmidt, Shen, Sohi, Sorin, Thottethodi, Vijaykumar, & Wood

#### Outline

- Multicycle Design (5.5)

- Implementing Control & Microprogramming (5.7)

- · Exceptions (5.6)

- Exceptions in a Pipeline (6.8)

CS/ECE 552 (2)

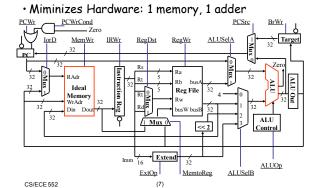

#### Multicycle Approach (No Pipelining)

- Break up the instructions into steps, each step takes a cycle

- balance the amount of work to be done

- restrict each cycle to use only one major functional unit

- At the end of a cycle

- store values for use in later cycles

- introduce additional "internal" registers

### Multicycle Approach

- · We will be reusing functional units

- ALU used to compute address and to increment  ${\it PC}$

- Memory used for instruction and data

- Our control signals will not be determined solely by instruction

- e.g., what should the ALU do for a "subtract" instruction?

- · We'll use a finite state machine for control

CS/ECE 552 (3) CS/ECE 552 (4)

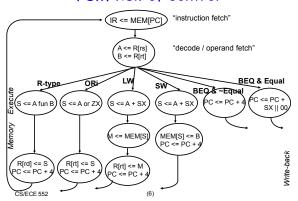

#### What Instructions Need to Do

| Step name                                               | Action for R-type instructions                                                            | Action for memory-reference instructions                       | Action for<br>branches         | Action for jumps                    |  |  |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------|-------------------------------------|--|--|--|--|

| Instruction fetch                                       | IR = Memory[PC]<br>PC = PC + 4                                                            |                                                                |                                |                                     |  |  |  |  |

| Instruction decode/register fetch                       | A = Reg [IR[25-21]]<br>B = Reg [IR[20-16]]<br>ALUOut = PC + (sign-extend (IR[15-0]) << 2) |                                                                |                                |                                     |  |  |  |  |

| Execution, address computation, branch/ iump completion | ALUOut = A op B                                                                           | ALUOut = A + sign-extend<br>(IR[15-0])                         | if (A ==B) then<br>PC = ALUOut | PC = PC [31-28] II<br>(IR[25-0]<<2) |  |  |  |  |

| Memory access or R-type completion                      | Reg [IR[15-11]] =<br>ALUOut                                                               | Load: MDR = Memory[ALUOut]<br>or<br>Store: Memory [ALUOut] = B |                                |                                     |  |  |  |  |

| Memory read completion                                  |                                                                                           | Load: Reg[IR[20-16]] = MDR                                     |                                |                                     |  |  |  |  |

CS/ECE 552 (5)

# FSM view of Control

# Multicycle Datapath

# Outline

- · Multicycle Design (5.5)

- Implementing Control & Microprogramming (5.7)

- Exceptions (5.6)

- Exceptions in a Pipeline (6.8)

CS/ECE 552 (8)

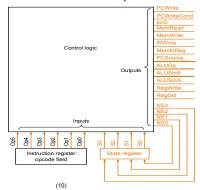

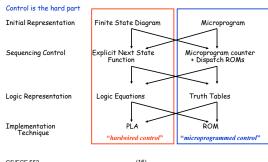

# Implementing the Control

- · Value of control signals is dependent upon:

- what instruction is being executed

- which step is being performed

- Use the information we've acculumated to specify a finite state machine

- specify the finite state machine graphically, or

- use microprogramming

- · Implementation can be derived from specification

CS/ECE 552 (9)

#### Finite State Machine for Multicycle Control

Implementation

State bits

Clin Clan

CS/ECE 552

- D-flipflopsControl Logic

- Comb. Block

- Use PLA or ROM

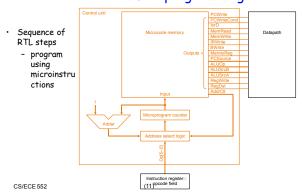

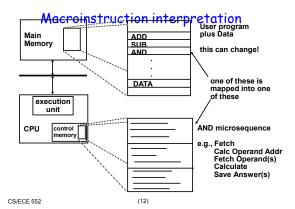

#### Alternative: Microprogramming

# Microprogramming

| Label    | ALU<br>control | SRC1 | SRC2    | Register control | Memory    | PCWrite control | Sequencing |

|----------|----------------|------|---------|------------------|-----------|-----------------|------------|

| Fetch    | Add            | PC   | 4       |                  | Read PC   | ALU             | Seq        |

|          | Add            | PC   | Extshft | Read             |           |                 | Dispatch 1 |

| Mem1     | Add            | Α    | Extend  |                  |           |                 | Dispatch 2 |

| LW2      |                |      |         |                  | Read ALU  |                 | Seq        |

|          |                |      |         | Write MDR        |           |                 | Fetch      |

| SW2      |                |      |         |                  | Write ALU |                 | Fetch      |

| Rformat1 | Func code      | Α    | В       |                  |           |                 | Seq        |

|          |                |      |         | Write ALU        |           |                 | Fetch      |

| BEQ1     | Subt           | Α    | В       |                  |           | ALUOut-cond     | Fetch      |

| JUMP1    |                |      |         |                  |           | Jump address    | Fetch      |

- A specification methodology (alternate to FSM)

- appropriate if hundreds of opcodes, modes, cycles, etc.

- signals specified symbolically using microinstructions

- Microassembler?

CS/ECE 552 (13)

#### Microprogramming Pros and Cons

- · Ease of design

- · Flexibility

- Easy to adapt to changes in organization, timing, technology

- Can make changes late in design cycle, or even in the field

- Can implement very powerful instruction sets (just more control memory)

- Generality

- Can implement multiple instruction sets on same machine.

- Can tailor instruction set to application.

- Compatibility

- Many organizations, same instruction set

- · Costly to implement

- Slow

CS/ECE 552 (14)

#### Next time: memory

# Control: Summary

CS/ECE 552 (15) CS/ECE 552 (16)

4

#### Outline

- Multicycle Design (5.5)

- · Implementing Control & Microprogramming

- Exceptions (5.6)

- Exceptions in a Pipeline (6.8)

CS/ECE 552 (17)

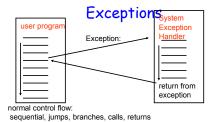

- Exception = unprogrammed control transfer

- system takes action to handle the exception

- must record the address of the offending instruction

- returns control to user

- must save & restore user state

- · Allows constuction of a "user virtual machine" CS/ECE 552 (18)

# Interrupt, Exception, Trap?

- $\cdot$  Interrupts

- caused by external events

- asynchronous to program execution

- may be handled between instructions - simply suspend and resume user program

- Traps

- caused by internal events

- · exceptional conditions (overflow)

- errors (parity)

faults (non-resident page)

synchronous to program execution

condition must be remedied by the handler

- instruction may be retried or simulated and program continued or program may be aborted

- MIPS convention:

- External : Interrupts

- Internal : Exception

CS/ECE 552 (19)

#### **Exception Semantics**

- · MIPS architecture defines the instruction as having no effect if the instruction causes an exception.

- When get to virtual memory we will see that certain classes of exceptions must prevent the instruction from changing the machine state.

- This aspect of handling exceptions becomes complex and potentially limits performance => why it is hard

- Precise interrupts vs Imprecise interrupts

CS/ECE 552 (20)

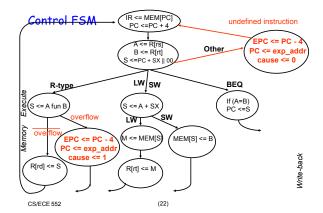

#### MIPS Exceptions

- · All exceptions jump to same handler code

- "Cause" register

- · We consider

- Illegal instructions

- Arithmetic overflows

- · Handler behavior

- Save PC of offending instruction (How? PC+4 has already been written to PC)

- Use special register EPC(why not use \$31 like jal?)

- Set cause register appropriately (0=ILL; 1=OVF)

- Jump to handler at fixed address

CS/ECE 552 (21

#### Other issues

- · Vectored exceptions

- "cause" folded into handler address

- Different causes jump to different handlers

- · User vs kernel mode

- · Software issues

- Disabling exceptions in handler

- · Returning from interrupt

CS/ECE 552 (23)

#### Outline

- · Multicycle Design (5.5)

- Implementing Control & Microprogramming (5.7)

- · Exceptions (5.6)

- Exceptions in a Pipeline (6.8)

CS/ECE 552 (24)

# Exceptions

- · Semantics

- No instruction after the exception causing instruction may execute

- Every instruction preceding the exception causing instruction must complete execution

- Set cause register

- Jump to exception handler address

- · Multiple instructions (exceptions) in a cycle!

CS/ECE 552

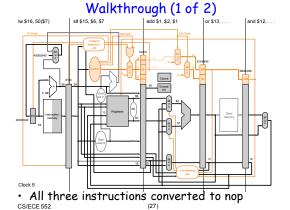

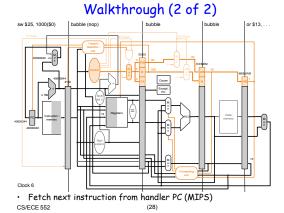

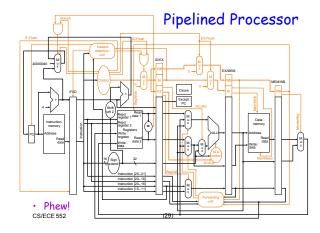

# Datapath modifications Pipeline complications

- · What stage is exception detected?

- Overflow?

- In EX stage, Also squash (convert to nop) EX stage

- Illegal Instruction?

- In ID stage, squash (convert to nop) ID stage

- · Similar to RAW hazard

- What about external interrupts?

- · Overflow in instruction i, illegal instruction in instruction i+1

- Simultaneous exceptions

- Hardware sorting

CS/ECE 552 (26)