#### U. Wisconsin CS/ECE 552 Introduction to Computer Architecture

Prof. Karu Sankaralingam

Pipelining (Chapter 6)

www.cs.wisc.edu/~karu/courses/cs552

Slides combined and enhanced by Karu Sankaralingam from work by Falsafi, Hill, Marculescu, Nagle, Patterson, Roth, Rutenbar,Schmidt, Shen, Sohi, Sorin, Thottethodi, Vijaykumar, & Wood

#### Outline

- · Pipelining

- What? Basic concepts

- · Overlapping execution

- · Latency vs. throughput

- Why? Performance implications

- Speedup

- · CPI, cycletime

- How? Implementation challenges

CS/ECE 552 (2) Sankaralingam

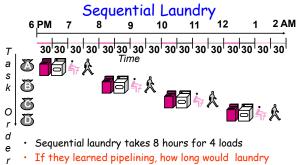

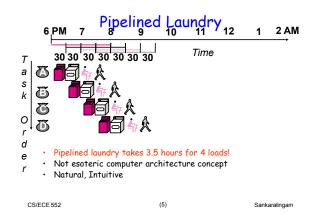

#### Pipelining · Laundry Example

- Ann, Brian, Cathy, Dave each have one load of clothes to wash, dry, and fold

- · Washer takes 30 minutes

- · Dryer takes 30 minutes

- "Folder" takes 30 minutes

- "Stasher" takes 30 minutes to put clothes into drawers

Sankaralingam

CS/ECE 552 (4) Sankaralingam

(3)

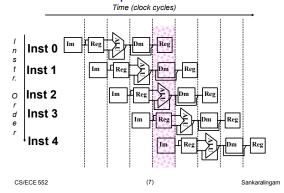

#### Seek to Pipeline Instructions

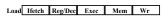

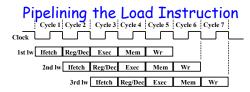

#### The Stages of Load

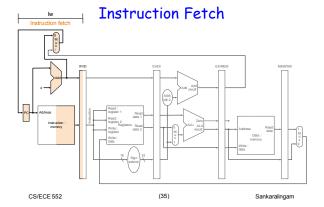

- · Ifetch: Instruction Fetch

- Fetch the instruction from the Instruction Memory

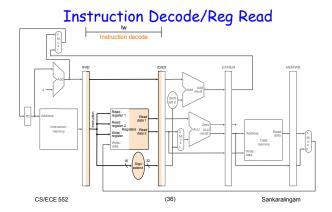

- Reg/Dec: Registers Fetch and Instruction Decode

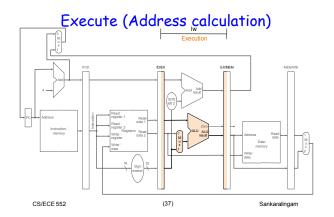

- Exec: Calculate the memory address

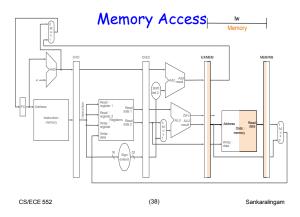

- Mem: Read the data from the Data Memory

- Wr: Write the data back to the register file

CS/ECE 552 (8) Sankaralingam

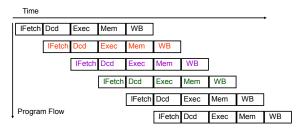

#### Pipelined Execution Representation

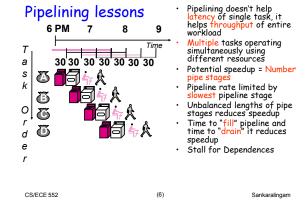

• Ideal speedup = 5, but ...

CS/ECE 552 (9) Sankaralingam

##

Ideal speedup is number of stages in the pipeline. Do we achieve this?

CS/ECE 552 (10) Sankaralingam

#### Non-uniform stages

$\label{eq:maximum_speedup} \begin{aligned} & \text{Maximum Speedup} \leq \text{Number of stages} \\ & \text{Speedup} \leq \text{Time for unpipelined operation} \\ & \hline & \text{Time for longest stage} \end{aligned}$

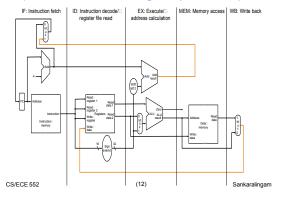

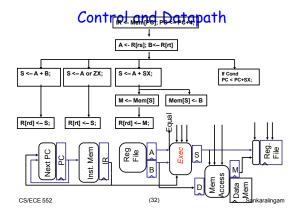

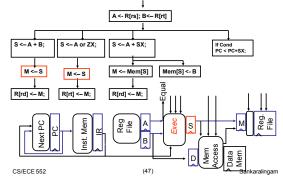

Pipeline Forecast: Single-Cycle Datapath

CS/ECE 552 (11) Sankaralingam

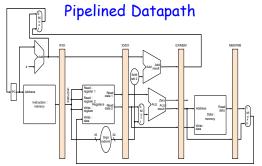

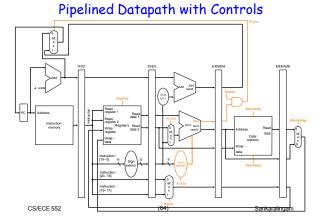

#### Pipeline Forecast: Pipelined Datapath

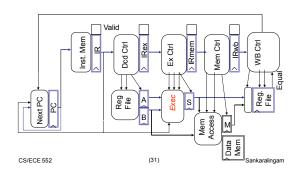

· Pipeline datapath with registers

CS/ECE 552 Sankaralingam

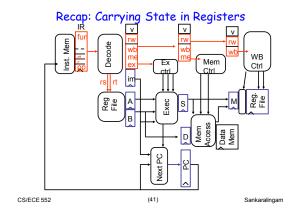

## Pipeline Forecast: Pipelined Control CS/ECE 552 (14)

#### Pipeline Forecast: Big Picture

- · Datapath similar to single-cycle datapath

- · Partition datapath with pipeline latches (D-FFs)

- · Naïve Control

- Generate single-cycle control signals

- Pass control signals through pipeline latches

- Apply control signals at appropriate stage/cycle

- · Truth is more complex (instruction interact)

#### Instructions vs. Laundry

- Definitely:

Need to maintain "illusion" of sequential execution

- Execution is actually overlapped.

- Pipeline Hazards

- structural hazards: attempt to use the same resource two different ways at the same time

Eg., combined washer/dryer would be a structural hazard or folder busy doing something else (watching TV)

data hazards: attempt to use item before it is ready

- - E.g., one sock of pair in dryer and one in washer; can't fold until get sock from washer through dryer

instruction depends on result of prior instruction still in the pipeline

- control hazards: attempt to make a decision before condition is evaulated

- E.g., washing football uniforms and need to get proper detergent level; need to see after dryer before next load in

- branch instructions

CS/ECE 552 Sankaralingam CS/ECE 552 (16) Sankaralingam

#### Hazards

- · Structural hazards

- Two instructions need the same hardware

- · Data Hazards

- Data not ready

- · Control Hazards

- Which instruction to fetch? Not known.

#### Hazards

- · Can always resolve hazards by waiting

- pipeline control must detect the hazard

- take action (or delay action) to resolve hazards

- · Delays

- Pipeline stalls/bubbles

- Reduce speedup

CS/ECE 552 (17) Sankaralingam CS/ECE 552 (18) Sankaralingam

# Single Memory: Structural Hazard Time (clock cycles) Load Mem Reg Mem Reg Instr 1 Instr 2 Instr 3 Instr 4 Detection is easy in this casel (right half highlight means read, left half write) CSECE 552 (19) Sankaralingam

#### Structural Hazards

- If 1.3 memory accesses per instruction

- How?

- 1 per instruction for instruction fetch

- Fraction for data load/store

- Depends on instruction mix

- · 20% load + 10% store

- · 15% load + 15% store

- CPI is atleast 1.3 (otherwise memory is used more than 100%)

CS/ECE 552 (20) Sankaralingam

#### Data Hazards

#### Data Hazard Solution

#### Forwarding (a.k.a. bypassing)

- · Can't solve with forwarding:

- Must delay/stall instruction dependent on loads

CS/ECE 552 (24) Sankaralingam

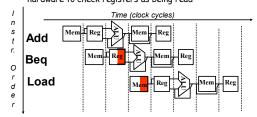

#### Control Hazard: Solutions • Stall: wait until decision is clear

- - Its possible to move up decision to 2nd stage by adding hardware to check registers as being read

Impact: 2 clock cycles per branch instruction => slow

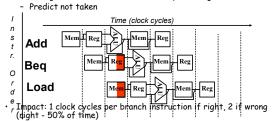

Control Hazard: Solutions

Predict: guess one direction then back up if wrong

· More dynamic scheme: history of 1 branch (- 90%)

CS/ECE 552 (25) Sankaralingam CS/ECE 552 (26) Sankaralingam

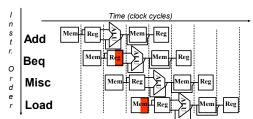

Control Hazard: Solutions

Redefine branch behavior (takes place after next instruction)

- Impact: 0 clock cycles per branch instruction if can find instruction to put in "slot" (- 50% of time)

- As launch more instruction per clock cycle, less useful CS/ECE 552 Sankaralingam

#### STOPPED HERE

CS/ECE 552 (28) Sankaralingam

7

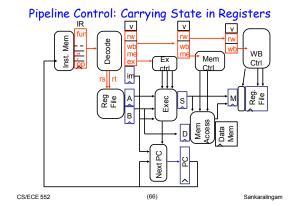

#### Pipelined Processor Design

- · Designing a pipelined processor

- Associate resources with states

- Resources not necessarily atomic

- · Register reads and writes can happen in the same cycle

- · Writes in first half of cycle and reads in the second half

- Assert appropriate controls in each stage

- Make sure all necessary information is carried through inter-pipestage flip-flops

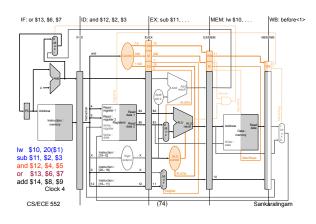

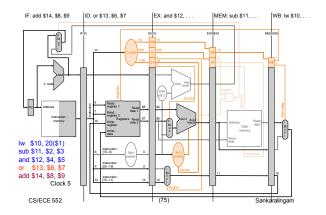

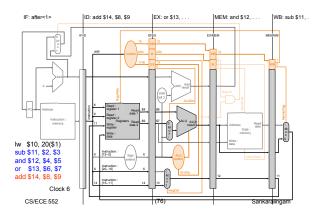

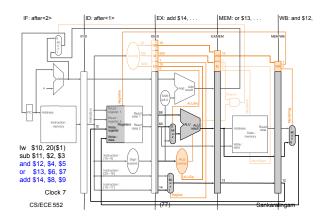

sub \$11, \$2, \$3 ALU atomic Register file/memory can handle read/write in the same cycle Memory cannot handle two reads

(30)

Shading convention

CC 4

CC 5

CC 6

Sankaralingam

Program

execution [ order 🗆

CS/ECE 552

(in instructions)

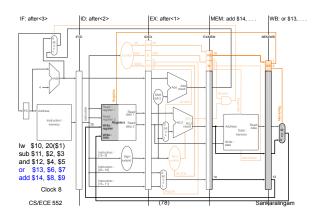

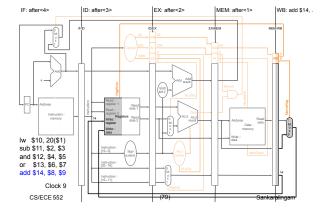

lw \$10, 20(\$1)

CS/ECE 552 (29) Sankaralingam

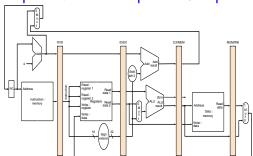

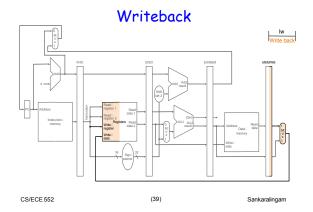

### Pipelined Processor (slide version) · What happens if we start a new instruction every cycle?

- The five independent functional units in the pipeline datapath are:

- Instruction Memory for the Ifetch stage

- Register File's Read ports (bus A and busB) for the Reg/Dec stage

- ALU for the Exec stage

- Data Memory for the Mem stage

- Register File's Write port (bus W) for the Wr stage

CS/ECE 552 (33) Sankaralingam

· Pipeline datapath with registers

CS/ECE 552 (34) Sankaralingam

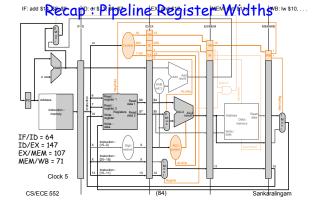

#### Pipeline registers

- Length of Pipeline registers

- Book says

- IF/ID : IR (32), PC+4 (32) : 64 bits ID/EX: IR (32), PC+4 (32) + RegA + RegB : 128 bits EX/MEM: ALUout(32) + zero(1) + PC+4+SX(imm) (32) : 97

- MEM/WB: ALUout (32) + MemData(32) : 64

- · Corrections:

- ALUout and MemData

- Destination register (5 bits)

- Other control bits (IR not going through)

CS/ECE 552 (40) Sankaralingam

#### The Four Stages of R-type

- · Ifetch: Instruction Fetch

- Fetch the instruction from the Instruction Memory

- Reg/Dec: Registers Fetch and Instruction Decode

- Exec:

- ALU operates on the two register operands

- Update PC

- Wr: Write the ALU output back to the register file

CS/ECE 552 (42) Sankaralingam

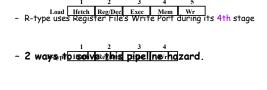

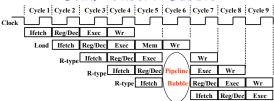

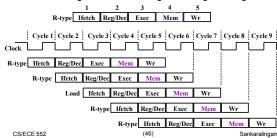

#### Pipelining R-type and Loads | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 | Ops! We have a problem! R-type Ifetch Reg/Dec Exec Wr R-type Ifetch Reg/Dec Exec Wr Load Ifetch Reg/Dec Exec Mem Wr R-type Ifetch Reg/Dec Exec Wr R-type Ifetch Reg/Dec Exec Wr

- · We have pipeline conflict or structural hazard:

- Two instructions try to write to the register file at the same

- Only one write port

CS/ECE 552 (43) Sankaralingam CS/ECE 552 (44) Sankaralingam

- Each functional unit must be used at the same stage for all instructions:

- Load uses Register File's Write Port during its 5th stage

#### Soln.1: Insert "Bubble"

- Insert a "bubble" into the pipeline to prevent 2 writes at the

- The control logic can be complex.

- Lose instruction fetch and issue opportunity.

- No instruction is started in Cycle 6!

CS/ECE 552 Sankaralingam

#### Soln.2: Delay R-type's Write Delay R-type's register write by one cycle:

- - Now R-type instructions also use Reg File's write port at Stage 5

- Mem stage is a NOOP stage: nothing is being done.

#### Modified Cantrol & Datapath

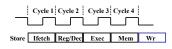

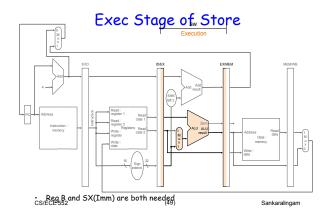

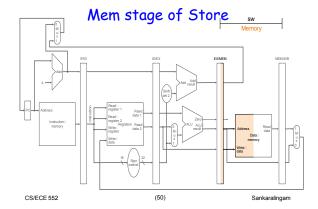

#### Four Stages of Store

- · Ifetch: Instruction Fetch

- Fetch the instruction from the Instruction Memory

- Reg/Dec: Registers Fetch and Instruction Decode

- · Exec: Calculate the memory address

- Mem: Write the data into the Data Memory

CS/ECE 552 (48) Sankaralingam

#### Three Stages of Beq | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Beq Ifetch Reg/Dec Exec Mem Wr

- Ifetch: Instruction Fetch

- Fetch the instruction from the Instruction Memory

- Reg/Dec:

- Registers Fetch and Instruction Decode

- Exec:

- compares the two register operand,

- select correct branch target address

- latch into PC

- Four stages as in book

Assume one delay slot (shadow instruction)

- One "predict not taken" instruction

(51) CS/ECE 552 Sankaralingam CS/ECE 552 (52) Sankaralingam

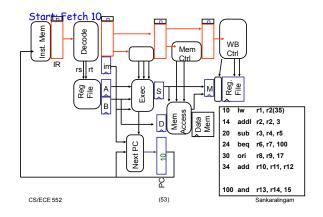

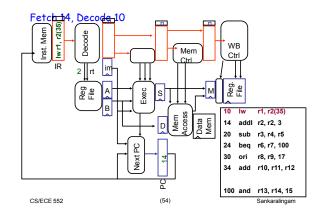

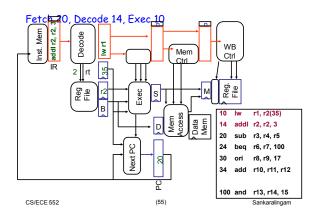

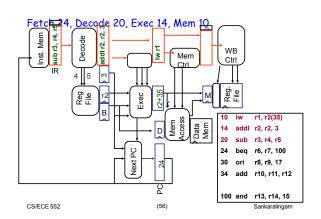

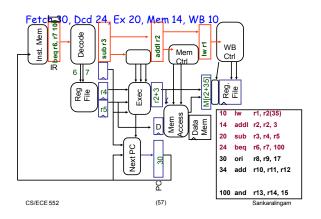

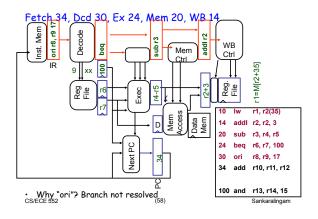

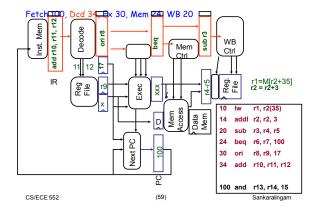

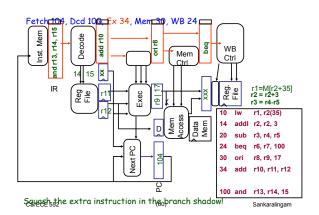

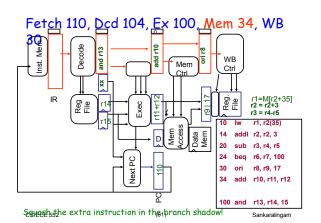

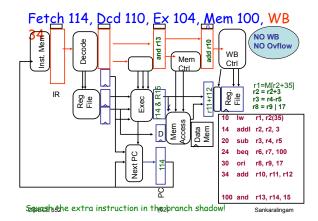

#### Visualizing the pipeline

10 r1, r2(35) lw r2, r2, 3 14 addl

20 sub r3, r4, r5

r6, r7, 100 24 beq

30 r8, r9, 17 ori

34 add r10, r11, r12 these addresses are octal

100 and r13, r14, 15

13

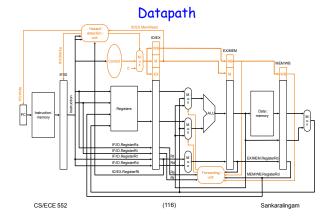

#### Outline

- · Pipeline Datapath

- Under simplifying assumptions

- · All independent instructions

- Talked about bypassing/forwarding

- Datapath not capable of handling forwarding yet

- Walk-through

- Delayed branches

- Control

- Most complicated (read irregular/unstructured)

- Gets more complicated for pipelined processors

- · But we'll start with a simple case

CS/ECE 552 (63) Sankaralingam

#### Pipeline Control vs. Single cycle control

- Similarity

- Replicated functional units like single-cycle implementation

- · Imem and Dmem

- · Separate adder for PC+SX(Imm ) computation

- · What about

- PCWrite? IR-write?

- Write enable for the pipeline registers?

CS/ECE 552 (65) Sankaralingam

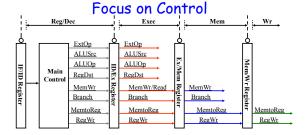

The Main Control generates the control signals during Reg/Dec

CS/ECE 552

- Control signals for Exec (ExtOp, ALUSrc, ...) are used 1 cycle later

Control signals for Mem (MemWr Branch) are used 2 cycles later

Control signals for Wr (MemtoReg MemWr) are used 3 cycles later

Sankaralingam

#### Generating controls

- · We just simplified the problem

- Reduced pipeline control to single-cycle control (Almost)

- Generate controls once

- Consume (i.e., use and discard) signals as you proceed along the pipeline stages

- Identify Stage of consumption for all control signals

CS/ECE 552 (68) Sankaralingam

17

#### Meaning of controls RegWr: 1-> write, 0-> no write MemToReg: 1-> MDR, 0-> ALUOut RegDst: 1->rd, 0->rt ALUOp<1:0>: 00->Add,01->Sub,10->'funct' Exec <3:0> ALUSrc: 0->RegB, 1->SX(Imm) · ExtOp\*\*: --- needed for ORI---• Branch: O->non-branch inst, 1-> branch · MemRead: 1->memread, 0-> no memread · MemWrite: 1->memwrite, 0->no memwrite ALU control abstracted away (as before) - Inputs: ALUop (2 bits), 6 "funct" bits from IR

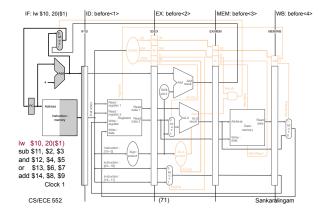

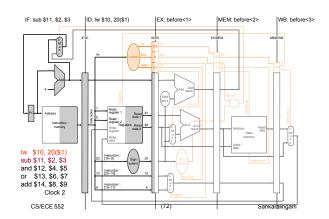

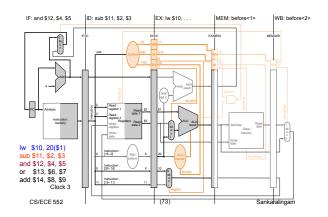

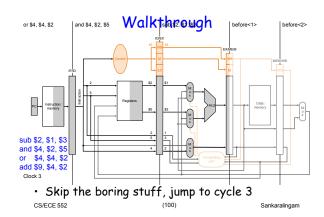

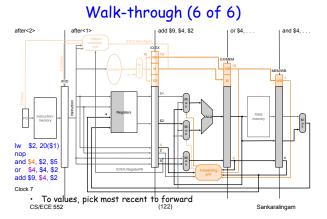

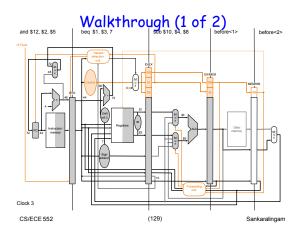

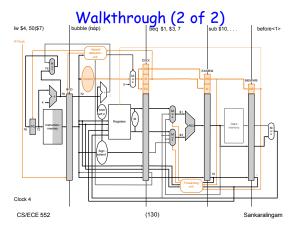

#### Pipeline Walkthrough with controls

- · Use walkthrough worksheets

- Use code segment shown

- Fill in controls

- Interesting stages · Controls generated in Decode

sub \$11, \$2, \$3 and \$12, \$4, \$5 or \$13, \$6, \$7 add \$14, \$8, \$9 · Controls consumed in subsequent stages

lw \$10, 20(\$1)

CS/ECE 552 (69) Sankaralingam CS/ECE 552 (70) Sankaralingam

#### Implementing Pipeline control

- How do we design the control logic block?

- Similar to single-cycle implementation

- Derive logic expressions

- E.g. MemtoReg = Iw

- · ALUSrc = Iw OR sw

- RegWrite = R-type OR lw

- Implement Combinational logic

- PLA implementation

- · ROM implementation

CS/ECE 552 (80) Sankaralingam

#### Pipeline registers

- · Preliminary estimates

- IF/ID: IR (32), PC+4 (32): 64 bits

- ID/EX: IR (32), PC+4 (32) + RegA + RegB: 128 bits

- EX/MEM: ALUout(32) + zero(1) + PC+4+SX(imm) (32): 97

- MEM/WB: ALUout (32) + MemData(32) : 64

- · Corrections:

- ALUout and MemData

- Destination register (5 bits)

- Other control bits (IR not going through)

#### Implementing Pipeline Control

- Exercise

- Compute required bit-width of pipeline registers

- Before the next lecture (NOT Feb 23rd)

CS/ECE 552 (81) Sankaralingam CS/ECE 552 (82) Sankaralingam

#### Summary

- Only slightly more complicated than single cycle

- not really, only because we:

- ignored complications of forwarding, branch prediction, pipeline bubbles, squashing mispredicted instructions (after branches)

- Need deeper understanding of hazards

- · need to modify datapath as well

CS/ECE 552 (83) Sankaralingam

#### Next

- · Pipeline datapath and control assuming independent instructions (no hazards)

- · Data hazards

- Types

CS/ECE 552

- Detecting RAW hazards

- Handling RAW hazards (Partial)

- Datapath

- · Control behavior

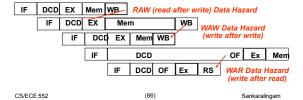

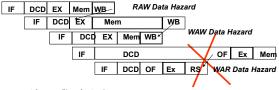

#### Data Hazards

- · Challenge: maintain illusion of sequential execution

- Types of data hazards

- RAW, WAR, WAW

(85)

Sankaralingam

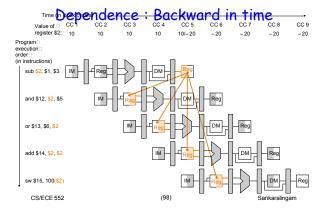

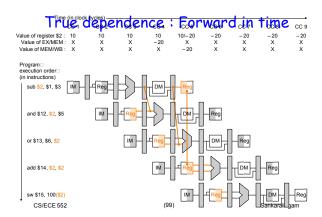

#### Data Hazards

- · Avoid some "by design"

- eliminate WAR by always fetching operands early (DCD) in

- eleminate WAW by doing all WBs in order (last stage, static)

- Detect and resolve remaining ones

- stall or forward (if possible)

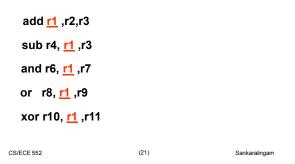

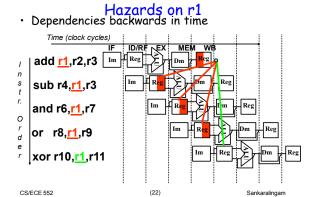

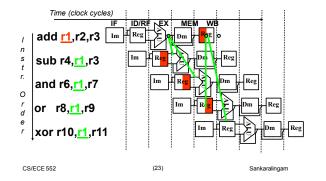

CS/ECE 552 Sankaralingam Hazards on r1

Dependencies backwards in time

#### Data Hazard Solution

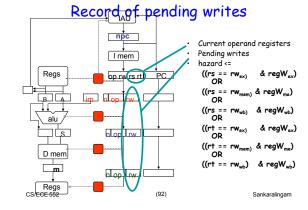

#### Handling RAW Hazards

- · Pre-requisite for handling RAW hazard

- Detection!

- Need to know:

- · Pending writes

- available results that haven't been written back to registers

- · Operand Reads

- Later instructions that potentially use these values

- Instructions may not write to register file (store, branch)

CS/ECE 552 (90) Sankaralingam

#### Detecting RAW hazards

- Suppose instruction i is about to be issued and a predecessor instruction j is in the instruction pipeline.

- A RAW hazard exists on register  $\rho$  if  $\rho \in \text{Rregs}(i) \cap \text{Wregs}(j)$

- Keep a record of pending writes (for inst's in the pipe) and compare with operand regs of current instruction.

- When instruction issues, reserve its result register.

- When on operation completes, remove its write reservation.

- A WAW hazard exists on register  $\rho$  if  $\rho \in \text{Wregs}(i) \cap \text{Wregs}(j)$  A WAR hazard exists on register  $\rho$  if  $\rho \in \text{Wregs}(i) \cap \text{Rregs}(j)$

CS/ECE 552 (91) Sankaralingam

#### Logic equations for Hazard Detection

- · Restatement of equations

- · Text book version

- WB stage is not really a hazard

- Data is written in first half of cycle, read in 2<sup>nd</sup> half

- EX/MEM.RegisterRd = ID/EX.RegisterRs

- EX/MEM.RegisterRd = ID/EX.RegisterRt

- MEM/WB.RegisterRd = ID/EX.RegisterRs

- MEM/WB.RegisterRd = ID/EX.RegisterRt

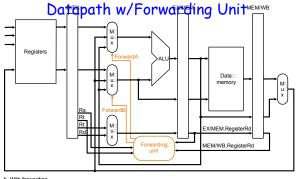

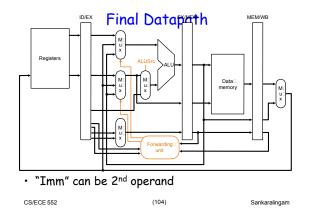

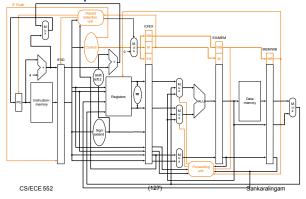

#### Lookahead: Forwarding datapath

- · We know how to detect RAW hazards

- Now.

- Modify Datapath to enable forwarding

- Desired control behavior

CS/ECE 552 (93) Sankaralingam CS/ECE 552 (94) Sankaralingam

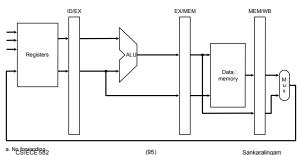

#### Base Pipelined Datapath

- · Simplified representation of pipelined datapath

- To avoid clutter

cs/EEQs;wardA/ForwardB:(9Q1->Mem, 10->EX<sub>Sankaralingam</sub>

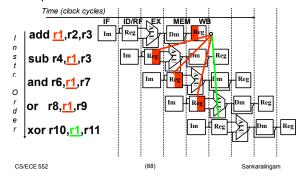

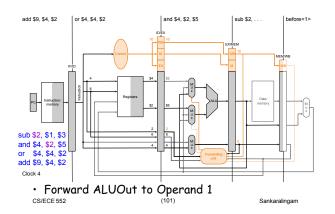

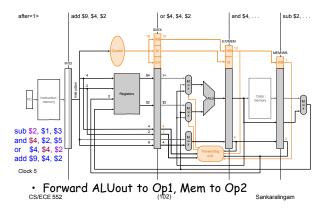

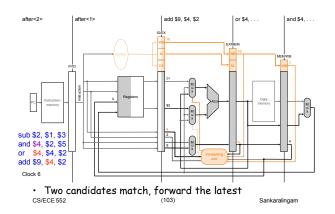

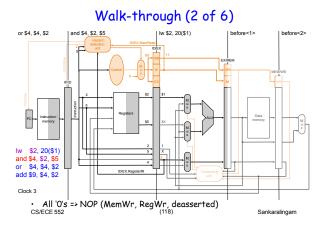

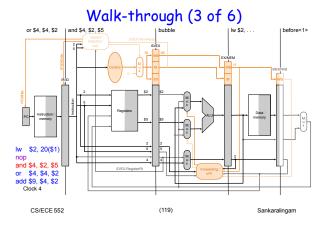

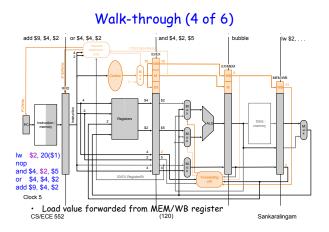

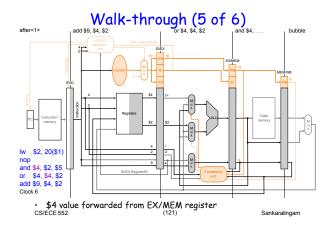

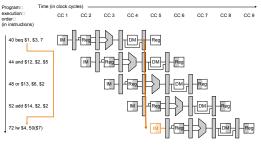

## Data Hazards and Forwarding: Walkthrough

- · Code snippet

- identify hazardsidentify forwarding paths

sub \$2, \$1, \$3 and \$4, \$2, \$5 or \$4, \$4, \$2 add \$9, \$4, \$2

CS/ECE 552 (97) Sankaralingam

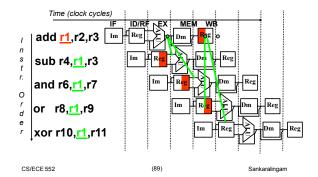

## Forwarding Control Behavior • EX hazard

If (EX/MEM.RegWrite AND // not store or branch EX/MEM.RegsterRd != 0 AND // Result is used EX/MEM.RegisterRd = ID/EX.RegisterRs) ForwardA = 10

If (EX/MEM.RegWrite AND EX/MEM.RegsterRd != 0 AND EX/MEM.RegisterRd = ID/EX.RegisterRt) ForwardB = 10

CS/ECE 552 (105) Sankaralingam CS/ECE 552 (106) Sankaralingam

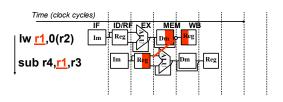

#### Lookahead: RAW hazard with load

- · Forwarding as solution to RAW hazard

- possible if no (true) dependence going backwards in time

- True for R-type instructions

- Data available after EX stage (i.e., at ALUOut)

- Not true for load instruction

CS/ECE 552 (107) Sankaralingam

Forwarding Control Behavior

MEM/WB.RegisterRd = ID/EX.RegisterRs)

MEM/WB.RegisterRd = ID/EX.RegisterRt)

If (MEM/WB.RegWrite AND

MEM/WB.RegsterRd != 0 AND

MEM/WB.RegsterRd != 0 AND

· Does this fully meet our requirements?

ForwardA = 01

ForwardB = 01

If (MEM/WB.RegWrite AND

#### Solution

- · Catch-all solution for hazards

- Stall

- · always works, but hurts performance

- · Use as last resort

- · Challenge:

- Modify pipeline implementation to support stalls when hazards are detected

CS/ECE 552 (109) Sankaralingam

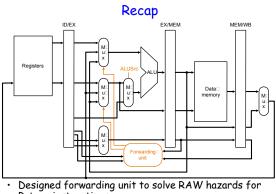

Designed forwarding unit to solve RAW hazards for R-type instructions

CS/ECE 552 (110) Sankaralingam

####

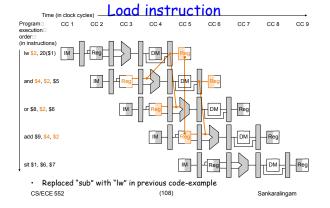

#### Hazards with load instruction

- · True dependencies: backward in time

- · Stall the pipeline

- · Minor change in terminology

- If forwarding can solve it, it is not a hazard!

- "Hazard" refers only to true backward dependencies in time.

CS/ECE 552 (112) Sankaralingam

#### Handling the hazard

- · As before

- Detection

- · Logic equations to detect hazard

- Actual stalling

- Datapath/control modifications to achieve stalling

#### Detection

lw \$2, 20(\$1) and \$4, \$2, \$5 or \$4, \$4, \$2

add \$9, \$4, \$2

- · Conditions

- Preceding instruction must read memory

- · MemRead must be asserted

- Destination of preceding instruction (rt) must be one of operands of current instruction

- Logic equations- restate above conditions formally

- If( ID/EX.MemRead AND

((ID/EX.RegRt = IF/ID.RegRs) OR

(ID/EX.RegRt = IF/ID.RegRt)))

STALL

CS/ECE 552 (113) Sankaralingam CS/ECE 552 (114) Sankaralingam

#### Stalling the pipeline

- · Instruction cannot proceed

- Following instruction must be stalled too.

- Otherwise state in pipeline registers is overwritten

- · Preceding instructions may proceed as usual

- Solution

- inject NOP into EX/Mem pipeline

- Prevent writes to PC to IF/ID register

CS/ECE 552 (115) Sankaralingam

###

#### RAW Hazard with Loads: Summary

- · True backward dependencies in time

- Need to stall

- Stall achieved by

- Detecting hazard (remember logic equation)

- Inserting NOP (all EX/MEM/WB controls set to 0)

- Preventing IF/ID register and PC from being overwritten

- · Next Branch/Control Hazards

CS/ECE 552 (123) Sankaralingam

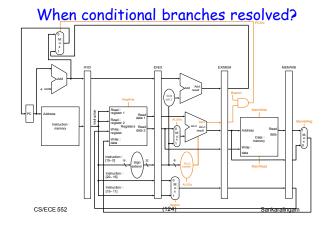

#### Branch Hazards

- Branch resolved in the MEM stage

- If taken,

PC-PC+4+SX(Imm\*4)

40+4+7\*4=72

CS/ECE 552 (125) Sankaralingam

#### Control/Branch Hazards

- · Branch resolved in the MEM stage

- But next instruction has to fetched in the next cycle

- Reduce the penalty by moving decision earlier in pipeline

- · Need additional comparator (r1=r2?) and adder (PC+4+SX(IMM)\*4)

- Reduced penalty from 3 cycles to 1 cycle

CS/ECE 552 (126) Sankaralingam

#### Datapath for branch hazards

#### Eliminate 1-cycle stall?

- Two solutions

- Predict branch is always not taken

- · More sophisticated prediction schemes

- Delay slots

- · Compiler's problem

- · Walkthrough example for solution #1

- Predict not taken

(128) CS/ECE 552 Sankaralingam

#### **Dynamic Branch Prediction**

- · Better than static prediction

- Branches are predictable

- $\sim$ 90% of program execution time is spent in

- ~10% of code (inner loops)

- Think of a program loop of N iterations

- · Taken N-1 times

- · Not taken last time

CS/ECE 552 (131) Sankaralingam

## Dynamic Branch Prediction Taken Predict taken Predict taken Predict taken Taken Not taken Predict not taken Predict not taken Predict not taken Taken Not taken

- · How does hardware "learn" branch behavior?

- Store each branch instruction's history \*\*\*

- If a branch was taken "recently", predict taken

- · One bit saturating counter

- Two bit counters

CS/ECE 552 (132)

33

Sankaralingam

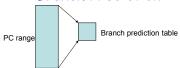

#### **Branch Prediction**

- Store each branch's history \*\*\*

- Not really

CS/ECE 552

- Keep a small table indexed by program counter

- PC is large (32 bit number)

- Mapping to number of table entries

- E.g. 16-entry branch prediction table

- Mapping: use last 4 bits of PC

- Problem: Multiple branches may map to same entry in table --Aliasina

(133)

Sankaralingam

#### "Easy way"\* to hide branch hazard delay

add \$s1, \$s2, \$s3

if \$s2 = 0 then::-

Delay slot

(134)

Delayed branch

Instruction after branch always executes

- Find an independent instruction from before the branch

Find instructions from Taken (target) OR from Not Taken (fallthrough) code section

R from (fallode (fall-

From target

0. From fall through

add \$81, \$32, \$33.

d3 \$1, \$32, \$33.

d3 \$1, \$32, \$33.

d5 \$1 = 0 then:

Delay slot

Becomes

Becomes

\* For Architects

CS/ECE 552

Sankaralingam

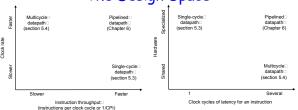

## Big picture

- Iron law: Insts/prog \* CPI \* cycletime

- · With pipelining:

- CPI ~ 1 (with ideal memory, good branch prediction and few data hazards)

- Cycletime: determined by critical path of one stage

The Design Space

- Summary of design trade-offs

- · Can we do better?

- CPI < 1?

- i.e., IPC > 1?

CS/ECE 552 (135) Sankaralingam CS/ECE 552 (136) Sankaralingam

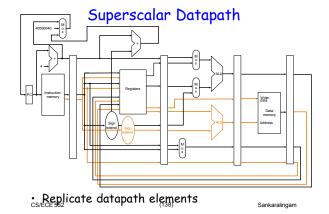

#### Superscalar Processor

- · What does it mean?

- Scalar processors (operate on scalar quantities)

- Vector (operate on vectors)

- Superscalar: multiple scalar operations in one cycle

- More than one instruction per cycle

CS/ECE 552 (137) Sankaralingam

#### Dynamic Scheduling

- No need to suffer hazards if other useful work can be achieved

- · Load Hazard results in pipeline stall

- But other instructions are ready

- "Oh! But we cannot execute instructions out of order" Not really

lw \$t0, 20(\$s2) addu \$t1, \$t0, \$t2 sub \$s4, \$s4, \$t3 slti \$t5, \$s4, \$t3

CS/ECE 552 (139) Sankaralingam

## Dynamic Scheduling Instruction fetch and decode unit Reservation station Reservation station Floating point Commit unit In-order issue In-order issue

- Instructions can execute when operands are ready

- Instructions can "commit" when all preceding instructions have committed

CS/ECE 552 (140) Sankaralingam

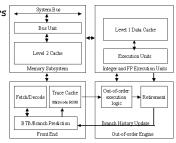

#### Pentium 4 on 0.18 micron

- 42 million transistors

- · 3GHz

- Several parts are clocked at half the speed

- Inorder front-end, out-of-order execution, in order retire

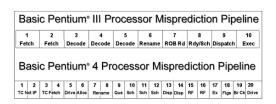

#### Pentium 4 pipeline

· Pipeline too much; c.f., Core2

CS/ECE 552 (141) Sankaralingam CS/ECE 552 (142) Sankaralingam