Problem 4:

- 2. ALUop = 00 Instruction = 010100

- NewPC = PC+4

Path = PC to ADD to branch-mux to jump-mux to PC

- 4. WrReg-mux = 2 or 0 ALU-mux = 20 Mem/ALU-mux = X Branch-mux = PC+4 Jump-mux = PC+4

- ALU = -3 and 20 Add (PC+4) = PC and 4 Add (branch) = PC+4 and 20\*4

- ReadReg 1 = 3 ReadReg 2 = 2 WriteReg = 2 or 0 WriteData = X RegWrite = 0

## Problem 5:

- 1. Pipelined = 350ps Single-Cycle = 1250 ps

- 2. Pipelined = 1750ps Single-Cycle = 1250

- Stage to split = ID New Cycle Time = 300ps

- 4. 35%

- 5. 65%

- 6. Multi-cycle execution time is 4.2 times pipelined execution Single-cycle execution time is 3.57 times pipelined execution

Problem 6:

- RAW on R1 from I1 to I2 and I3 RAW on R2 from I2 to I3 WAR on R2 from I1 to I2 WAR on R1 from I2 to I3 WAW on R1 from I1 to I3

- 2. Add 2 NOPs between each instruction for RAW hazards on R1 and R2

- 3. No hazards

- No forwarding = 1980ps

Forwarding = 1680ps

Speedup = 1.18

- 5. No NOPs needed

- No forwarding = 1980ps ALU-ALU forwarding = 1470ps Speedup = 1.35

Problem 7:

- RegWrite = 1

MemRead = 0

ALUMux = 0

MemWrite = 0

ALUop = AND

RegMux = 0

Branch = 0

- 2. All except data memory, immediate sign-extender, and branch adder

- Not used = branch adder No output = data memory

Problem 8:

Easiest = "bit equal" - would only need an optional negation after the xor

Medium = "replace under mask" – would require new function for ALU

Hard = "split register" – This requires writing two registers which would require an additional data path through many of the stages and an additional write port for the register file

## Problem 9:

Problem 10:

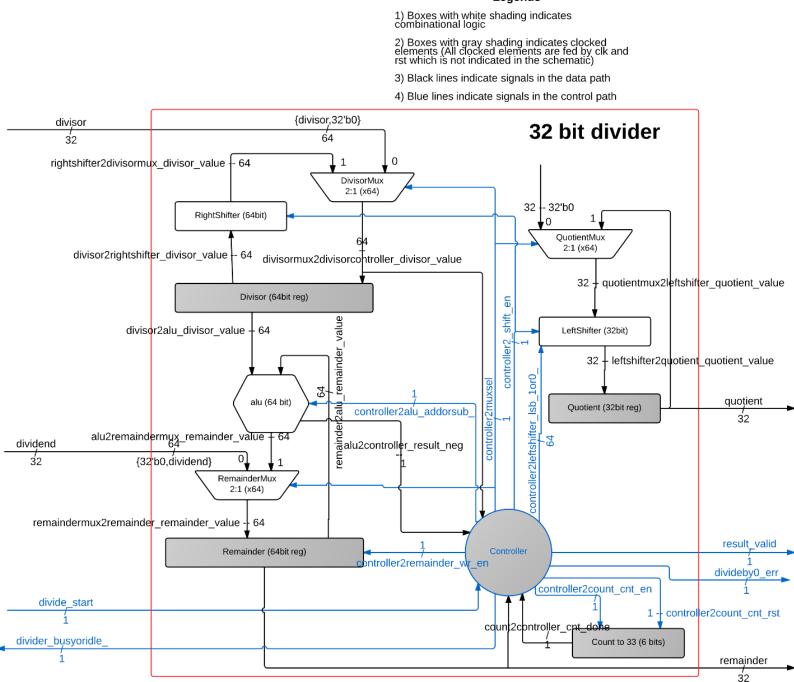

## Legends

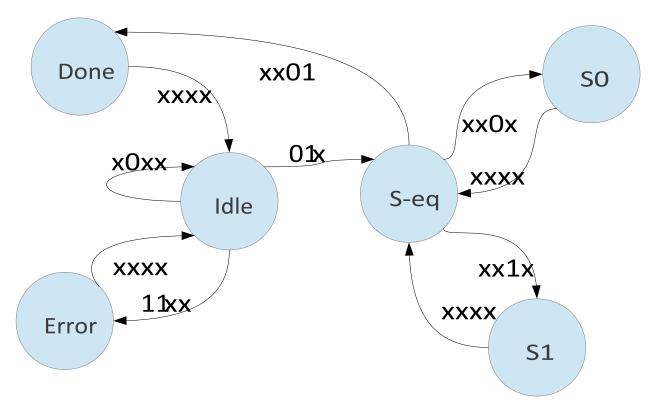

State Machine:

Inputs: (divisor==0, divide\_start, remainder<0, count2controller\_cnt\_done)</pre>

## Problem 10 Controller Truth Table

|                                        | Statę machine outputs |               |              |                         |                          |                                   |                           |                            |                   |                      |

|----------------------------------------|-----------------------|---------------|--------------|-------------------------|--------------------------|-----------------------------------|---------------------------|----------------------------|-------------------|----------------------|

| Moore state machine's<br>current state | divider_bus yoridle_  | divideby0_err | result_valid | controller2count_cnt_en | controller2count_cnt_rst | controller2lefts hifter_ls b_1or0 | controller2alu_addors ub_ | controller2remainder_wr_en | controller2muxsel | controller2_shift_en |

| Idle                                   | 0                     | 0             | 0            | 0                       | 1                        | 0                                 | х                         | 1                          | 0                 | 0                    |

| Error                                  | 1                     | 1             | 1            | х                       | х                        | х                                 | х                         | х                          | х                 | x                    |

| Done                                   | 1                     | 0             | 1            | х                       | х                        | х                                 | х                         | х                          | х                 | х                    |

| S-eq                                   | 1                     | 0             | 0            | 0                       | 0                        | х                                 | 0                         | 1                          | 1                 | 0                    |

| SO                                     | 1                     | 0             | 0            | 1                       | 0                        | 1                                 | х                         | 0                          | 1                 | 1                    |

| S1                                     | 1                     | 0             | 0            | 1                       | 0                        | 0                                 | 1                         | 1                          | 1                 | 1                    |