${ \begin{tabular}{l} {\rm Copyright}\\ {\rm by}\\ {\rm Karthikeyan\ Sankaralingam}\\ {\rm 2006} \end{tabular} }$

The Dissertation Committee for Karthikeyan Sankaralingam certifies that this is the approved version of the following dissertation:

## Polymorphous Architectures: A Unified Approach for Extracting Concurrency of Different Granularities

| Comr  | nittee:                    |

|-------|----------------------------|

| Stepl | nen W. Keckler, Supervisor |

| Sama  | an Amarasinghe             |

| Jame  | s C. Browne                |

| Doug  | las C. Burger              |

| Н. Р  | eter Hofstee               |

| Willi | am R. Mark                 |

# Polymorphous Architectures: A Unified Approach for Extracting Concurrency of Different Granularities

by

Karthikeyan Sankaralingam, B.Tech., M.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2006

## Acknowledgments

"At times our own light goes out and is rekindled by a spark from another person. Each of us has cause to think with deep gratitude of those who have lighted the flame within us."

-Albert Schweitzer

Many people have contributed to my dissertation research and my experience at UT. I would like to first thank my advisor, Steve Keckler, for his advice, guidance, and training that helped me get to this point in my graduate career. Thanks also for paying me during more than seven years of graduate school and bringing me to Austin. Steve Keckler and Doug Burger provided the vision, constant encouragement and technical expertise that made this dissertation possible. Steve has been an excellent mentor and thesis advisor and I cannot thank him enough for the influence he has had on me.

Doug Burger, as the co-leader of the CART group, and a de-facto coadvisor for my dissertation research has also played an important part in my professional development. I am thankful for the numerous opportunities I have had to interact with him, and for his many insightful comments on topics ranging from microarchitecture pipelines to brewing beer.

The students in the CART lab have been incredible and made graduate school life always exciting. I would like to thank them for their feedback on my research, attending many of my practice talks, proofreading my papers, and

iv

indulging in numerous technical and non-technical discussions that kept me entertained, informed, and always provoked my thinking. Thanks especially to Vikas Agarwal, Hrishi, Changkyu Kim, Kartik Agaram, Simha Sethumadhavan, Raj Desikan, and Heather Hanson for their inputs on all topics of research and life in general. Thanks to Maria Jump and Alison Norman for attending numerous practice talks and giving their perspective on my research. Thanks to Heather Hanson and Kartik Agaram for carefully proof-reading this document and riding me of my under-hyphenation disease.

I would especially like to thank Ramadass Nagarajan with whom I collaborated closely through all my years in graduate school. I have thoroughly enjoyed working together with him and could not have asked for a better collaborator. Starting from our initial work on writing a PowerPC port of the SimpleScalar simulator, to our late night brainstorming discussions on initial ideas for the TRIPS processor, and design and verification of the prototype chip, I have always enjoyed Ramadas's insights and hearing his perspective. We jointly designed the instruction set described in this dissertation and many aspects of the microarchitecture.

I would like to thank the staff in the Computer Sciences department for helping navigate graduate school bureaucracy and shielding me from most of it. The facilities staff in the department were outstanding, and the rare times they exposed their BOFH side to me were completely justified! I would like to thank Gem Naivar for helping with graduate school miscellany, several travel issues, and her immense patience and tolerance.

v

Last, but not the least, I would like thank my family. My mother and my brother provided me with the constant encouragement necessary for success in graduate school and I could not have done it without them. Thanks Mom for your infinite patience and never asking me when I was going to graduate! Thanks Ranga for putting up with me as a roommate for two years and tolerating all my eccentricities as a kid brother for 28 years. Thanks Dad for your words of wisdom and challenging me to be the best I could.

I would also like to acknowledge the institutions that helped support my research in graduate school: National Science Foundation for the initial grants that funded me and DARPA for the TRIPS funding.

vi

Polymorphous Architectures: A Unified Approach for Extracting Concurrency of Different Granularities

Publication No.

Karthikeyan Sankaralingam, Ph.D. The University of Texas at Austin, 2006

Supervisor: Stephen W. Keckler

Processor architects today are faced by two daunting challenges: emerging applications with heterogeneous computation needs and technology limitations of power, wire delay, and process variation. Designing multiple application-specific processors or specialized architectures introduces design complexity, a software programmability problem, and reduces economies of scale. There is a pressing need for design methodologies that can provide support for heterogeneous applications, combat processor complexity, and achieve economies of scale. In this dissertation, we introduce the notion of architectural polymorphism to build such scalable processors that provide support for heterogeneous computation by supporting different granularities of parallelism. Polymorphism configures coarse-grained microarchitecture blocks to provide an adaptive and flexible processor substrate. Technology scalability is achieved by designing an architecture using scalable and modular microarchitecture blocks.

We use the dataflow graph as the unifying abstraction layer across three granularities of parallelism-instruction-level, thread-level, and data-level. To first order, this granularity of parallelism is the main difference between different classes of applications. All programs are expressed in terms of dataflow graphs and directly mapped to the hardware, appropriately partitioned as required by the granularity of parallelism. We introduce Explicit Data Graph Execution (EDGE) ISAs, a class of ISAs as an architectural solution for efficiently expressing parallelism for building technology scalable architectures.

We developed the TRIPS architecture implementating an EDGE ISA using a heavily partitioned and distributed microarchitecture to achieve technology scalability. The two most significant features of the TRIPS microarchitecture are its heavily partitioned and modular design, and the use of microarchitecture networks for communication across modules. We have also built a prototype TRIPS chip in 130nm ASIC technology composed of two processor cores and a distributed 1MB Non-Uniform Cache Access Architecture (NUCA) on-chip memory system.

Our performance results show that the TRIPS microarchitecture which provides a 16-issue machine with a 1024-entry instruction window can sustain good instruction-level parallelism. On a set of hand-optimized kernels IPCs in the range of 4 to 6 are seen, and on a set of benchmarks with ample data-level parallelism (DLP), compiler generated code produces IPCs in the range of 1 to 4. On the EEMBC and SPEC CPU2000 benchmarks we see IPCs in the range of 0.5 to 2.3. Comparing performance to the Alpha 21264, which is a

vii

viii

high performance architecture tuned for ILP, TRIPS is up to 3.4 times better on the hand optimized kernels. However, compiler generated binaries for the DLP, EEMBC, and SPEC CPU2000 benchmarks perform worse on TRIPS compared to an Alpha 21264. With more aggressive compiler optimization we expect the performance of the compiler produced binaries to improve.

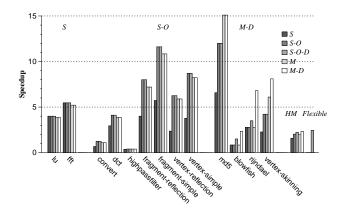

The polymorphous mechanisms proposed in this dissertation are effective at exploiting thread-level parallelism and data-level parallelism. When executing four threads on a single processor, significantly high levels of processor utilization are seen; IPCs are in the range of 0.7 to 3.9 for an application mix consisting of EEMBC and SPEC CPU2000 workloads. When executing programs with DLP, the polymorphous mechanisms we propose provide harmonic mean speedups of 2.1X across a set of DLP workloads, compared to an execution model of extracting only ILP. Compared to specialized architectures, these mechanisms provide competitive performance using a single execution substrate.

ix

## Table of Contents

| Ackno    | ow ledgments                         | i  |

|----------|--------------------------------------|----|

| Abstra   | act                                  | vi |

| List of  | f Tables                             | χV |

| List of  | f Figures x                          | vi |

| Chapt    | er 1. Introduction                   |    |

| 1.1      | Principles of Polymorphism           |    |

| 1.2      | System Design                        | ļ  |

|          | 1.2.1 Granularity of Processors      | ļ  |

|          | 1.2.2 Granularity of Parallelism     |    |

|          | 1.2.3 Technology Scalability         |    |

| 1.3      | TRIPS Architecture                   | 1  |

| 1.4      | Implementation of Polymorphism       | 13 |

| 1.5      | Thesis Statement                     | 1  |

| 1.6      | Dissertation Contributions           | 1  |

| 1.7      | Dissertation Organization            | 1  |

| Chapt    | er 2. Related Work                   | 2  |

| 2.1      | Polymorphism                         | 2  |

| $^{2.2}$ | Data Parallel Architectures          | 2  |

| 2.3      | Scalable Architectures               | 3  |

| 2.4      | Microarchitecture Techniques for ILP | 3  |

Х

| Chapte                       | er 3. EDGE ISAs                                                                                                                                    | 36                                      | 5.3.2 Control Flow                                                  | 95                                                   |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------|------------------------------------------------------|

| 3.1                          | EDGE ISAs                                                                                                                                          | 37                                      | 5.3.3 Data Storage                                                  | 96                                                   |

| 3.2                          | Execution Model                                                                                                                                    | 38                                      | 5.3.4 Summary                                                       | 97                                                   |

|                              | 3.2.1 Block Execution                                                                                                                              | 40                                      | 5.4 Instruction-Level Parallelism                                   | 100                                                  |

|                              | 3.2.2 Key Advantages                                                                                                                               | 41                                      | 5.4.1 Execution Core Management                                     | 100                                                  |

| 3.3                          | Compilation                                                                                                                                        | 43                                      | 5.4.2 Control Flow Management                                       | 102                                                  |

| 3.4                          | $Summary \dots \dots$                        | 46                                      | 5.4.3 Data Storage Management                                       | 105                                                  |

| ~· .                         |                                                                                                                                                    |                                         | 5.5 Thread-Level Parallelism                                        | 107                                                  |

| _                            | er 4. TRIPS Architecture and Prototype Chip                                                                                                        | 48                                      | 5.5.1 Execution Core Management                                     | 108                                                  |

| 4.1                          | The TRIPS ISA                                                                                                                                      | 50                                      | 5.5.2 Control Flow Management                                       | 111                                                  |

|                              | 4.1.1 TRIPS Blocks                                                                                                                                 | 50                                      | 5.5.3 Data Storage Management                                       | 112                                                  |

|                              | 4.1.2 Direct Instruction-Instruction Communication                                                                                                 | 52                                      | 5.6 Data-Level Parallelism                                          | 113                                                  |

|                              | TRIPS Microarchitecture Principles                                                                                                                 | 53                                      | 5.6.1 Execution Core Management                                     | 114                                                  |

| 4.3                          | TRIPS Microarchitecture Implementation                                                                                                             | 55                                      | 5.6.2 Control Flow Management                                       | 115                                                  |

|                              | 4.3.1 Global Control Tile (GT)                                                                                                                     | 62                                      | 5.6.3 Data Storage Management                                       |                                                      |

|                              | 4.3.2 Instruction Tile (IT)                                                                                                                        | 63                                      | 5.7 Discussion                                                      |                                                      |

|                              | 4.3.3 Register Tile (RT)                                                                                                                           | 64                                      |                                                                     |                                                      |

|                              | 4.3.4 Execution Tile (ET)                                                                                                                          | 65                                      | Chapter 6. Performance Evaluation: ILP                              | 120                                                  |

|                              | 4.3.5 Data Tile (DT)                                                                                                                               | 65                                      | 6.1 Methodology                                                     | 121                                                  |

|                              | 4.3.6 Secondary Memory System                                                                                                                      | 67                                      | 6.2 Benchmarks                                                      | 122                                                  |

| 4.4                          | Microarchitecture Execution Model                                                                                                                  | 68                                      | 6.3 Results                                                         | 125                                                  |

| 4.5                          | TRIPS Prototype Chip                                                                                                                               | 73                                      | 6.3.1 Microbenchmarks                                               | 125                                                  |

|                              | 4 E 1 Chia Caraifantian                                                                                                                            |                                         | 000 D : D : N. T                                                    | 10=                                                  |

|                              | 4.5.1 Chip Specifications                                                                                                                          | 74                                      | 6.3.2 Data Parallel Kernels                                         | 127                                                  |

|                              | 4.5.2 Physical Design                                                                                                                              | 74<br>79                                | 6.3.2 Data Parallel Kernels 6.3.3 EEMBC and SPEC CPU2000 Benchmarks |                                                      |

|                              | • •                                                                                                                                                |                                         |                                                                     | 131                                                  |

| 4.6                          | 4.5.2 Physical Design                                                                                                                              | 79                                      | 6.3.3 EEMBC and SPEC CPU2000 Benchmarks 6.4 Summary                 | 131                                                  |

|                              | 4.5.2 Physical Design4.5.3 Design Analysis                                                                                                         | 79<br>80                                | 6.3.3 EEMBC and SPEC CPU2000 Benchmarks 6.4 Summary                 | 131<br>132<br><b>135</b>                             |

|                              | 4.5.2 Physical Design                                                                                                                              | 79<br>80<br>82                          | 6.3.3 EEMBC and SPEC CPU2000 Benchmarks 6.4 Summary                 | 131<br>132<br><b>135</b>                             |

| 4.7<br>Chapte                | 4.5.2 Physical Design 4.5.3 Design Analysis  My Contributions  Discussion  Polymorphism in the TRIPS Architecture                                  | 79<br>80<br>82                          | 6.3.3 EEMBC and SPEC CPU2000 Benchmarks 6.4 Summary                 | 131<br>132<br><b>135</b><br>137                      |

| 4.7<br>Chapte                | 4.5.2 Physical Design         4.5.3 Design Analysis         My Contributions         Discussion                                                    | 79<br>80<br>82<br>83                    | 6.3.3 EEMBC and SPEC CPU2000 Benchmarks 6.4 Summary                 | 131<br>132<br><b>135</b><br>137<br>137               |

| 4.7<br><b>Chapt</b> 6<br>5.1 | 4.5.2 Physical Design 4.5.3 Design Analysis  My Contributions  Discussion  Polymorphism in the TRIPS Architecture                                  | 79<br>80<br>82<br>83                    | 6.3.3 EEMBC and SPEC CPU2000 Benchmarks 6.4 Summary                 | 131<br>132<br><b>135</b><br>137<br>137<br>139        |

| 4.7<br>Chapte<br>5.1<br>5.2  | 4.5.2 Physical Design 4.5.3 Design Analysis  My Contributions Discussion  Par 5. Polymorphism in the TRIPS Architecture Principles of Polymorphism | 79<br>80<br>82<br>83<br><b>85</b><br>89 | 6.3.3 EEMBC and SPEC CPU2000 Benchmarks 6.4 Summary                 | 131<br>132<br><b>135</b><br>137<br>137<br>139<br>140 |

xii

xi

|        | 7.2.2 | EEMBC Benchmarks                             | 155 |

|--------|-------|----------------------------------------------|-----|

|        | 7.2.3 | Data Parallel Benchmarks                     | 161 |

| 7.3    | Sumn  | nary                                         | 168 |

| Chapt  | er 8. | Data-Level Parallelism                       | 173 |

| 8.1    | DLP   | Overview and History                         | 174 |

| 8.2    | Appli | ication Behavior                             | 178 |

|        | 8.2.1 | Program Attributes                           | 178 |

|        | 8.2.2 | Benchmark Attributes                         | 183 |

| 8.3    | Micro | parchitecture Analysis                       | 187 |

|        | 8.3.1 | Methodology                                  | 187 |

|        | 8.3.2 | Analysis                                     | 189 |

|        | 8.3.3 | Summary                                      | 192 |

| 8.4    | Data- | Parallel Microarchitectural Mechanisms       | 194 |

|        | 8.4.1 | Memory System Mechanisms                     | 194 |

|        | 8.4.2 | Instruction Fetch and Control Mechanisms     | 197 |

|        | 8.4.3 | Execution Core Mechanisms                    | 200 |

|        | 8.4.4 | Summary                                      | 201 |

| 8.5    | Resul | lts                                          | 203 |

|        | 8.5.1 | Simulation Methodology                       | 204 |

|        | 8.5.2 | Baseline TRIPS Performance                   | 205 |

|        | 8.5.3 | Configuration of Mechanisms                  | 206 |

|        | 8.5.4 | Performance Evaluation                       | 208 |

|        | 8.5.5 | Comparison Against Specialized Architectures | 211 |

| 8.6    | Sumn  | nary                                         | 214 |

| Chapte | er 9. | Conclusions                                  | 217 |

| 9.1    | Sumn  | nary                                         | 217 |

| 9.2    | Discu | ssion                                        | 221 |

|        | 9.2.1 | VLSI Design Complexity                       | 222 |

|        | 9.2.2 | Software Complexity                          | 226 |

|        | 9.2.3 | Technology Constraints                       | 228 |

| 9.3    | Final | Thoughts                                     | 229 |

| App endices                                        | 232 |

|----------------------------------------------------|-----|

| Appendix A. tsim-proc and GPA simulator comparison | 233 |

| A.1 Description                                    | 234 |

| A.2 Results                                        | 236 |

| Appendix B. IPC reduction from speculation depth   | 239 |

| Bibliography                                       | 243 |

| Vita                                               | 271 |

xiii xiw

# List of Tables

| 1.1 | A taxonomy of architectures                                                                                                                                                                                     | 14  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | TRIPS processor micronetworks.                                                                                                                                                                                  | 59  |

| 4.2 | Block execution timeline and micronets used                                                                                                                                                                     | 70  |

| 4.3 | Chip area breakdown                                                                                                                                                                                             | 77  |

| 4.4 | TRIPS Tile Specifications                                                                                                                                                                                       | 81  |

| 5.1 | Summary of polymorphism mechanisms                                                                                                                                                                              | 99  |

| 6.1 | TRIPS processor parameters                                                                                                                                                                                      | 122 |

| 6.2 | List of benchmarks                                                                                                                                                                                              | 123 |

| 6.3 | TRIPS performance results on microbenchmarks                                                                                                                                                                    | 125 |

| 6.4 | Processor performance on DLP kernels                                                                                                                                                                            | 127 |

| 6.5 | Processor performance on EEMBC benchmarks                                                                                                                                                                       | 130 |

| 6.6 | Processor performance on SPEC CPU2000 benchmarks                                                                                                                                                                | 131 |

| 7.1 | Different processor modes simulated                                                                                                                                                                             | 138 |

| 7.2 | Benchmark mix in 2-Thread configuration - SPEC CPU2000 suite. First column is the workload mix number and the second column lists the benchmarks executed concurrently as part of the multiprogrammed workload. | 153 |

| 7.3 | Benchmark mix in 4-Thread configuration - SPEC CPU2000 suite. First column is the workload mix number and the second column lists the benchmarks executed concurrently as part of the multiprogrammed workload  | 154 |

| 7.4 | Benchmark mix in 2-Thread configuration - EEMBC suite. First column is the workload mix number and the second column lists the benchmarks executed concurrently as part of the multiprogrammed workload.        | 159 |

| 7.5 | Benchmark mix in 4-Thread configuration - EEMBC suite. First column is the workload mix number and the second column lists the benchmarks executed concurrently as part of the multiprogrammed workload.        | 160 |

xv

| 7.6 | Benchmark mix in 2-Thread configuration - DLP suite. First column is the workload mix number and the second column lists the benchmarks executed concurrently as part of the multiprogrammed workload. | 166 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.7 | Benchmark mix in 4-Thread configuration - DLP suite. First column is the workload mix number and the second column lists the benchmarks executed concurrently as part of the multiprogrammed workload. | 167 |

| 7.8 | Resource contention: percentage of cycles that the execution tiles are stalled due to a resource conflict                                                                                              | 171 |

| 8.1 | Benchmark description                                                                                                                                                                                  | 184 |

| 8.2 | Benchmark Attributes                                                                                                                                                                                   | 185 |

| 8.3 | Benchmark attributes                                                                                                                                                                                   | 185 |

| 8.4 | Critical path analysis.                                                                                                                                                                                | 189 |

| 8.5 | Data-parallel program attributes and the set of universal microarchitectural mechanisms. Mechanisms in parenthesis indicate TRIPS specific implementations.                                            | 201 |

| 8.6 | Performance on baseline TRIPS                                                                                                                                                                          | 205 |

| 8.7 | Machine configurations                                                                                                                                                                                 | 206 |

| 8.8 | Performance comparison of TRIPS with DLP mechanisms to specialized hardware                                                                                                                            | 212 |

| A.1 | Comparison of GPA simulator to TRIPS simulator on the DLP kernels                                                                                                                                      | 237 |

| A.2 | Comparison of GPA simulator to TRIPS simulator on a set of hand optimized SPEC CPU2000 microbenchmakrs                                                                                                 | 238 |

| B.1 | IPC comparison of ILP-mode and 1-Thread TLP-mode - SPEC CPU2000 suite                                                                                                                                  | 240 |

| B.2 | IPC comparison of ILP-mode and 1-Thread TLP-mode - EEMBC suite                                                                                                                                         | 241 |

| B.3 | IPC comparison of ILP-mode and 1-Thread TLP-mode - DLP suite                                                                                                                                           | 242 |

xvi

# List of Figures

| 1.1  | Granularity of parallel processing elements on a chip. Number<br>of cores that can fit on a typical 65nm high performance chip. | 6   |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

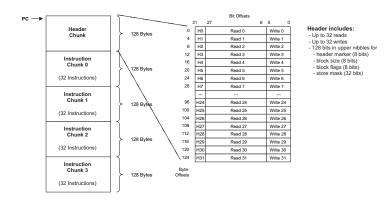

| 4.1  | TRIPS Block Format.                                                                                                             | 51  |

| 4.2  | TRIPS Instruction Formats                                                                                                       | 53  |

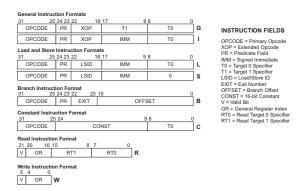

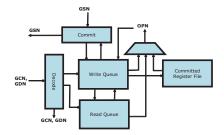

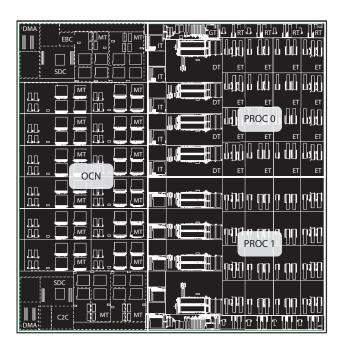

| 4.3  | TRIPS Prototype Chip Schematic                                                                                                  | 56  |

| 4.4  | TRIPS Micronetworks (GRD, DSN, and ESN not shown). $\ \ .$                                                                      | 57  |

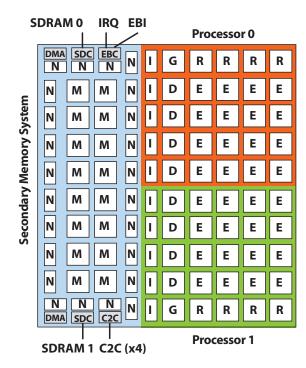

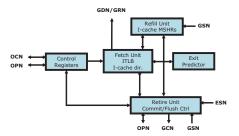

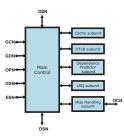

| 4.5  | TRIPS Tile-level Diagrams: Global Tile - GT                                                                                     | 60  |

| 4.6  | TRIPS Tile-level Diagrams: Register Tile - RT                                                                                   | 60  |

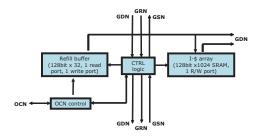

| 4.7  | TRIPS Tile-level Diagrams: Instruction Tile - IT                                                                                | 60  |

| 4.8  | TRIPS Tile-level Diagrams: Data Tile - DT                                                                                       | 61  |

| 4.9  | TRIPS Tile-level Diagrams: Execution Tile - ET $\ \ldots \ \ldots$                                                              | 61  |

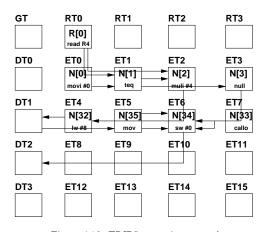

| 4.10 | TRIPS execution example                                                                                                         | 71  |

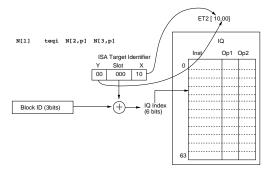

| 4.11 | Encoding of a single instruction and mapping instructions to reservation stations                                               | 72  |

| 4.12 | Floorplan diagram                                                                                                               | 76  |

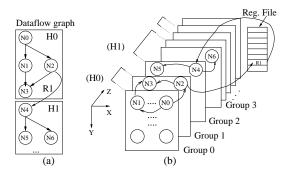

| 5.1  | Execution core management for ILP.                                                                                              | 103 |

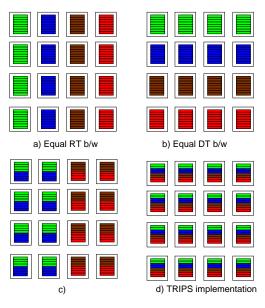

| 5.2  | Partitioning execution core resources to support thread-level parallelism. Each color denotes a different thread                | 109 |

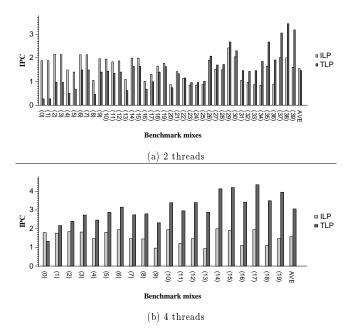

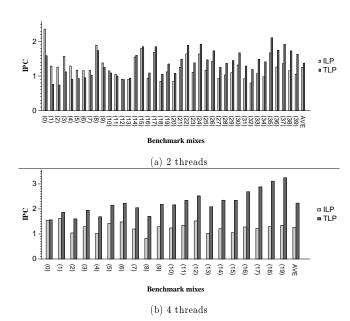

| 7.1  | TLP-mode performance (utilization) - SPEC CPU2000 suite                                                                         | 147 |

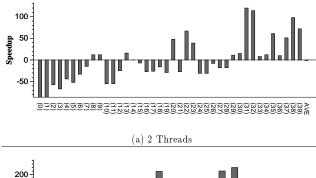

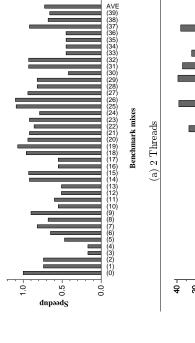

| 7.2  | TLP-mode speedup compared to serialized execution - SPEC CPU2000 suite.                                                         | 150 |

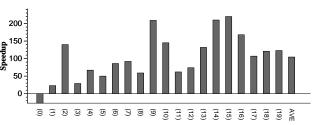

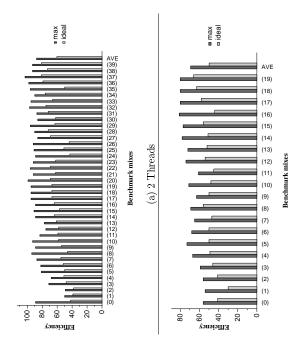

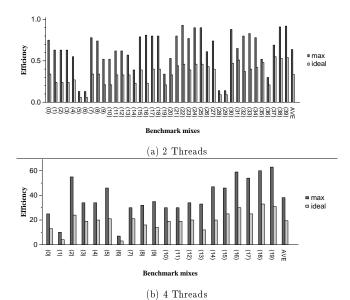

| 7.3  | TLP-mode execution efficiency - SPEC CPU2000 suite                                                                              | 152 |

| 7.4  | TLP-mode performance (utilization) - EEMBC suite                                                                                | 156 |

| 7.5  | TLP-mode speedup compared to serialized execution - EEMBC suite                                                                 | 157 |

| 7.6  | TLP-mode execution efficiency - EEMBC suite                                                                                     | 158 |

| 7.7  | TLP-mode performance (utilization) - DLP suite                                                                                  | 163 |

| 7.8 | TLP-mode speedup compared to serialized execution - DLP suite                                                                                                    | .164     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 7.9 | TLP-mode execution efficiency - DLP suite                                                                                                                        | 165      |

| 7.1 | 0 TLP-mode summary of results. FIXME change to $\%$                                                                                                              | 170      |

|     |                                                                                                                                                                  |          |

| 8.1 | Kernel control behavior.                                                                                                                                         | 182      |

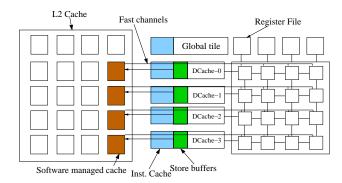

| 8.2 | Microarchitecture block diagram                                                                                                                                  | 194      |

| 8.3 | Memory system mechanisms. Software managed cache, fast channels and store buffers                                                                                | 195      |

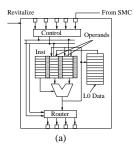

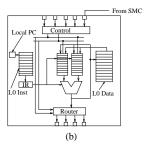

| 8.4 | Execution core and control mechanisms. a) Instruction, operand revitalization and L0-data storage. b) Local PC and L0-instructio store to provide MIMD execution | n<br>197 |

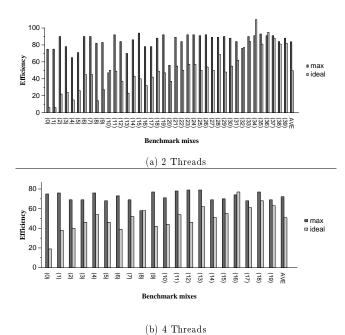

| 8.5 | Speedup using different mechanisms, relative to baseline architecture. Programs grouped by best machine configuration.                                           | 209      |

xvii xviii

## Chapter 1

## Introduction

In the last decade, programmable processors have proliferated into increasingly diverse application domains, producing distinct markets for desktop, network, server, scientific, graphics, and digital signal processors. While clearly providing application-specific performance improvements, these processors perform poorly on applications outside of their intended domain, primarily because they are tuned to exploit specific types and granularities of parallelism, and to some extent due to instruction set specialization. Emerging applications with heterogeneous computational requirements, such as image recognition and tracking or video databases, introduce the need for computation systems that can support such heterogeneous computation. Future systems can be heterogeneous at the hardware level, built using multiple domain-specific processors to support this application heterogeneity. They suffer from two problems: reduced economies of scale compared to a single general purpose design and design-time freezing of the processor mix and composition. These two problems motivate the need for a flexible or polymorphous processor design that can adapt to different application demands dynamically.

Along with this proliferation of programmable processors, the perfor-

mance of general purpose processors has grown tremendously over the past two decades. This improvement has come from deeper pipelines and faster transistors. Device integration has played a large role in improving processor performance as well, enabling large on-chip multi-megabyte caches, multiple floating point units on chip, and microarchitecture structures to improve performance. Due to technology limitations of wire delays [4], power [74], and process variation [25], performance improvement due to pipelining and faster transistors is likely to slow down. Device integration has already reached a point where conventional architectures are unable to utilize more on-chip transistors to extract more performance. As a result, performance growth in the future must come from extracting more concurrency from applications. Architectures must extract concurrency at all levels, including thread-level and coarse-grained data-level parallelism, and not rely on only fine-grained instruction-level parallelism. But conventional architectures are poor at extracting such different granularities of parallelism and furthermore rely primarily on large centralized structures like register files, rename tables, and predictors to extract concurrency. Due to the aforementioned technology limitations, scaling conventional designs which are monolithic and integrated to future technologies is infeasible. There is instead a desire for scalable and modular architectures.

Broadly, the two trends that processor architects face are: 1) emerging applications with heterogeneous computation needs, and 2) technology limitations of power, wire-delay, and process variation. There is a growing

need for design methodologies that can achieve economies of scale, provide support for heterogeneous applications, and combat the processor complexity arising from these technology trends. In this dissertation, we introduce polymorphism to build such scalable processors that provide support for such heterogeneous computation. The key idea behind polymorphism is to configure coarse-grained microarchitecture blocks to provide an adaptive and flexible processor substrate. Technology scalability is achieved by a designing an architecture using scalable and modular microarchitecture blocks.

Another strategy for addressing technology constraints and diverse application demands is to build a heterogeneous chip, which contains multiple processing cores, each designed to run a distinct class of workloads effectively. The Tarantula processor is one example of integrated heterogeneity [48]. The two major downsides to this approach are increased hardware complexity, since there is little design reuse between the types of processors and poor resource utilization when the application mix contains a balance different than that ideally suited to the underlying heterogeneous hardware.

The intent of a polymorphous design instead is to build one or more homogeneous processors, thus mitigating the aforementioned complexity problem. The polymorphous nature of the processor cores allows the hardware to be configured to provide special purpose behavior on an application-by-application basis, thus adapting to a wide range of application classes. Since the hardware is constructed of homogeneous processor cores, the resource utilization problem found in heterogeneous systems, of mis-match between appli-

cation mix and hardware capability does not arise since the hardware can be adapted at run-time to any application mix.

In this dissertation, we define architectural polymorphism and describe a core set of principles which we build upon to develop mechanisms to implement polymorphism. We describe the TRIPS architecture which is a technology scalable and partitioned design. The TRIPS ISA is one instance of a new class of ISAs called Explicit Data Graph Execution (EDGE) which we propose in this dissertation as an architectural solution to expressing concurrency to the hardware. The polymorphous mechanisms are described in the context of the TRIPS architecture. In the remainder of this chapter we provide a short overview of polymorphism, a summary of the TRIPS architecture, and conclude with a thesis statement and a description of contributions.

#### 1.1 Principles of Polymorphism

We define architectural polymorphism as the ability to modify the functionality of coarse-grained microarchitecture blocks at runtime, by changing control logic but leaving datapath and storage elements largely unmodified, to build a programmable architecture that can be specialized on an application-by-application basis. The main principles of polymorphism are the following which are developed in detail through the remainder of this dissertation:

- Adaptivity across different granularities of parallelism.

- Economy of mechanisms so that different microarchitecture structures

3

are used differently at different times, rather than application-specific structures.

Reconfiguring coarse-grained blocks to provide different functionality instead of synthesizing fine-grained primitive components into blocks with different functionality, as done by FPGAs.

## 1.2 System Design

Before applying this abstract definition of architectural polymorphism to processor architectures to develop the resources and mechanisms for implementing polymorphous systems, three main system decisions must be addressed: the granularity of processor cores, granularities of parallelism, and technology scalability.

#### 1.2.1 Granularity of Processors

The granularity of processors spans the following spectrum shown in Figure 1.1.

- a) Ultra-fine-grained FPGAs that consist of an array of gates or configurable lookup tables interconnected through a configurable network. These are typically programmed using a high-level hardware description language and applications are synthesized to the hardware.

- b) Several basic processing cores like in PipeRench [59] or PACT-XPP [19].

The primitive processor elements provide more functionality than gates

Figure 1.1: Granularity of parallel processing elements on a chip. Number of cores that can fit on a typical 65nm high performance chip.

and lookup tables used in an FPGA. They are programmed at a higher level of abstraction than FPGAs and thus speed up the development process, however they still synthesize applications to hardware like an FPGA.

- c) Many simple in-order processors like in the RAW architecture [156, 158] or Sun Niagara chip [92]. Each processing core is a full fledged processor that runs applications compiled down to the ISA of the processor. RAW also has the ability to use sophisticated compiler techniques to map a single application across these processing cores.

- d) Many powerful out-of-order processors like in the POWER4 chip [159]. The processing cores are more powerful and provide higher single-thread performance than the above three.

- e) Some number of ultra-wide issue processors like the Grid Processor [117]-

a TRIPS chip like configuration we propose in this dissertation.

Fine-grained architectures perform well when ample fine-grained parallelism exists but do not support general purpose sequential programs. They are plagued by synchronization overheads resulting from aggregating multiple of these units together. Coarse-grained architectures using conventional wide-issue out-of-order processors have the ability for high performance on sequential codes, but have traditionally lacked the capability for partitioning and support for fine-grained parallelism. Technology limitations of power and wire delays limit the scalability of conventional out-of-order processor designs.

In this dissertation, we assert that a chip with few large cores is better than many fine grained cores across a spectrum of applications if the coarse-grained cores can be subdivided when fine-grain parallelism exists. Our two key insights are: 1) Use the dataflow graph as a basic level of abstraction to express concurrency to the hardware to eliminate the hardware's need to rediscover concurrency, and reduce the hardware overheads of instruction-level bookkeeping. 2) The full processor core is designed to exploit coarse-grained concurrency and we use polymorphism to subdivide resources to support fine-grained concurrency.

#### 1.2.2 Granularity of Parallelism

To first order, classes of applications can be represented by different types of concurrency. Desktop, server, network processing, digital signal processing, etc. can all be classified into three categories of parallelism: Instruction-level Parallelism (ILP): The predominant type of parallelism is among individual machine operations, such as memory loads, stores, and arithmetic operations. The operations are simple RISC-style operations and the system is handed a single program written with a sequential processor in mind [134].

Thread-level Parallelism (TLP): Parallelism between multiple threads of control, either from the same program or from different programs.

Data-level Parallelism (DLP): Parallelism across groups of data that have the same or similar operations applied to them. Several data operands share a single flow of control.

The differences between application domains includes several other features:

- Memory access patterns which include streaming-like regular or more irregular accesses typical of recursive data structures.

- Instruction mix.

- Types of arithmetic operation, namely fixed point or floating point.

- Energy efficiency and power consumption. Embedded workloads typically operate in the milli-watt regime, whereas server workloads operate in the 60W to 80W regime.

7

However, at an architecture level, granularity of parallelism is the main difference between different application domains.

These classes of concurrency are not mutually exclusive. In fact, it is common to extract some amount of ILP in traditional multithreaded workloads like database workloads. An example of simultaneously using TLP and DLP is found in the Cell processor, where multithreading is extensively used to partition work among eight Synergistic Processing Engines which are SIMD execution units used to extract DLP. In the remainder of this dissertation, we examine polymorphism and application heterogeneity in the context of these three types of parallelism. While ILP and TLP are well understood, the differences between programs with DLP is less well understood. In chapter 8 we undertake a comprehensive program characterization of data-level parallelism to analyze the behavior of these programs

## 1.2.3 Technology Scalability

Conventional microarchitectures traditionally rely on large centralized structures like register files, branch prediction tables, and rename tables to extract concurrency [4]. Increasing wire delays and the limits on pipeline depth from a performance and power perspective restrict the scalability of these architectures [4,73,74,80,151]. Consequently, technology limitations have driven a desire for scalability, modularity, reduced complexity, and energy efficiency in processor architectures. Polymorphism could potentially satisfy these requirements.

- Scalability and Modularity: The basic ideas behind polymorphism lead to the construction of scalable and reconfigurable modular blocks to support multiple application domains.

- Complexity: The economy of mechanisms that is central to architectural polymorphous inherently reduces complexity and makes the architecture scalable.

- Energy efficiency: By using a small set of mechanisms and adapting

the processor to an application's needs, polymorphous architectures can

be energy efficient for wide class of domains compared to general purpose

programmable processors. However, it is not clear how close polymorphous systems can get to the energy efficiency of specialized processors.

## 1.3 TRIPS Architecture

In this dissertation, we develop a technology scalable architecture called TRIPS which uses a new dataflow encoding ISA to express concurrency more efficiently to the hardware. The hardware is implemented using a distributed microarchitecture that relies on well defined control and data networks for communication. One contribution of this dissertation is the specification and description of this scalable and distributed architecture. The mechanisms to implement polymorphism are developed in the context of this architecture. We chose this architecture as our baseline upon which to develop the mechanisms for polymorphism because this design already provides a scalable and modular

starting point. The main features of the architecture are:

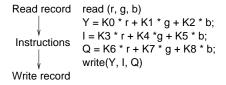

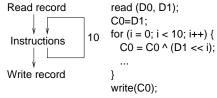

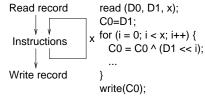

1. Dataflow dependences are encoded in the ISA to enable direct instruction-instruction communication and reduce the overheads of detecting and managing dependencies that conventional out-of-order processors must pay. This new class of ISAs called EDGE (Explicit Data Graph Execution) essentially brings dataflow to the ISA, without having to change programming models. Unlike VLIW architectures, the execution order of instructions is determined dynamically based on when operands arrive at instruction slots, thus relieving the compiler of the responsibility of determining the dynamic execution order.

- 2. The program is partitioned into well-defined blocks to limit the scope of the dependences so that the number of dependence arcs does not exceed the instruction space. Dependences inside such a block are encoded directly in the instructions, while dependences across blocks are expressed through architectural registers or store-load pairs. This execution model fetches, executes, and commits a full block of instructions atomically to reduce the overheads of instruction management like register renaming, dependence checking, and branch prediction. These overheads are amortized across many instructions, thus saving energy per executed instruction.

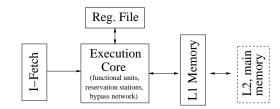

- To manage design complexity and address wire-delay scaling, the computation core is completely distributed using well defined microarchitecture

control and data networks with only nearest-neighbor links for communication. The use of such well defined networks reduces design complexity because the the communication and interaction between units is only through these networks, compared to bypass paths and stall signals as is common in conventional designs. Furthermore, the microarchitecture is constructed is using a set of small tiles such that these nearest-neighbor links can be traversed in a single cycle, and each tile's complexity is low.

## 1.4 Implementation of Polymorphism

Architectural polymorphism provides the capability to configure hardware at run-time to perform different functions. Unlike a reconfigurable architecture, a polymorphous architecture alters the behavior of coarse-grained components instead of synthesizing functions from primitive logic blocks at run-time.

Table 1.1 lists a taxonomy of high-level architectures principles used in processor design and defines the polymorphism approach using this taxonomy. The taxonomy provides a 4-tuple that can be used to classify architectures into one (or more) of 16 possible categories and polymorphous architectures occupy a portion of this space. In chapter 2 which discusses related work, we classify other architectures according to this taxonomy. Below, we briefly explain polymorphous architectures according to this taxonomy.

• Architecture type: Architecture type can be programmable hardware

11

or application specific hardware. Programmable hardware refers to architectures that execute a program specified using an ISA that has been compiled into a program binary, with typically a small portion of the program's instructions mapped to execution resources on the hardware at one time. Application specific hardware on the other hand directly maps the functionality of the entire program into hardware elements like gates and data-path units with the full program mapped to the hardware at once. Programmability differentiates architectural polymorphism from other approaches to reconfiguration like FPGAs which create application specific hardware. Polymorphous architectures tailor a programmable architecture to application needs.

- Processor type: The processor cores used to construct a chip can be

homogeneous or heterogeneous. While polymorphism does not require

or imply a chip made of homogeneous processor cores, in this dissertation we restrict ourself to discussing and evaluating polymorphism for

homogeneous cores. The Smart Memories chip is another example of a

homogeneous polymorphous architecture.

- Core granularity: Core granularity can be coarse-grained or fine-grained, and we define a core as the set of units on-chip controlled by

a single program counter. Architectural polymorphism can be implemented on fine-grained cores like simple in-order processors or coarse-grained cores like the TRIPS core. Designing polymorphous mechanisms

| Architecture             | Processor                  | Core           | Configuration  |  |  |

|--------------------------|----------------------------|----------------|----------------|--|--|

| $\mathbf{type}$          | $_{ m type}$               | granularity    | granularity    |  |  |

| Programmable h/w         | Homogeneous                | Coarse-grained | Coarse-grained |  |  |

| Application specific h/w | Heterogeneous              | Fine-grained   | Fine-grained   |  |  |

| Pol                      | Polymorphous Architectures |                |                |  |  |

| Programmable h/w         | Homogeneous                | Coarse-grained | Coarse-grained |  |  |

|                          | or                         | or             |                |  |  |

|                          | Heterogeneous              | Fine-grained   |                |  |  |

Table 1.1: A taxonomy of architectures.

for aggregating fine-grained cores to execute a large program presents different challenges from partitioning a coarse-grained core for supporting fine-grained concurrency. While aggregation introduces the challenge of overcoming synchronization overheads when multiple cores must communicate, for coarse-grained cores the challenge is efficiently partitioning the substrate to a sufficiently small level of granularity to support fine-grained parallelism.

Configuration granularity: Architectural polymorphism is defined as configuration of coarse-grained microarchitecture blocks and is different from synthesizing different functions from fine-grained primitive components like datapath slices, like and FPGA, or primitive processing elements.

In this dissertation, we discuss polymorphism in the context of the TRIPS processor to support different granularities of parallelism. The main polymorphous resources in the TRIPS processor are: the *instruction window*  space, physical register files, the block sequencing logic, and the on chip memory system.

While the concept and the mechanisms are explained in detail in Chapter 5 we briefly summarize the resources and provide some examples of polymorphism below. Using polymorphism the reservation stations can be reconfigured in the following ways to adapt the processor to different granularities of parallelism: 1) configure the reservation stations like an instruction window and devote all entries to one thread to support ILP, 2) share the reservation stations among multiple threads for TLP, and 3) provide instruction sequencing support at every ALU site to support fine-grained DLP that is best executed in a MIMD style of computation.

## 1.5 Thesis Statement

This dissertation introduces the concept of architectural polymorphism – the capability to configure coarse-grained microarchitecture blocks to provide application controlled specialization of an architecture. This dissertation presents the design and implementation of a scalable processor that can be configured to support different granularities of parallelism using polymorphous mechanisms. Specifically, this dissertation describes the TRIPS architecture and evaluates polymorphous mechanisms for supporting different granularities of parallelism on the TRIPS processor.

## 1.6 Dissertation Contributions

This dissertation makes the following main contributions.

Architectural Polymorphism: We introduce the concept of architectural polymorphism and develop the main principles and a set of mechanisms driven by these principles that configure coarse-grained microarchitecture blocks to support different granularities of parallelism. Compared to reconfigurable architectures which attempt to provide support for diverse workloads using a synthesis approach of building different functional blocks from primitive components, the principle behind polymorphism is to adapt coarse-grained blocks to behave differently.

TRIPS Architecture: We describe the TRIPS processor organization, its ISA (one instance of an EDGE ISA), and microarchitecture<sup>1</sup>. EDGE ISAs succinctly express concurrency to the hardware by encoding programs as sequences of atomic blocks of execution with blocks encoding a dataflow graph that can be directly mapped to physical resources in the processor. The TRIPS processor core provides a 1024-entry instruction window and can issue up to 16 instructions every cycle. We have also built a prototype chip in 130nm ASIC technology composed of two TRIPS processor cores and a distributed

<sup>&</sup>lt;sup>1</sup>The principles behind EDGE ISAs and the implementation of the TRIPS ISA and its microarchitecture are not sole individual contributions but are collaboratory efforts in which I have played lead intellectual roles.

1MB on-chip memory system which can be configured as a non-uniform cache architecture (NUCA).

Data-Parallel Program Attributes: We present a detailed characterization of the fundamental behavior of data-parallel programs based on their memory access patterns, program control behavior, and available concurrency.

Experimental Evaluation: Our performance results show that the TRIPS microarchitecture can sustain good instruction-level parallelism. On a set of hand-optimized kernels IPCs in the range of 4 to 6 are seen, and on a set of highly data-parallel benchmarks with compiler generated code IPCs in the range of 1 to 4 are seen. On the EEMBC and SPEC CPU2000 benchmarks we see IPCs in the range of 0.5 to 2.3. Comparing performance to the Alpha 21264, which is a high performance architecture tuned for ILP, TRIPS is up to 3.4 times better on the hand optimized kernels. However, the compiler generated binaries for the DLP, EEMBC, and SPEC CPU2000 benchmarks perform worse on TRIPS compared to an Alpha 21264. With more aggressive compiler optimization we expect the performance of the compiler produced binaries to improve.

With more aggressive compiler optimization we expect these numbers to improve.

The polymorphous mechanisms proposed in this dissertation are effective at exploiting thread-level parallelism and data-level parallelism. When

executing 4 threads on a single processor, high levels of processor utilization are seen, IPCs are in the range of 0.7 to 3.9 for an application mix consisting of EEMBC and SPEC CPU2000 workloads. When executing programs with DLP, the polymorphous mechanisms we propose provide harmonic mean speedups of 2.1X across a set of DLP workloads, compared to an execution model of extracting only ILP. Compared to specialized architectures, these mechanisms provide competitive performance using a single execution substrate.

## 1.7 Dissertation Organization

The remainder of this dissertation is organized as follows. Chapter 2 discusses related work and places this dissertation in the context of prior work. Chapter 3 defines and describes EDGE ISAs and the compilation strategy for this new class of ISAs. Chapter 4 describes the TRIPS architecture and the prototype TRIPS chip. We describe the TRIPS ISA, the microarchitecture of the TRIPS chip, and briefly describe the logic design, verification, synthesis and physical design of the prototype TRIPS chip.

Chapter 5 describes architectural polymorphism. We describe the three principles behind polymorphism and a classification scheme for processor resources into fixed, specialized, and polymorphous resources. We then describe the mechanisms and resources required to implement polymorphism to support ILP, TLP, and DLP in the TRIPS architecture.

Chapter 6 presents a performance evaluation of the TRIPS processor

17

focused on instruction-level parallelism. The performance evaluation is based on an event driven validated processor simulator. Chapter 7 presents a performance evaluation of using polymorphous mechanisms in the TRIPS processor to extract thread-level parallelism.

Chapter 8 presents a detailed application characterization of data parallel programs based on their fundamental behavior. Based on this characterization a set of microarchitecture mechanisms to support data-level parallelism is proposed. This chapter also includes a performance evaluation of these mechanisms on a high-level processor simulator that models the TRIPS processor. Finally, chapter 9 concludes and points to some future directions in the software aspects of polymorphous systems and the application of polymorphism to optimize other technology constraints like power and area.

## Chapter 2

## Related Work

This chapter discusses and differentiates prior work most closely related to the focus of this dissertation. The related work is grouped around the four main themes of this dissertation: polymorphism, data parallel architectures, scalable architectures, and microarchitecture techniques for ILP.

## 2.1 Polymorphism

Below we discuss the previous work related to polymorphism. We discuss prior work that has focused on support for different types of applications on a single substrate using reconfiguration or other means.

Multithreading: While multithreading is not directly related to supporting different types of applications, polymorphism-like behavior has been used to support multithreading in modern processor. We briefly trace the history of multithreading before describing these systems. Multithreading has been widely used to share compute resources between multiple program threads [102]. Multithreaded pipelining was used in the Peripheral and Control Processors of the Control Data 6600 computer architecture of the early 1960s to provide

19

several virtual peripheral processors [160]. More recently, the HEP multiprocessor system had limited polymorphous behavior. It included support for multiple program contexts in the processor and "it allowed the user to control the number of processes dynamically in order to take advantage of varying amounts of parallelism in a problem [148]." Other recent systems that provided multithreading support on a single chip include the MIT M-Machine [53], MIT Alewife machine [3], Hydra [70], and the Pirañha multiprocessor [18].

Fine-grained multithreading to share processor resources between threads has been explored using different techniques. The Tera computer system had support for fine-grained multithreading interleaving long instruction word (LIW) instructions from different threads every cycle [8]. Keckler and Dally proposed an architecture that incorporated both compile-time and run-time information to interleave multiple VLIW instructions on individual functional units [87]. Both of these have a polymorphous nature in the sense that they support single-thread execution and multiple threads using the same set of mechanisms. Tullsen et al. described their approach of supporting multiple thread contexts in the pipeline of a modern out-of-order processor and called it simultaneous multithreading (SMT) [164]. They method replicates certain architectural storage elements in the processor, but shares most other resources to support the execution of multiple threads simultaneously in the processor pipeline. Yamamoto and Nemirovsky proposed an architecture similar to SMT but with separate instruction queues for each thread [173]. Ungerer et al. provide a detailed survey of multithreading literature [166].

Novel architectures: Browne et al. developed the Texas Reconfigurable Array Computer that could support sequential processing, SIMD, and MIMD processing on a single substrate [83,144]. The TRAC project was focused on building interconnection networks and optimizing communication for a configurable array that relied on large amounts of off-chip communication.

The Stanford Smart Memories project employs polymorphous mechanisms to synthesize a large core from a modular homogeneous substrate [107] While this approach works well for thread-level and data-level parallelism, single threaded execution suffers on this architecture. The main conceptual difference between Smart Memories and TRIPS is that TRIPS has a well defined set of specialized resources and fixed resources that can be used to support specific application needs. For example, TRIPS has a traditional 2-way set associative instruction cache which provides high instruction fetch bandwidth and low latency instruction fetch. Its function does not change with application behavior. A second example is the next-block predictor used in TRIPS which is used to predict control flow for sequential programs. In Smart Memories on the other hand, there are no such fixed resources like the instruction cache or specialized resources like the next-block predictor. Instead the architecture simply provides an array of tiles, with each tile containing multiple SRAM banks, an interconnection network, and a simple processor core. Synthesizing efficient instruction cache behavior out of these SRAM banks can be challenging and creating branch predictor-like behavior out of the memory tiles is almost impossible. While more homogeneous and perhaps simpler than the TRIPS design, the lack of any specialized resources makes this architecture less adaptable.

The Vector-Thread Architecture supports data parallel and multithreaded execution by configuring the instruction sequencing logic of a set of closely coupled processor cores [95]. This architecture provides a scalable, tightly integrated MIMD array for data intensive processing. Clearly it can excel on vector codes and fine-grained MIMD parallelism. However, this architecture lacks many mechanisms that are required for extracting ILP. For example, it lacks memory ordering mechanisms for load/store re-ordering. As a result it is unclear how well this architecture will perform on general purpose programs.

Sasanka et al. propose a novel architecture called ALP to support ILP, TLP, and DLP for media applications [139]. They introduce a DLP technique called SIMD vectors and streams (SVectors/SStreams), which is integrated within a conventional superscalar based CMP/SMT architecture with subword SIMD parallelism. The technique exploits the simple implementation of sub-word SIMD already common in many machines and provides the benefits of full-fledged vector processing. The primary focus of ALP is to support multiple types of parallelism on conventional architectures with evolutionary changes to the ISA and microarchitecture. Its main drawback is that it augments a conventional processor core and as a result it does not scale to large issue widths. The techniques proposed in ALP extend a conventional processor core to support parallelism efficiently, but do not address the wire-delay and complexity issues that plague scaling of the underlying microarchitecture.

As a result, large amounts of DLP will have to be partitioned into threads and distributed across a set of narrow-issue cores. TRIPS on the other hand provides a scalable very wide-issue design that can be tailored to application needs using polymorphism.

Finally, Rabbah et al. introduce a versatility metric to quantify the ability of an architecture to effectively execute a broad set of applications [130]. They also propose a benchmark suite called VersaBench suite that is comprised of a set of applications that capture diverse behavior. This versatility metric is simply a quantitative metric for comparing different types of architectures and does not describe or characterize the architecture itself. They formally define versatility as: "the geometric mean of the speedup of each of the applications in the VersaBench suite relative to the architecture which provides the best execution time for that application."

Extensions to conventional designs: In addition to reconfiguration for performance, adaptivity has been used to increase energy efficiency. Albonesi et al. [7] introduce adaptive processing where on-chip structures are dynamically resized to provide power efficient execution. This can be thought of as polymorphism within the ILP domain that uses run-time application behavior to improve energy efficiency. Other examples of specific microarchitecture mechanisms to provide adaptability include the following: adjusting cache size via ways [6], sizing issue windows [56], adjusting the issue window coupled with the load/store queue and register file [127], adjusting issue width

23

along with the functional units [14], and adaptively resizing instruction issue queues [80, 129].

At a coarser granularity, single-ISA heterogeneous processors attempt to provide support for different granularities of parallelism by integrating multiples types of cores which all use the same ISA [99]. In a similar vein, Kumar et al. discuss the architectural tradeoffs of sharing varying degrees of hardware between processors and threads in a SMT/CMP hybrid design to explore the tradeoffs of ILP and TLP [100].

Coarse-grained reconfigurable architectures: Fisher et al. proposed Custom-fit processors where processor cores are synthesized at design time based on application needs [54]. They adopt a unique approach of designing a heavily customizable VLIW architecture in which the number and types of functional units, memory sizes and hierarchy, and number of registers can all be customized. Through a hardware/software co-design process one important application is taken as input and a customized VLIW architecture heavily optimized for that application is generated. The final processor is fully general purpose and can run all other applications also, albeit not as efficiently as the one "input" application. Tensilica follows a similar approach providing a complete toolchain flow for synthesizing processors and an ISA based on a set of applications [165].

PACT-XPP is an array-based architecture for stream computation which does data-flow computing in the array [19,58]. Vectorization techniques are

used to generate configuration states for this array for large blocks of repetitive code. One of the drawbacks in the architecture is the lack of support for executing sequential programs efficiently and lack of access to random access memory. The Mathstar [69] processor belongs to a new class of chips called Field Programmable Object Array (FPOA), in which, instead of configuration of gates like an FPGA, designers work with a massively parallel array of pre-configured function units like 16-bit ALUs, multiply-accumulate units, and register files which can communicate through an interconnect fabric.

In the ASH architecture, the predication model and dataflow concepts are similar to the TRIPS approach [29]. The main difference being that, ASH targets application-specific hardware for small programs, as opposed to compiling large programs into a sequence of configurations mapped to a programmable substrate. The Garp architecture and the BRASS project used an FPGA based reconfiguration approach to offload compute intensive regions of an application to an on-chip FPGA [76]. Hartenstein has written a literature survey of other reconfigurable coarse-grained architectures targeted at a single application domain [71,72].

## 2.2 Data Parallel Architectures

Several authors have proposed architectures and mechanisms for data parallel architectures. In this section we discuss the work most closely related to ours, grouped under vector processors, systolic arrays, SIMD/MIMD processors, stream processing and other hybrid architectures. The key difference

25

between many of these architectures and the polymorphism approach is the ability to support different granularities of parallelism and the granularity of reconfiguration.

Vector processors: Early data parallel architectures were classic vector processors which were built using expensive SRAMs for high-speed memory and large vector register files [78, 112, 138]. These machines were designed for programs with regular control and data behavior, but could tolerate some degree of irregular (but structured) memory accesses using scatter and gather operations. Programs with frequent irregular memory references or accesses to lookup tables performed poorly. A number of architectures have been proposed or built to overcome the limitations of the rigid vector execution model and to allow for dynamic instruction scheduling and conditional execution [48, 49, 94, 149]. Removing these limitations still did not make these architectures widely applicable as they provided support only for a subset of data parallel programs. The Vector IRAM architecture is another vector processing architecture that exploits VLSI density and uses embedded DRAM with closely integrated vector lanes [93]. However, the global control between the different vector lanes and specilization of the vector lanes renders sequential and non-vectorizable code very inefficient on this architecture. Short vector processing has found its way into commercial microprocessors in the form of instruction extensions such as MMX, SSE2, Altivec and VIS [43]. These architectures have similar requirements of regular control and data access, and have further restrictions on data alignment. Some of the ISA extensions, such as MMX and SSE2, have poor support for scalar-vector operations, only operating on one sub-word of a MMX/SSE2 register when using a scalar register as one operand.