Welcome back!

#### MEMORY: PAGING AND TLBS

Shivaram Venkataraman CS 537, Fall 2024

#### **ADMINISTRIVIA**

- Project 2 done?! -> deadline today

- Project 3 will be out! Start early? → 2 weeks

- Project I grades ->

- Midterm conflicts?

#### AGENDA / LEARNING OUTCOMES

Memory virtualization

What is paging and how does it work?

What are some of the challenges in implementing paging?

# **RECAP**

#### MEMORY VIRTUALIZATION

Transparency: Process is unaware of sharing

Protection: Cannot corrupt OS or other process memory

Efficiency: Do not waste memory or slow down processes

Sharing: Enable sharing between cooperating processes

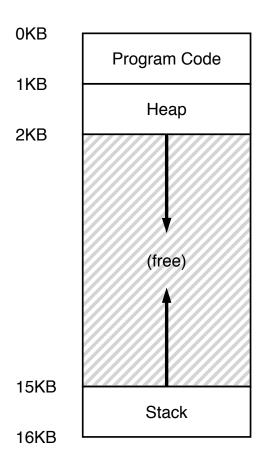

#### RECAP: WHAT IS IN ADDRESS SPACE?

the code segment: where instructions live

the heap segment: contains malloc'd data dynamic data structures (it grows downward)

Static: Code and some global variables

Dynamic: Stack and Heap

(it grows upward) the stack segment: contains local variables arguments to routines, return values, etc.

12 bits offset min mar

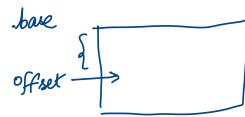

# REVIEW: SEGMENTATION = max segment size = 4K

Divide address space into logical segments

14 bit virtual address ress space

Each segment corresponds to logical entity in address space

(code, stack, heap)

Each segment has separate base + bounds register

How does process designate a particular segment?

- Top bits of logical address select segment

- Low bits of logical address select offset within segment

2 bits to segment

### **EXAMPLE: SEGMENTATION**

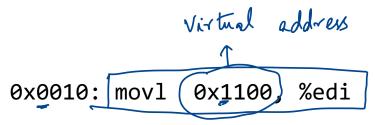

%rip: 0x0010

| Seg | Base          | Bounds |

|-----|---------------|--------|

| 0   | <u>0×4000</u> | 0xfff  |

| I   | 0×5800        | 0xfff  |

| 2   | 0×6800        | 0×7ff  |

CPV

1. Fetch instruction at logical addr 0x0010

Physical addr:

$$0 \times 4000 + 0 \times 0010$$

=  $0 \times 4010$

2. Exec, load from logical addr 0x1100

Physical addr:

$$0 \times 5800 + 0 \times 0100$$

=  $0 \times 5900$

## QUIZ 5!

#### https://tinyurl.com/cs537-fa24-q5

01 1001 1011 VA space 1K, Physical memory 16K

Segment 0 base (grows positive): 0x1959 (decimal 6489) Segment 0 limit

Segment I base (grows negative): 0x0b05 (decimal 2821)

Segment I limit : 282

Address space with two segments: segment 0 (topbit=0) or segment 1 (topbit=1).

10 bits virtual address

Segment of virtual address?

0x019b (decimal: 411)

**Translate**

316

0x019b (decimal: 411):

Segmentation violation

Segment?

0x0315 (decimal: 789):

Translate 0x0315 (decimal 789) VA space 1K, Physical memory 16K offset = 277 Segment 0 base (grows positive): 0x1959 (decimal 6489) Segment 0 limit :316 offset = offset - max seg Segment I base (grows negative): 0x0b05 (decimal 2821) Segment I limit : 282

Segment I base (grows negative):

$$0\times0b05$$

(decimal 2821)

Segment I limit : 282

Segment?

Ox0315 (decimal: 789):

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2309$

$2$

277 -512 = -235

0x0315 (decimal 789) PA = 2821 - 235 = 2586

#### DISADVANTAGES OF SEGMENTATION

Not Compacted 0KB Each segment must be allocated contiguously **Operating System** 8KB May not have sufficient physical memory for large segments? 16KB (not in use) 24KB **External Fragmentation** Allocated 32KB (not in use) Allocated 40KB 48KB (not in use) 56KB Allocated 64KB

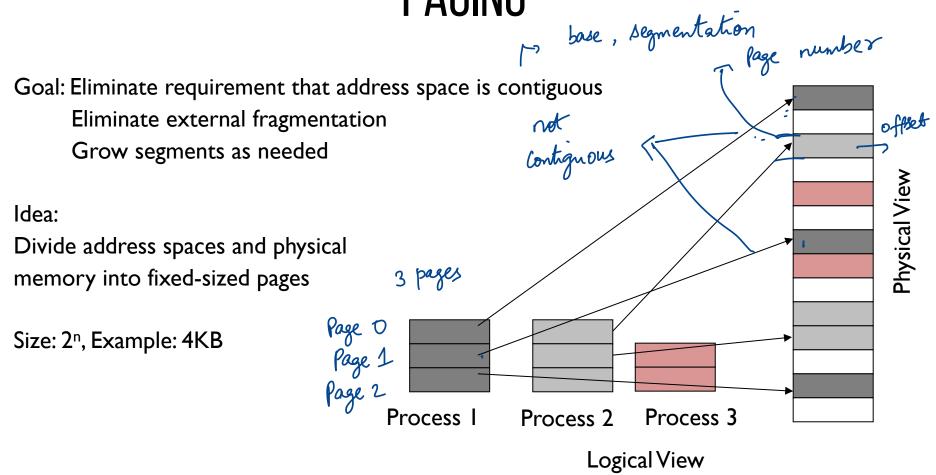

# **PAGING**

**PAGING**

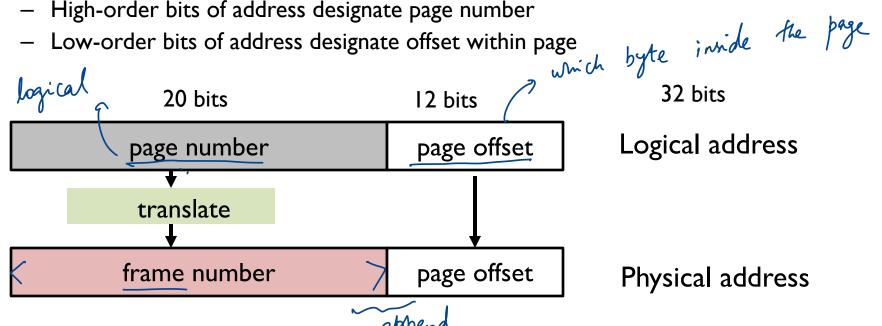

#### TRANSLATION OF PAGE ADDRESSES

How to translate logical address to physical address?

High-order bits of address designate page number

Low-order bits of address designate offset within page

No addition needed; just append bits correctly!

# ADDRESS FORMAT

Given known page size, how many bits are needed in address to specify offset in page?

| Page Size                         | Low Bits (offset)                   |  |  |

|-----------------------------------|-------------------------------------|--|--|

| I6 bytes I KB I MB 512 bytes 4 KB | 4 bits log_(1 KB) = 10 bilt 20 9 12 |  |  |

# **ADDRESS FORMAT**

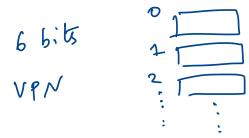

VPN Toffset

6 bits 4 bits

Given number of bits in virtual address and bits for offset, how many bits for virtual page number?

Total hits p low bits offset

| Page Size | Low Bits(offset) | Virt Addr<br>Total Bits | High Bits(vpn) |

|-----------|------------------|-------------------------|----------------|

| 16 bytes  | 4                | 10                      | 6              |

| I KB      | 10               | 20                      | 10             |

| I MB      | 20               | 32                      | 12             |

| 512 bytes | 9                | 16                      | 7              |

| 4 KB      | 12               | 32                      | 20             |

# **ADDRESS FORMAT**

20 4KB

Given number of bits for vpn, how many virtual pages can there be in an address space?

| Page Size | Low Bits (offset) | Virt Addr Bits | High Bits (vpn) | Virt Pages |

|-----------|-------------------|----------------|-----------------|------------|

| I6 bytes  | 4                 | 10             | 6               | 26 = 64    |

| I KB      | 10                | 20             | Ĩ0              | 2 = 64     |

| I MB      | 20                | 32             | 12              | 2   2      |

| 512 bytes | 9                 | 16             | 7               | 27         |

| 4 KB      | 12                | 32             | 20              | 20         |

| 32 bits   | virtual addre     | W = 20<br>2    | pages, each p   | age 4 KB   |

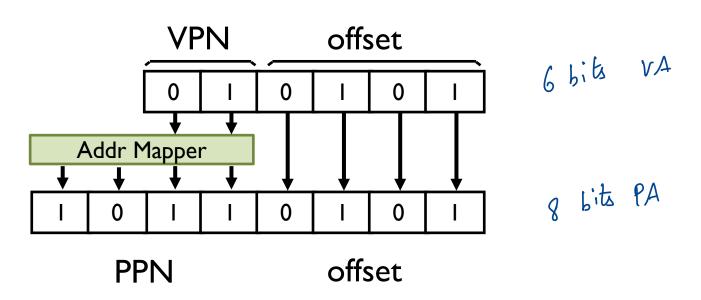

#### VIRTUAL -> PHYSICAL PAGE MAPPING

Number of bits in virtual address

need not equal

number of bits in physical address

How should OS translate VPN to PPN?

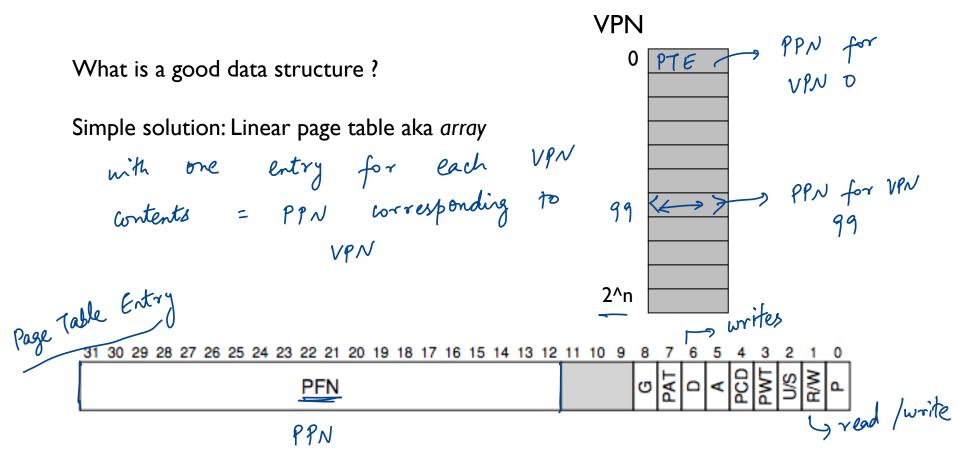

#### **PAGETABLES**

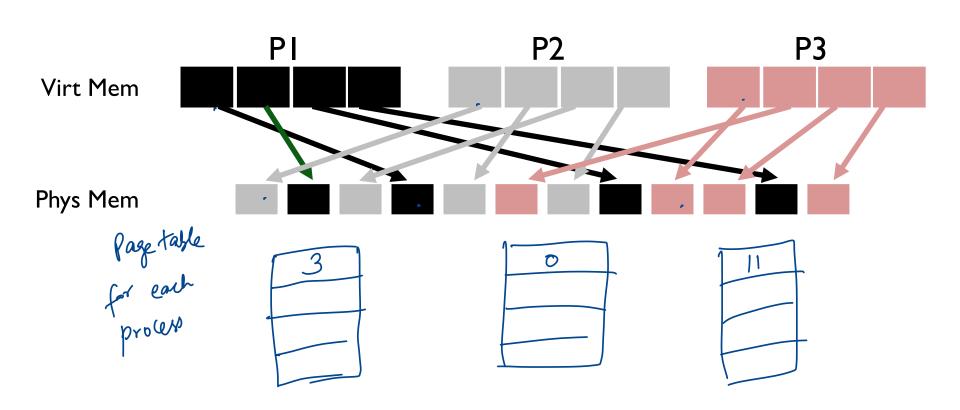

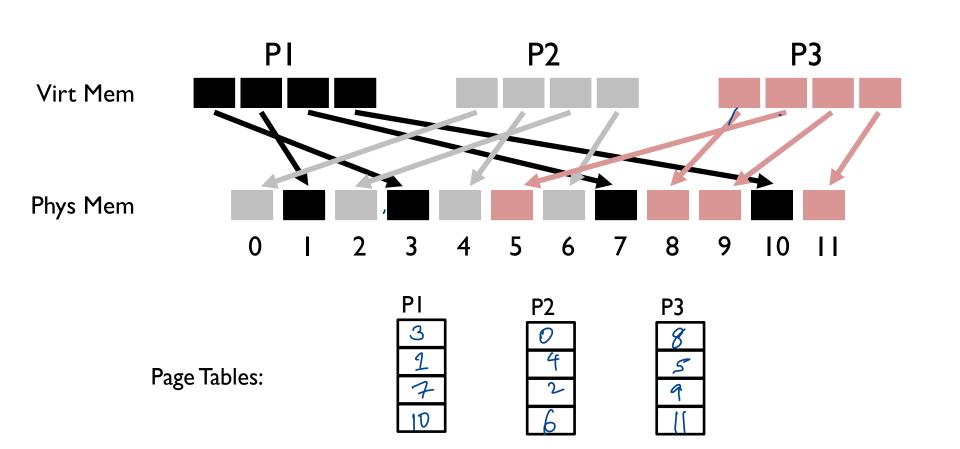

# PER-PROCESS PAGETABLE

### FILL IN PAGETABLE

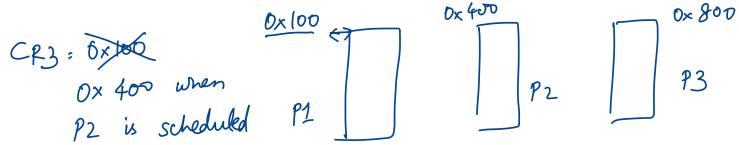

#### WHERE ARE PAGETABLES STORED?

Implication: Store each page table in memory

Hardware finds page table base with register (e.g., CR3 on x86)

What happens on a context-switch?

Change contents of page table base register to newly scheduled process

Save old page table base register in PCB of descheduled process

#### OTHER PAGETABLE INFO

What other info is in pagetable entries besides translation?

- valid bit

- protection bits -> R/W or execute

- present bit (needed later)

- reference bit (needed later)

- dirty bit (needed later)

Pagetable entries are just bits stored in memory

Agreement between HW and OS about interpretation

### MEMORY ACCESSES WITH PAGING

14 bit addresses

0x0010: movl 0x1100, %edi

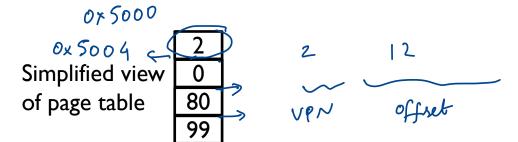

Assume PT is at phys addr 0x5000

Assume PTE's are 4 bytes

Assume 4KB pages

How many bits for offset? 12

Fetch instruction at logical addr 0x0010

Access page table to get ppn for vpn 0

Mem ref 1: Ox5000 → read PTE

Learn vpn 0 is at ppn 2

Fetch instruction at \_\_\_\_\_ (Mem ref 2)

0×2 010

append

### MEMORY ACCESSES WITH PAGING

14 bit addresses

0x0010: movl 0x1100, %edi

Assume PT is at phys addr 0x5000

Assume PTE's are 4 bytes

Assume 4KB pages

How many bits for offset? 12

Simplified view of page table  $0 \times 5004$

Exec, load from logical addr 0x1100 Access page table to get ppn for vpn 1 Mem ref 3:  $0 \times 5000 + \text{Size}(\text{PTE}) \times 1$ Learn vpn I is at ppn  $0 = 0 \times 5004$ Movl from into reg (Mem ref 4) 0100 2 mem access for

### MEMORY ACCESSES WITH PAGING

14 bit addresses

0x0010: movl 0x1100, %edi

Assume PT is at phys addr 0x5000 Assume PTE's are 4 bytes Assume 4KB pages How many bits for offset? 12

Simplified view 0

of page table 80

99

Fetch instruction at logical addr 0x0010

Access page table to get ppn for vpn 0

Mem ref I: \_\_\_\_0x5000\_\_\_\_

Learn vpn 0 is at ppn 2

Fetch instruction at \_\_\_0x2010\_\_\_ (Mem ref 2)

Exec, load from logical addr 0x1100

Access page table to get ppn for vpn 1

Mem ref 3: \_\_\_0x5004\_\_\_

Learn vpn 1 is at ppn 0

Movl from \_\_\_0x0100\_\_\_ into reg (Mem ref 4)

#### PROS/CONS OF PAGING

No external fragmentation

Any page can be placed in any frame in physical memory

Fast to allocate and free

- Alloc: No searching for suitable free space

- Free: Doesn't have to coalesce with adjacent free space

Internal fragmentation

4 KB

Wy not IMB?

- Page size may not match process needs

- Wasted memory grows with larger pages

Additional memory reference to page table →

- Page table must be stored in memory

- MMU stores only base address of page table

Storage for page tables may be substantial

- Requires PTE for all pages in address space

- Entry needed even if page not allocated?

#### SUMMARY: PAGE TRANSLATION STEPS

For each mem reference:

```

I. extract VPN (virt page num) from VA (virt addr)

2. calculate addr of PTE (page table entry)

3. read PTE from memory — experience

4. extract PFN (page frame num)

5. build PA (phys addr)

6. read contents of PA from memory into register

```

Which steps are expensive?

#### **EXAMPLE: ARRAY ITERATOR**

integer 4 bytes

```

int sum = 0;

for (i=0; i<N; i++){

sum += a[i];

}</pre>

```

Assume 'a' starts at 0x3000 Ignore instruction fetches and access to 'i'

What virtual addresses?

What physical addresses?

#### STRATEGY: CACHE PAGE TRANSLATIONS

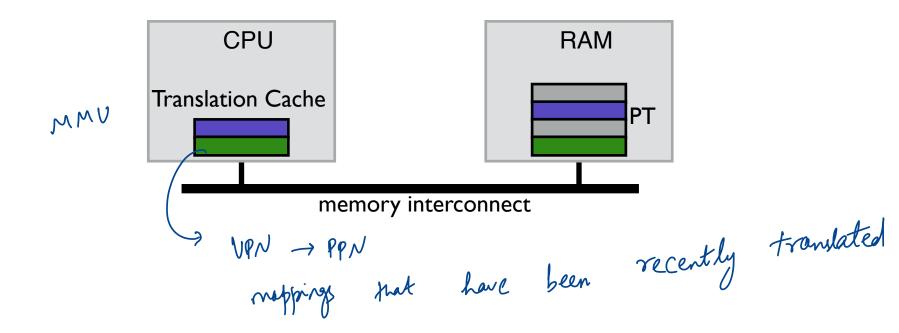

#### TLB: TRANSLATION LOOKASIDE BUFFER

TLB

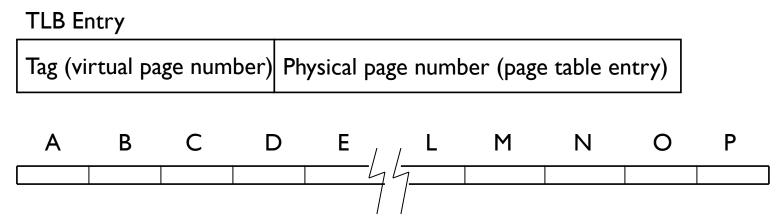

#### TLB ORGANIZATION

#### Fully associative

Any given translation can be anywhere in the TLB Hardware will search the entire TLB in parallel

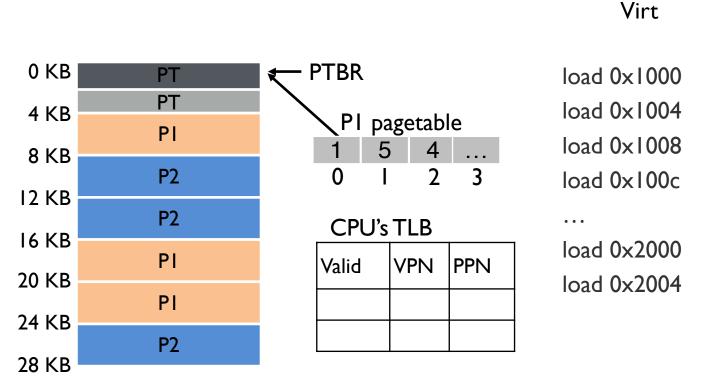

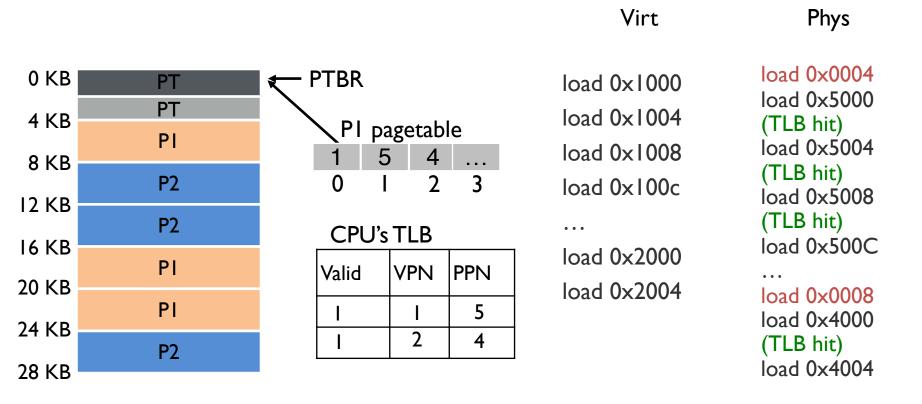

#### ARRAY ITERATOR (W/TLB)

```

int sum = 0;

for (i = 0; i < 2048; i++){

sum += a[i];

}</pre>

```

Assume 'a' starts at 0x1000 Ignore instruction fetches and access to 'i'

Assume following virtual address stream: load 0x1000

load 0x1004

load 0x1008

load 0x100C

• • •

What will TLB behavior look like?

#### TLB ACCESSES: SEQUENTIAL EXAMPLE

#### TLB ACCESSES: SEQUENTIAL EXAMPLE

#### PERFORMANCE OF TLB?

```

int sum = 0;

for (i=0; i<2048; i++) {

sum += a[i];

}</pre>

```

Would hit rate get better or worse with smaller pages?

```

Miss rate of TLB: #TLB misses / #TLB lookups

#TLB lookups? number of accesses to a = 2048

#TLB misses?

= number of unique pages accessed

= 2048 / (elements of 'a' per 4K page)

= 2K / (4K / sizeof(int)) = 2K / IK

= 2

```

Miss rate? = 2/2048 = 0.1%

Hit rate? (I - miss rate) = 99.9%

#### TLB PERFORMANCE

How can system improve hit rate given fixed number of TLB entries?

Increase page size:

Fewer unique page translations needed to access same amount of memory

TLB Reach: Number of TLB entries \* Page Size

#### **WORKLOAD ACCESS PATTERNS**

#### Workload A

```

int sum = 0;

for (i=0; i<2048; i++) {

sum += a[i];

}</pre>

```

Sequential array accesses almost always hit in TLB!

#### Workload B

```

int sum = 0;

srand(1234);

for (i=0; i<1000; i++) {

sum += a[rand() % N];

}

srand(1234);

for (i=0; i<1000; i++) {

sum += a[rand() % N];

}</pre>

```

#### **WORKLOAD ACCESS PATTERNS**

#### **WORKLOAD LOCALITY**

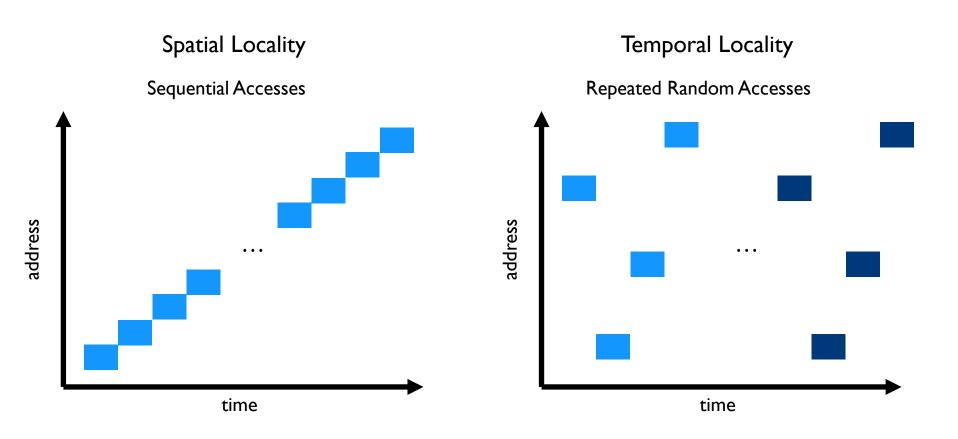

**Spatial Locality**: future access will be to nearby addresses

**Temporal Locality**: future access will be repeats to the same data

What TLB characteristics are best for each type?

#### Spatial:

- Access same page repeatedly; need same vpn → ppn translation

- Same TLB entry re-used

#### Temporal:

- Access same address near in future

- Same TLB entry re-used in near future

- How near in future? How many TLB entries are there?

#### OTHER TLB CHALLENGES

How to replace TLB entries? LRU? Random?

TLB on context switches? HW or OS?

### **NEXT STEPS**

Project 3 out!

Next class: More TLBs and better pagetables!