|

|

|||||||||||||||||||||

Homework 3 // Due at lecture Mon, Feb 21Primary contact for this homework: Peter Ohmann [ohmann at cs dot wisc dot edu] You may do this homework with one other person from your section. You must put both names on the assignment. Please staple multiple pages together. Problem 1 (2 points)Draw a transistor-level circuit for a three-input AND gate. Problem 2 (3 points)

Problem 3 (3 points)

Problem 4 (5 points)

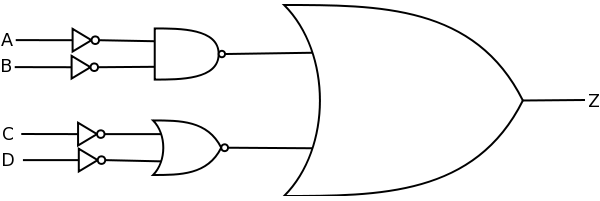

Given the circuit:

Problem 5 (3 points)

Draw the FSM state-diagram for recognizing all 4-bit unsigned numbers greater than

or equal to 12. (Hint: Each edge will either correspond to

a 1 or a 0. If the last four bits correspond to a value greater than or equal

to 12, your FSM should have 1 as output; otherwise, it should have 0). For

help, look at the lock example in Figure 3.28 of the textbook (this is an

extension of that example). Problem 6 (3 points)How many memory locations can be addressed with a 16-bit address? Assuming the memory is byte-addressable and we are working with standard 32-bit integers, what is the theoretical maximum number of integers we could store and reference in our memory? (Hint: Think about how many total bytes/bits are in the memory). You may, of course, provide your answers as 2n. Problem 7 (4 points)

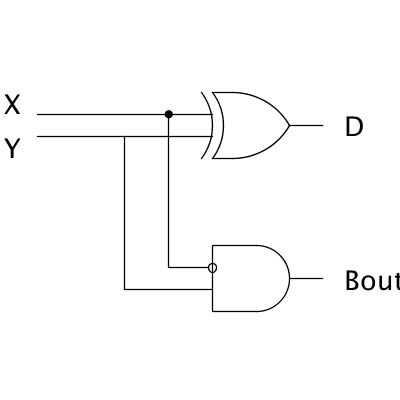

The figure below shows the gate-level circuit for a half-subtractor and its

associated truth table. Similar to the full-adder, the full-subtractor takes

two bits to be subtracted and a borrow-in, and outputs the result bit, and a

borrow-out. Based on this and your knowledge of the full-adder:

Problem 8 (2 points)

If one begins with the R-S latch (Figure 3.18 in the textbook) and replaces

the NAND gates with NOR gates, one obtains what is called an S-R latch.

What impact will this have on the action of the latch? |