# CS 701

### Charles N. Fischer

### Fall 2003

#### http://www.cs.wisc.edu/~fischer/cs701.html

### **Class Meets**

Tuesdays & Thursdays, 11:00 — 12:15 2321 Engineering Hall

### Instructor

Charles N. Fischer 5397 Computer Sciences Telephone: 262-6635 E-mail: fischer@cs.wisc.edu Office Hours: 10:30 - Noon, Mondays & Wednesdays, or by appointment

## **Teaching Assistant**

Kent Hunter 1308 Computer Sciences Telephone: 262-6602 E-mail: khunter@cs.wisc.edu Office Hours: 10:00 - 11:00 Tuesdays and Thursdays, or by appointment

## Key Dates

- September 23: Project 1 due

- October 21:

- October 23:

- November 18:

- determined

- Project 2 due (tentative)

- Midterm (tentative)

- Project 3 due (tentative)

- December 11: Project 4 due

- December ??: Final Exam, date to be

## **Class Text**

There is no required text. Handouts and Web-based reading will be used.

Suggested reference:

Advanced Compiler Design & Implementation, by Steven S. Muchnick, published by Morgan Kaufman.

### **Instructional Computers**

Departmental SPARC Processors (nova1-nova60)

You may use your own workstation if it is has a SPARC processor

(test using **dmesg|grep cpu**) Otherwise log onto a SPARC processor to do SPARC-specific assignments

## CS701 Projects

- 1. SPARC Code Optimization

- 2. Global Register Allocation (using Graph Coloring)

- 3. Global Code Optimizations

- 4. Individual Research Topics

## **Academic Misconduct Policy**

- You must do your assignments—no copying or sharing of solutions

- You may discuss general concepts and Ideas

- All cases of Misconduct *must* be reported.

- Penalties may be severe.

## **Reading Assignment**

- Get Handout #2 (Chapter 15, Code Optimization) from Dolt.

- Read Chapters 0-6 and Appendices G&H of the SPARC Architecture Manual. Also skim Appendix A.

- Read section 15.2 of Chapter 15.

- Read Assignment #1

### **Overview of Course Topics**

### 1. Register Allocation

#### Local Allocation

Avoid unnecessary loads and stores within a *basic block*. Remember and reuse register contents. Consider effects of *aliasing*.

#### Global Allocation

Allocate registers within a single subprogram. Choose "most profitable" values. Map several values to the *same* register.

#### Interprocedural Allocation

Avoid saves and restores across calls. Share globals in registers.

#### 2. Code Scheduling

We can reorder code to reduce latencies and to maximize ILP (*Instruction Level Parallelism*). We must respect *data dependencies* and *control dependencies*.

ld [a],%r1 ld [a],%r1

add %r1,1,%r2 mov 3,%r3

mov 3,%r3 add %r1,1,%r2

(before) (after)

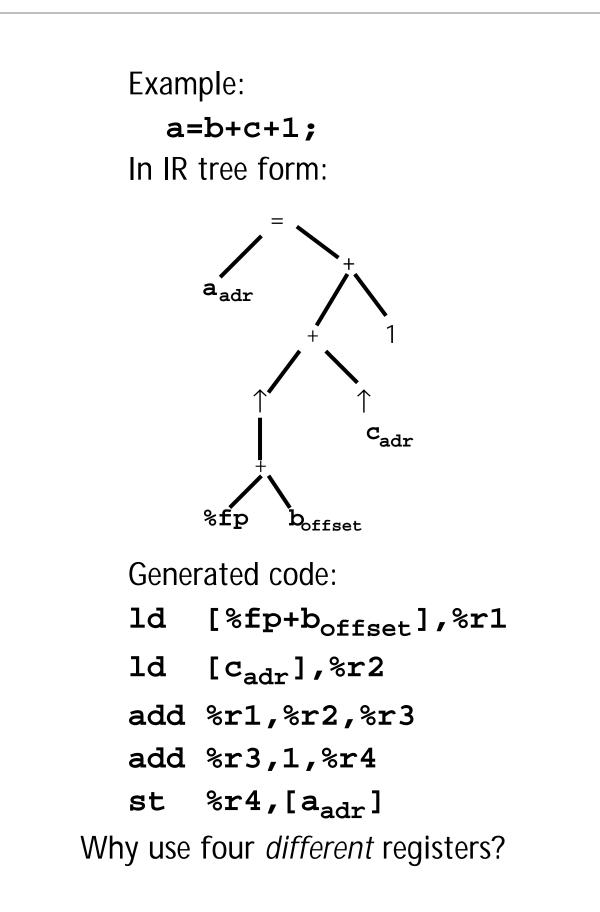

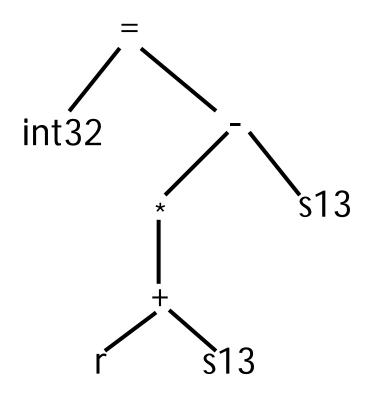

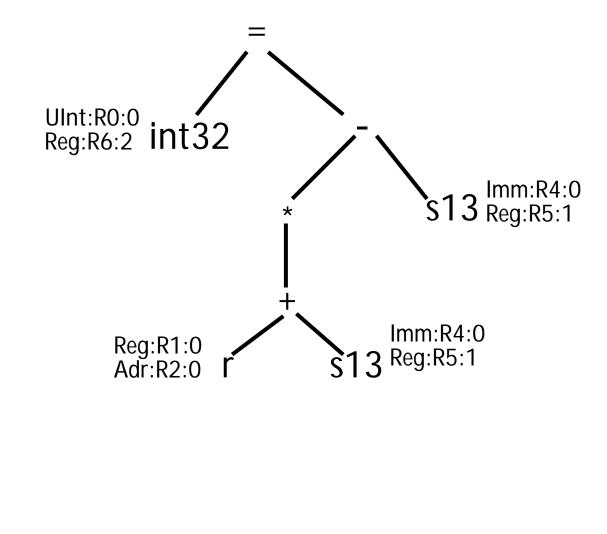

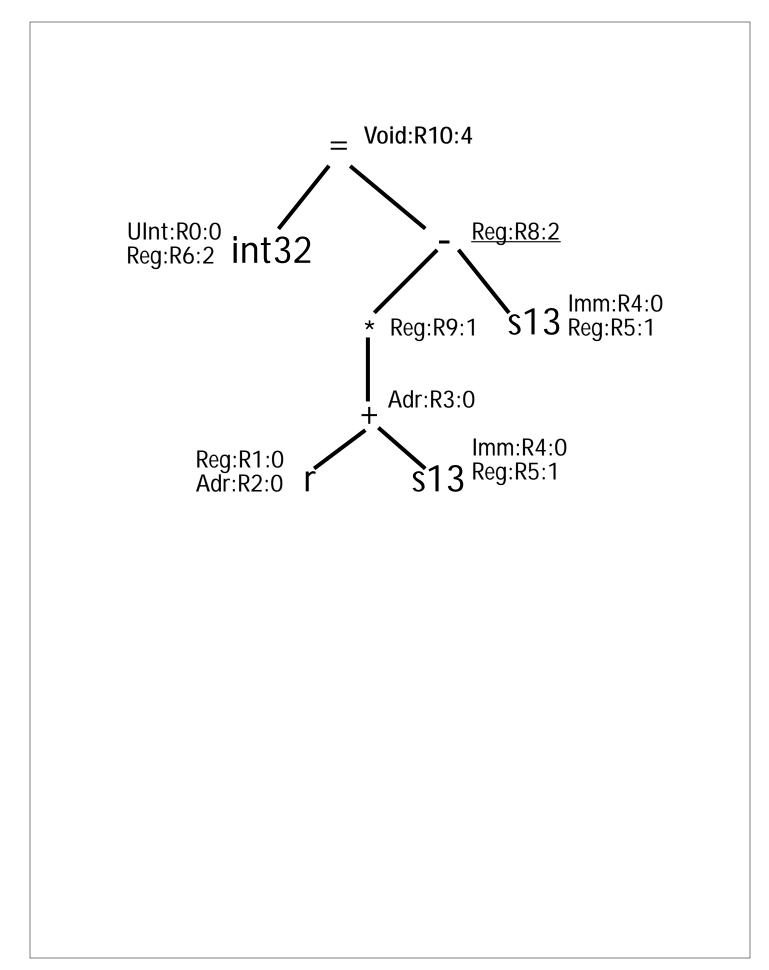

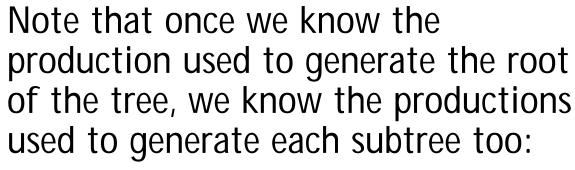

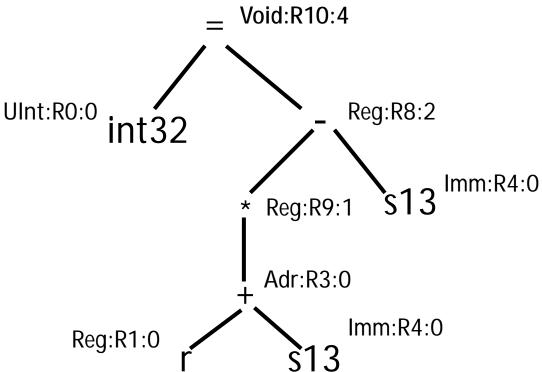

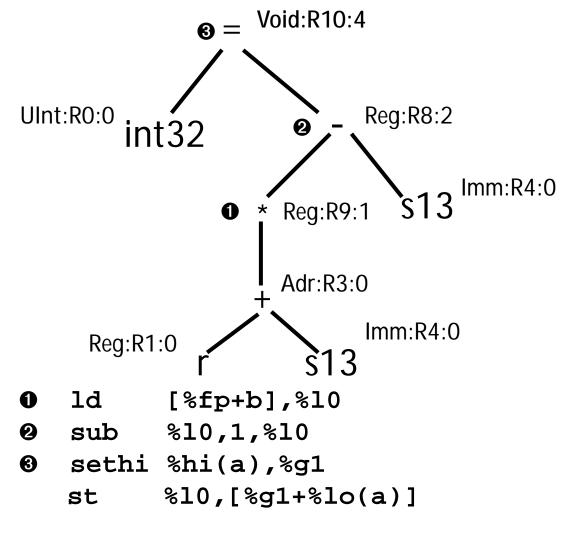

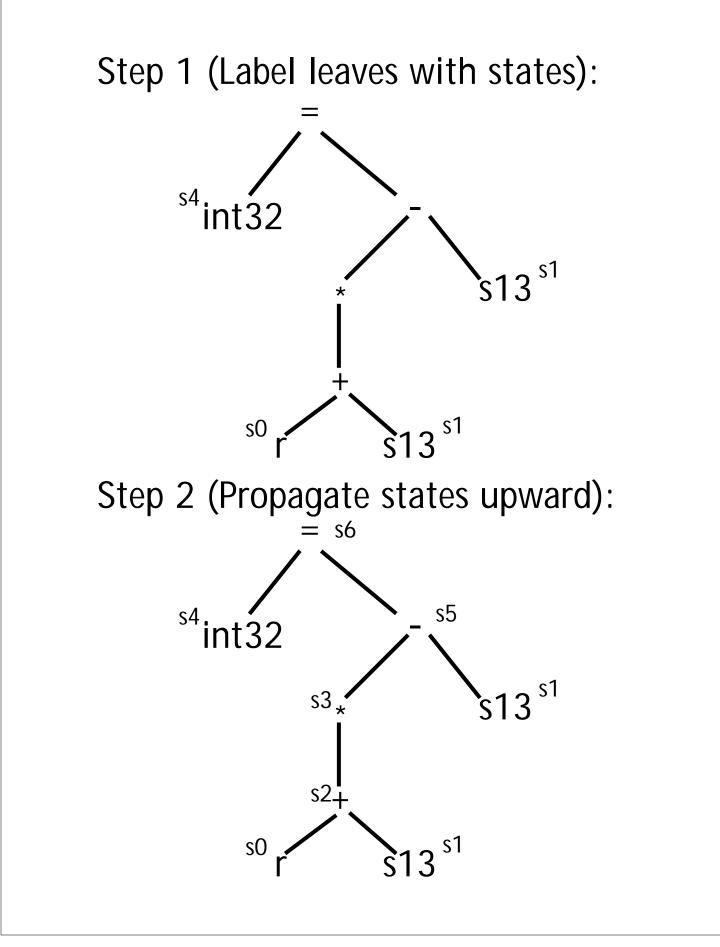

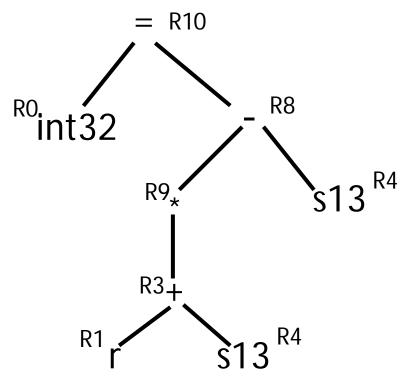

#### 3. Automatic Instruction Selection

How do we map an IR (*Intermediate Representation*) into Machine Instructions? Can we guarantee the *best* instruction sequence?

Idea—Match instruction patterns (represented as trees) against an IR that is a low-level tree. Each match is a generated instruction; the best overall match is the best instruction sequence.

4. Peephole Optimization

Inspect generated code sequences and replace pairs/triples/tuples with better alternatives.

ld [a],%r1 ld [a],%r1

mov const,%r2 add %r1,const,%r3

add %r1,%r2,%r3

(before) (after)

mov 0,%r1OP %g0,%r2,%r3OP %r1,%r2,%r3(after)

But why not just generate the better code sequence to begin with?

5. Cache Improvements

We want to access data & instructions from the L1 cache whenever possible; misses into the L2 cache (or memory) are *expensive*!

We will layout data and program code with consideration of cache sizes and access properties.

6. Local & Global Optimizations

Identify unneeded or redundant code.

Decide where to place code.

Worry about debugging issues (how reliable are current values and source line numbers after optimization?)

#### 7. Program representations

- Control Flow Graphs

- Program Dependency Graphs

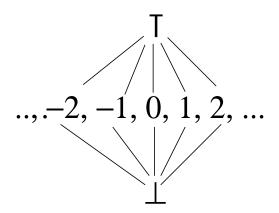

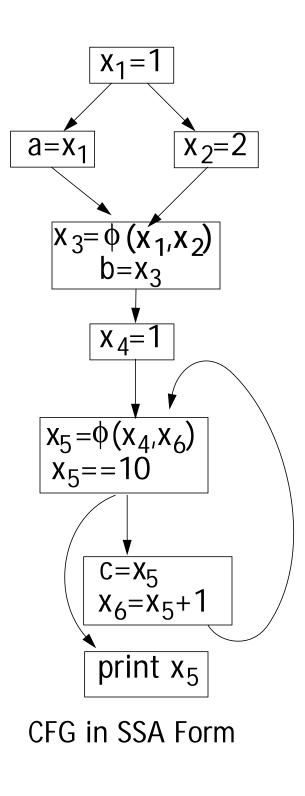

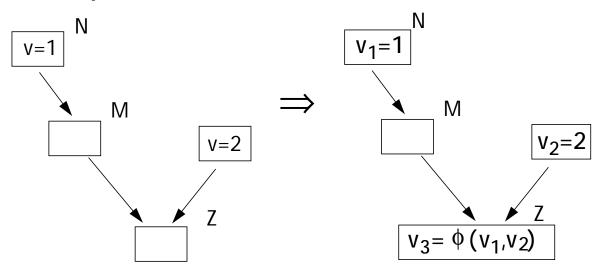

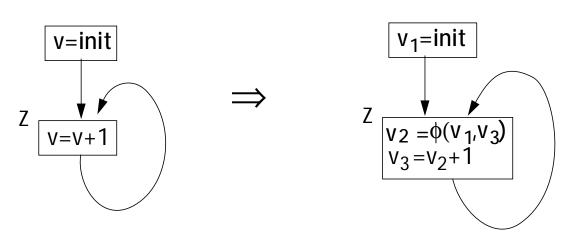

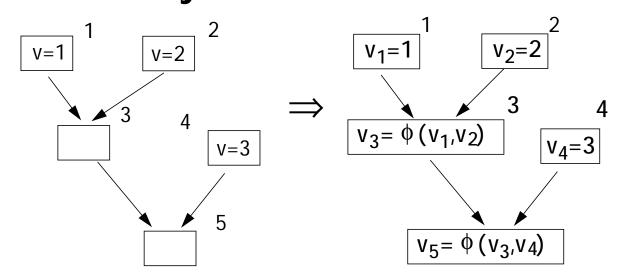

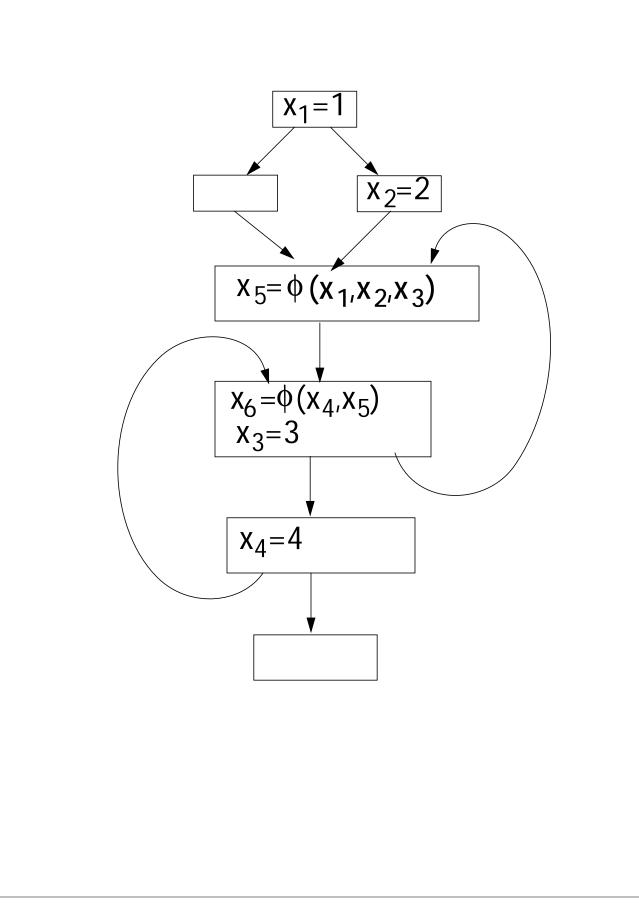

- Static Single Assignment Form (SSA)

Each program variable is assigned to in only one place.

After an assignment x<sub>i</sub> = y<sub>j</sub>, the relation x<sub>i</sub> = y<sub>j</sub> always holds.

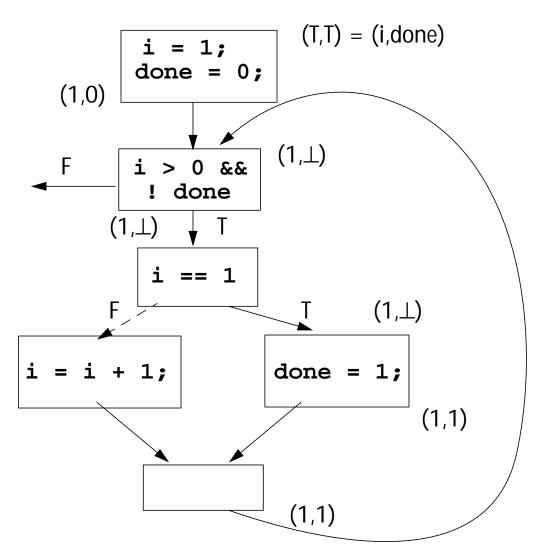

Example:

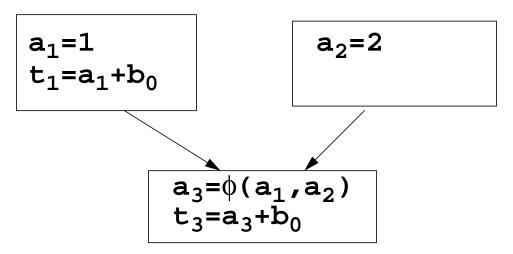

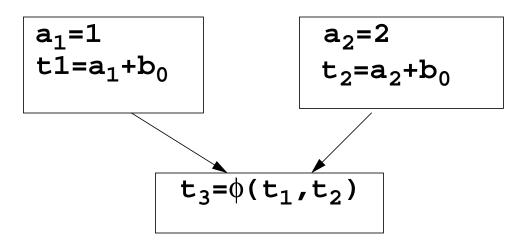

| if (a)           | if (a)                                            |  |

|------------------|---------------------------------------------------|--|

| $\mathbf{x} = 1$ | $\mathbf{x}_1$ =1                                 |  |

| else $x = 2;$    | else $x_2 = 2;$                                   |  |

| print(x)         | $\mathbf{x}_3 = \phi(\mathbf{x}_1, \mathbf{x}_2)$ |  |

|                  | $print(x_3)$                                      |  |

#### 8. Data Flow Analysis

Determine invariant properties of subprograms; analysis can be extended to entire programs.

Model abstract execution.

Prove correctness and efficiency properties of analysis algorithms.

### Review of Compiler Optimizations

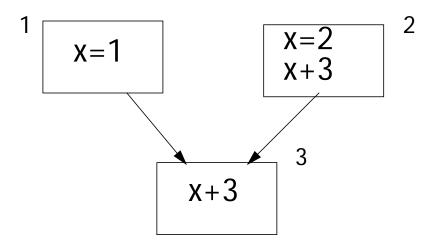

1. Redundant Expression Elimination (Common Subexpression Elimination)

Use an address or value that has been previously computed. Consider control and data dependencies.

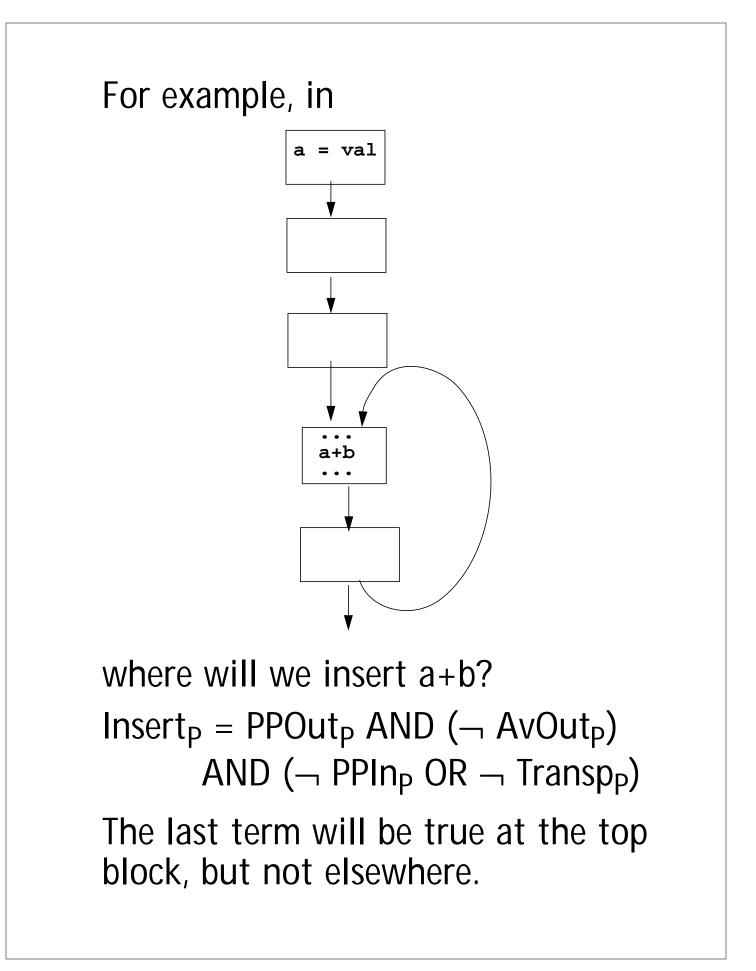

2. Partially Redundant Expression (PRE) Elimination

A variant of Redundant Expression Elimination. If a value or address is redundant along *some* execution paths, add computations to other paths to create a fully redundant expression (which is then removed).

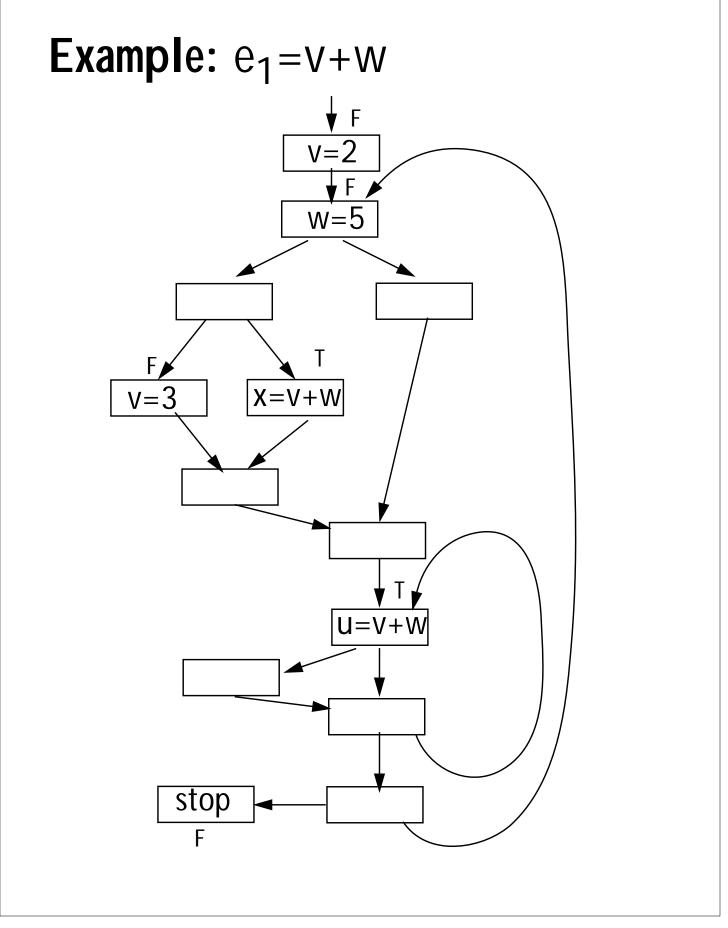

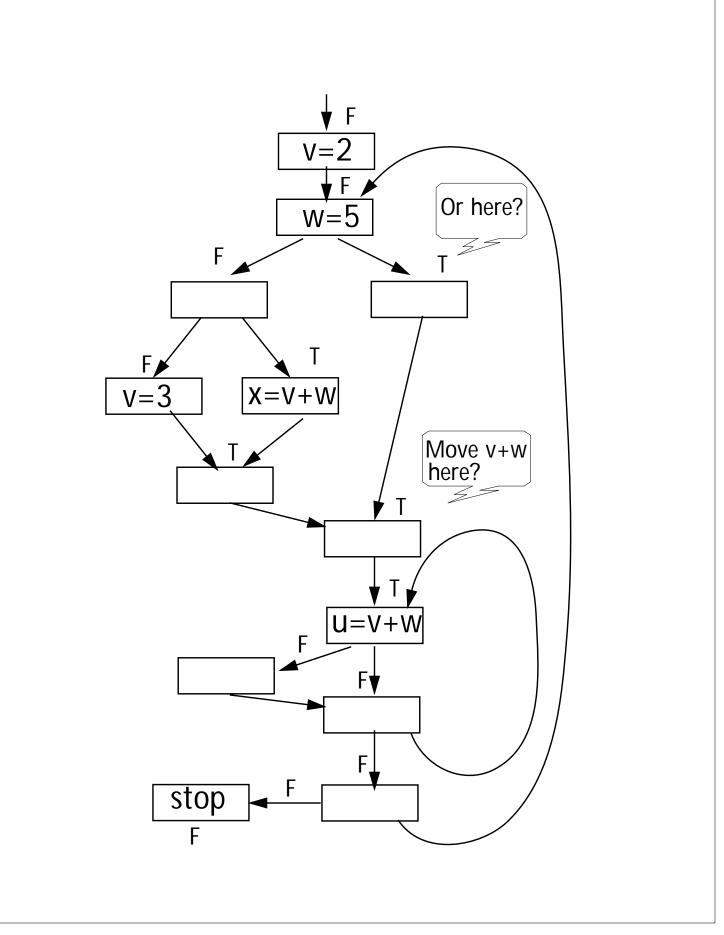

Example:

```

if (i > j)

```

```

a[i] = a[j];

```

```

a[i] = a[i] * 2;

```

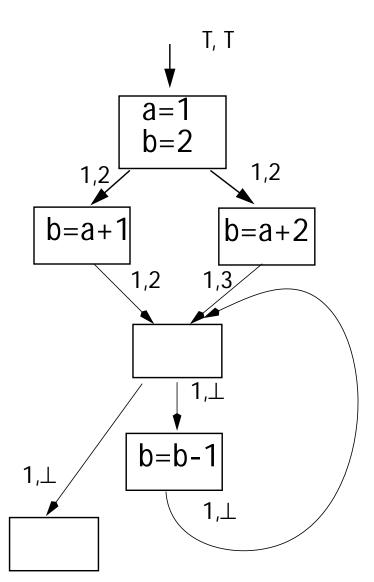

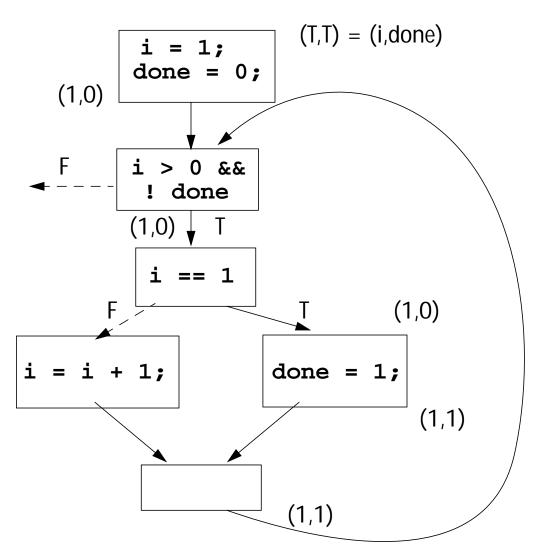

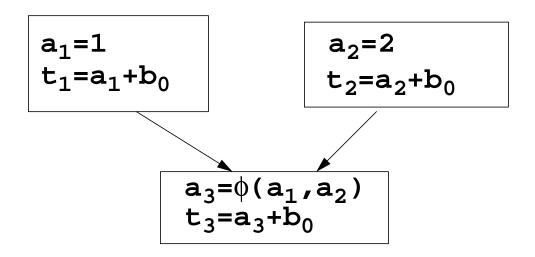

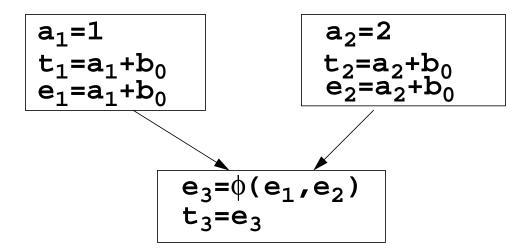

#### 3. Constant Propagation

If a variable is known to contain a particular constant value at a particular point in the program, replace references to the variable at that point with that constant value.

#### 4. Copy Propagation

After the assignment of one variable to another, a reference to one variable may be replaced with the value of the other variable (until one or the other of the variables is reassigned).

(This may also "set up" dead code elimination. Why?)

#### 5. Constant Folding

An expression involving constant (literal) values may be evaluated and simplified to a constant result value. Useful when constant propagation is performed.

### 6. Dead Code Elimination

Expressions or statements whose values or effects are unused may be eliminated.

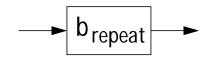

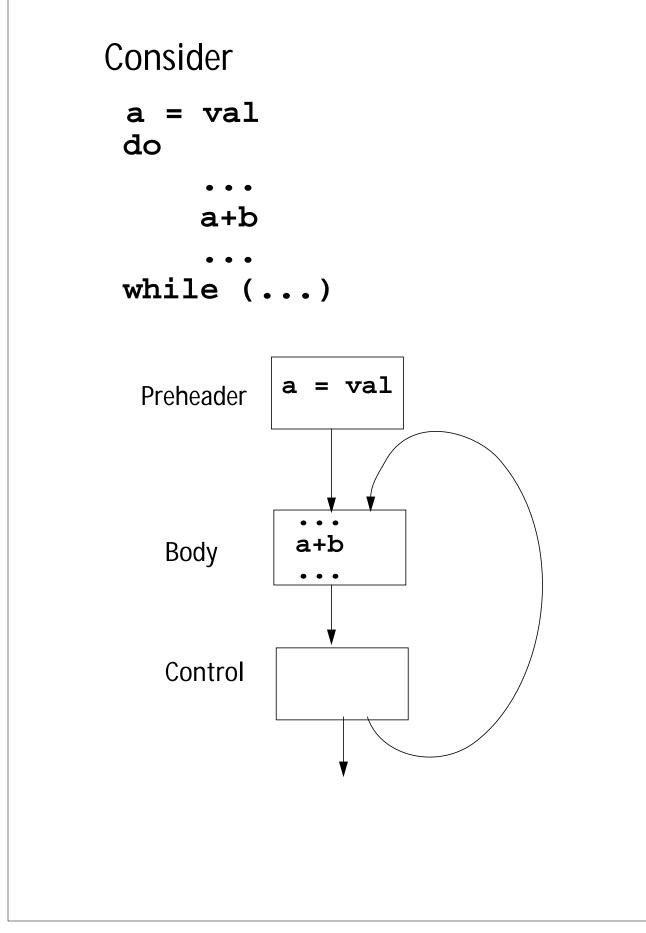

#### 7. Loop Invariant Code Motion

An expression that is *invariant* in a loop may be moved to the loop's header, evaluated once, and reused within the loop. *Safety* and *profitability* issues may be involved.

#### 8. Scalarization (Scalar Replacement)

A field of a structure or an element of an array that is repeatedly read or written may be copied to a local variable, accessed using the local, and later (if necessary) copied back.

This optimization allows the local variable (and in effect the field or array component) to be allocated to a register.

#### 9. Local Register Allocation

Within a *basic block* (a straight line sequence of code) track register contents and reuse variables and constants from registers.

#### 10. Global Register Allocation

Within a subprogram, frequently accessed variables and constants are allocated to registers. Usually there are *many more* register candidates than available registers.

#### 11. Interprocedural Register Allocation

Variables and constants accessed by more than one subprogram are allocated to registers. This can *greatly* reduce call/return overhead. 12. Register Targeting

Compute values directly into the intended target register.

- 13. Interprocedural Code Motion Move instructions across subprogram boundaries.

- 14. Call Inlining

At the site of a call, insert the body of a subprogram, with actual parameters initializing formal parameters.

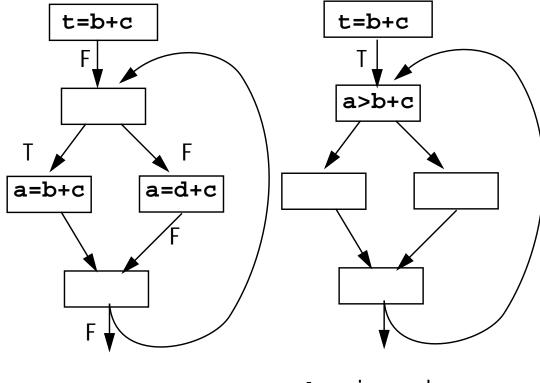

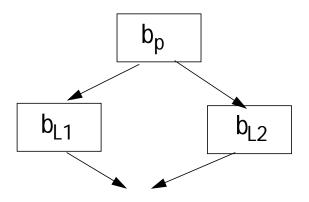

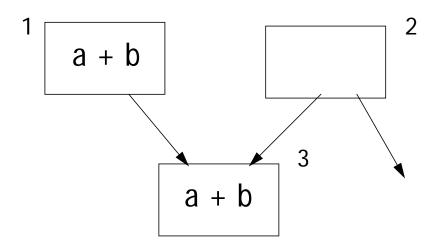

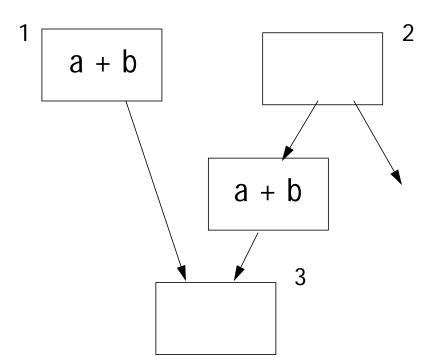

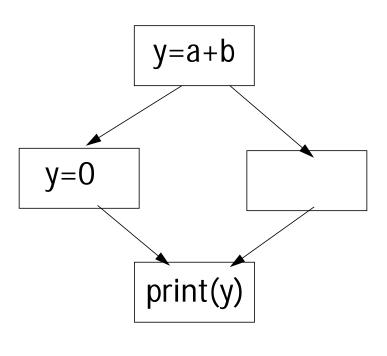

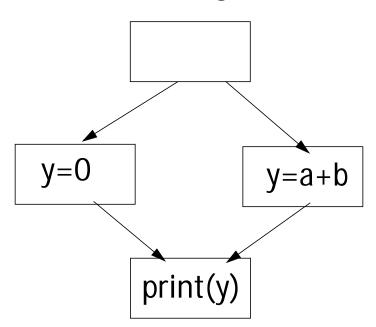

### 15. Code Hoisting and Sinking

If the same code sequence appears in two or more alternative execution paths, the code may be *hoisted* to a common ancestor or *sunk* to a common successor. (This reduces code size, but does not reduce instruction count.)

### 16. Loop Unrolling

Replace a loop body executed N times with an expanded loop body consisting of M copies of the loop body. This expanded loop body is executed N/M times, reducing loop overhead and increasing optimization possibilities within the expanded loop body.

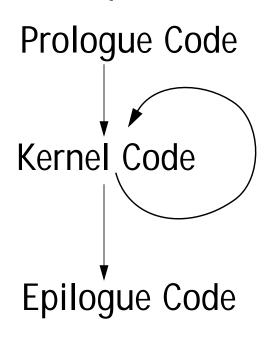

#### 17. Software Pipelining

A value needed in iteration *i* of a loop is computed during iteration *i*-1 (or *i*-2, ...). This allows long latency operations (floating point divides and square roots, low hit-ratio loads) to execute in parallel with other operations. Software pipelining is sometimes called *symbolic loop unrolling*. 18. Strength Reduction

Replace an expensive instruction with an equivalent but cheaper alternative. For example a division may be replaced by multiplication of a reciprocal, or a list append may be replaced by cons operations.

- 19. Data Cache Optimizations

- Locality Optimizations

Cluster accesses of data values both spacially (within a cache line) and temporally (for repeated use). *Loop interchange* and *loop tiling* improve temporal locality.

Conflict Optimizations

Adjust data locations so that data used consecutively and repeatedly don't share the same cache location.

#### 20. Instruction Cache Optimizations

Instructions that are repeatedly reexecuted should be accessed from the instruction cache rather than the secondary cache or memory. Loops and "hot" instruction sequences should fit within the cache.

Temporally close instruction sequences should not map to conflicting cache locations.

## **Reading Assignment**

• Read "Modern Microprocessors—A 90 Minute Guide!," by Jason Patterson.

### **SPARC** Overview

- SPARC is an acronym for Scalable Processor ARChitecture

- SPARCs are load/store RISC processors

Load/store means only loads and stores access memory directly.

RISC (Reduced Instruction Set Computer) means the architecture is simplified with a limited number of instruction formats and addressing modes.

#### • Instruction format:

#### add %r1,%r2,%r3

Registers are prefixed with a % Result is stored into last operand.

#### ld [adr],%r1

Memory addresses (used only in loads and stores) are enclosed in brackets

Distinctive features include Register

Windows and Delayed Branches

### **Register Windows**

The SPARC provides 32 general-purpose integer registers, denoted as %r0 through %r31.

These 32 registers are subdivided into 4 groups:

| Globals:       | %g0 t0 %g7                 |

|----------------|----------------------------|

| In registers:  | %i0 to %i7                 |

| Locals:        | %10 to %17                 |

| Out registers: | % <b>00</b> to % <b>07</b> |

There are also 32 floating-point registers, **%f0** to **%f31**.

A SPARC processor has an implementationdependent number of *register windows*, each consisting of 16 distinct registers. The "in", "local" and "out" registers that are accessed in a procedure depend on the current register window. The "global" registers are independent of the register windows (as are the floating-point registers).

A register window may be pushed or popped using SPARC **save** and **restore** instructions.

After a register window push, the "out" registers become "in" registers and a fresh set of "local" and "out" registers is created:

Before **save**:

| In    | Local | Out |       |       |

|-------|-------|-----|-------|-------|

| In    | Local | In  | Local | Out   |

| (old) | (old) |     | (new) | (new) |

After save

Why the overlap between "in" and "out" registers? It's a convenient way to pass parameters—the caller puts parameter values in his "out" registers. After a call (and a **save**) these values are *automatically* available as "in" registers in the newly created register window.

SPARC procedure calls normally advance the register window. The "in" and "local" registers become hidden, and the "out" registers become the "in" registers of the called procedure, and new "local" and "out" registers become available.

A register window is advanced using the **save** instruction, and rolled back using the **restore** instruction. These instructions are separate from the procedure **call** and **return** instructions, and can sometimes be optimized away.

For example, a *leaf procedure*—one that contains no calls—can be compiled without use of **save** and **restore** if it doesn't need too many registers. The leaf procedure must then make do with the caller's registers, modifying only those the caller treats as volatile.

### **Register Conventions**

**Global Registers**

**%g0** is unique: It *always* contains 0 and can *never* be changed.

**%g1** to **%g7** have global scope (they are unaffected by **save** and **restore** instructions)

**%g1** to **%g4** are volatile across calls; they may be used between calls.

**%g5** to **%g7** are reserved for special use by the SPARC ABI (application binary interface)

Local Registers

%10 to %17

May be freely used; they are unaffected by deeper calls.

### In Registers

These are also the caller's out registers; they are unaffected by deeper calls.

#### %i0

Contains incoming parameter 1.

Also used to return function value to caller.

#### %i1 to %i5

Contain incoming parameters 2 to 6 (if needed); freely usable otherwise.

%i6 (also denoted as %fp)

Contains frame pointer (stack pointer of caller); it must be preserved.

#### %i7

Contains return address -8 (offset due to delay slot); it must be preserved.

#### Out Registers

Become the in registers for procedures called from the current procedure.

#### %00

Contains outgoing parameter 1.

It also contains the value returned by the called procedure.

It is volatile across calls; otherwise it is freely usable.

#### %**01** t0 %**05**

Contain outgoing parameters 2 to 6 as needed.

These are volatile across calls; otherwise they are freely usable.

%o6 (also denoted as %sp)

Holds the stack pointer (and becomes frame pointer of called routines)

It is reserved; it must *always* be valid (since TRAPs may modify the stack at any time).

%07

Is volatile across calls.

It is loaded with address of caller on a procedure call.

## **Special SPARC Instructions**

#### save %r1,%r2,%r3

#### save %r1,const,%r3

This instruction pushes a register window and does an add instruction (%r3 = %r1+%r2). Moreover, the operands (%r1 and %r2) are from the old register window, while the result (%r3) is in the new window.

Why such an odd definition?

It's ideal to allocate a new register window *and* push a new frame.

In particular,

#### save %sp,-frameSize,%sp

pushes a new register window. It also adds **-frameSize** (the stack grows downward) to the old stack pointer, initializing the new stack pointer. (The old stack pointer becomes the current frame pointer)

#### restore %r1,%r2,%r3

#### restore %r1,const,%r3

This instruction pops a register window and does an add instruction (%r3 = %r1+%r2). Moreover, the operands (%r1 and %r2) are from the *current* register window, while the result (%r3) is in the *old* window.

Again, why such an odd definition? It's ideal to release a register window and place a result in the return register (%o0).

In particular,

#### restore %r1,0,%00

pops a register window. It also moves the contents of %r1 to %o0 (in the caller's register window).

#### call label

This instruction branches to **label** and puts the address of the call into register %o7 (which will become %i7 after a **save** is done).

#### ret

This instruction returns from a subprogram by branching to %i7+8. Why 8 bytes after the address of the call? SPARC processors have delayed branch instructions, so the instruction immediately after a branch (or a call) is executed before the branch occurs! Thus two instructions after the call is the normal return point.

#### mov const,%r1

You can load a small constant (13 bits or less) into a register using a **mov**. (**mov** is actually implemented as an **or** of **const** with %g0).

But how do you load a 32 bit constant? One instruction (32 bits long) isn't enough. Instead you use:

#### sethi %hi(const),%r1

#### or %r1,%lo(const),%r1

That is, you extract the high order 22 bits of **const** (using **%hi**, an assembler operation). **sethi** fills in these 22 bits into **%r1**, clearing the lowest 10 bits. Then **%lo** extracts the 10 low order bits of const, which are or-ed into **%r1**. Loading a 64 bit constant (in SPARC V9, which is a 64 bit processor) is far nastier:

| sethi | %uhi(const),%r <sub>tmp</sub>           |

|-------|-----------------------------------------|

| or    | $r_{tmp}$ ,%ulo(const),%r_{tmp}         |

| sllx  | %r <sub>tmp</sub> ,32,%r <sub>tmp</sub> |

| sethi | %hi(const),%r                           |

| or    | %r,%lo(const),%r                        |

| or    | %r <sub>tmp</sub> ,%r,%r                |

## **Delayed Branches**

In the SPARC, transfers of control (branches, calls and returns) are *delayed*. This means the instruction *after* the branch (or call or return) is executed *before* the transfer of control.

For example, in SPARC code you often see

#### ret

#### restore

The register window restore occurs first, then a return to the caller occurs.

Another example is

call subr

#### mov 3,%00

The load of **subr**'s parameter is placed after the call to **subr**. But the **mov** is done before **subr** is actually called.

### Why are Delayed Branches Part of the SPARC Architecture?

Because of pipelining, several instructions are partially completed before a branch instruction can take effect. Rather than lose the computations already done, one (or more!) partially completed instructions can be allowed to complete before a branch takes effect.

## How does a Compiler Exploit Delayed Branches?

A peephole optimizer or code scheduler looks for an instruction logically before the branch that can be placed in the branch's *delay slot*. The instruction should not affect a conditional branch's branch decision.

| mov 3,%00 | call subr |

|-----------|-----------|

| call subr | mov 3,%00 |

| nop       |           |

| (before)  | (after)   |

Another possibility is to "hoist" the target instruction of a branch into the branch's delay slot.

| call subr  | call subr+4   |

|------------|---------------|

| nop        | mov 100,%11   |

| • • •      | • • •         |

| subr:      | subr:         |

| mov 100,%1 | 1 mov 100,%11 |

| (before)   | (after)       |

Hoisting branch targets doesn't work for conditional branches—we don't want to move an instruction that is executed *sometimes* (when the branch is taken) to a position where it is *always* executed (the delay slot).

## **Annulled Branches**

An *annulled branch* (denoted by a ", a" suffix) executes the instruction in the delay slot *if* the branch is taken, but *ignores* the instruction in the delay slot if the branch isn't taken.

With an annulled branch, a target of a conditional branch can be hoisted into the branch's delay slot.

| bz else     | bz,a else+4 |

|-------------|-------------|

| nop         | mov 100,%11 |

| ! then code | ! then code |

| • • •       | • • •       |

| else:       | else:       |

| mov 100,%11 | mov 100,%11 |

| (before)    | (after)     |

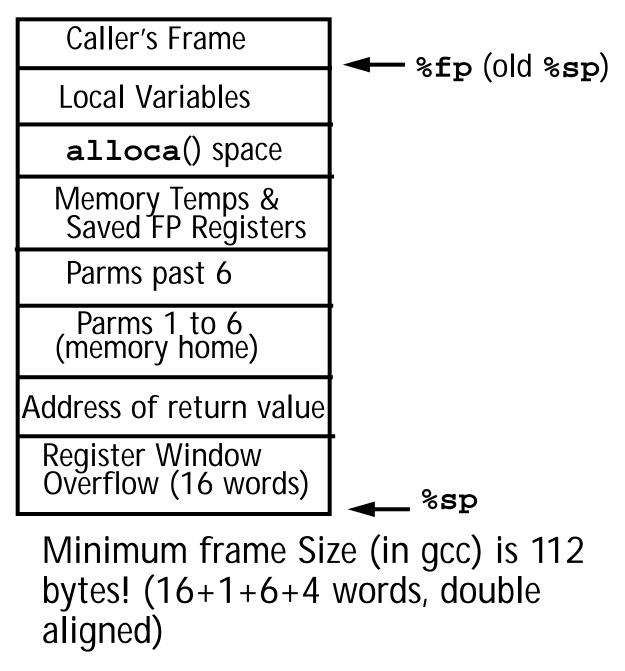

## SPARC Frame Layout (on Run-Time Stack)

The Stack Grows Downward

### **Examples of SPARC Code**

int incr(int i){

return i+1; }

Unoptimized:

incr:

| save | %sp,          | -112,              | %sp |

|------|---------------|--------------------|-----|

| st   | %i0,          | [%fp+0             | 58] |

| ld   | [%fp+         | ۰68], <sup>9</sup> | %o1 |

| add  | %o1,          | 1, %0              | C   |

| mov  | % <b>00</b> , | %i0                |     |

| b    | .LL2          |                    |     |

nop

.LL2:

ret

restore

# int main(){ int a; return incr(a);}

Unoptimized:

main:

| save    | %sp, -120, %sp |

|---------|----------------|

| ld      | [%fp-20], %00  |

| call    | incr, 0        |

| nop     |                |

| mov     | %00, %i0       |

| b       | .LL3           |

| nop     |                |

| .LL3:   |                |

| ret     |                |

| restore |                |

## int incr(int i){ return i+1; }

Optimized: incr: retl add %00, 1, %00

int main(){

int a;

return incr(a);}

#### Optimized:

main:

save %sp, -112, %sp

! Where is a ????

call incr, 0

nop

ret

restore %g0, %o0, %o0

## With More Extensive Optimization (including inlining) we get:

| incr: |      |    |     |  |

|-------|------|----|-----|--|

| retl  |      |    |     |  |

| add   | %o0, | 1, | %00 |  |

|       |      |    |     |  |

| main: |      |    |     |  |

| retl  |      |    |     |  |

| add   | %o0, | 1, | %00 |  |

## **Reading Assignment**

S. Kurlander, T. Proebsting and C. Fischer, "Efficient Instruction Scheduling for Delayed-Load Architectures," *ACM Transactions on Programming Languages and Systems*, 1995. (Linked from class Web page)

## "On the Fly" Local Register Allocation

Allocate registers as needed during code generation.

Partition registers into 3 classes.

Allocatable

Explicitly allocated and freed; used to hold a variable, literal or temporary. On SPARC: Local registers & unused In registers.

Reserved

Reserved for specific purposes by OS or software conventions.

On SPARC: **%fp**, **%sp**, return address register, argument registers, return value register. • Work

Volatile—used in short code sequences that need to use a register.

On SPARC: **%g1** to **%g4**, unused out registers.

## **Register Targeting**

Allow "end user" of a value to state a register preference in AST or IR.

#### Oľ

Use Peephole Optimization to eliminate unnecessary register moves.

#### Oľ

Use *preferencing* in a graph coloring register allocator.

## **Register Tracking**

Improve upon standard getReg/ freeReg allocator by *tracking* (remembering) register contents.

Remember the value(s) currently held within a register; store information in a *Register Association List.*

Mark each value as *Saved* (in memory) or *Unsaved* (in memory).

Each value in a register has a *Cost*. This is the cost (in instructions) to restore the value to a register. The cost of allocating a register is the sum of the costs of the values it holds.

$Cost(register) = \sum_{values \in register} cost(values)$

When we allocate a register, we will choose the *cheapest* one.

If 2 registers have the same cost, we choose that register whose values have the *most distant* next use. (Why most distant?)

## Costs for the SPARC

- 0 Dead Value

- 1 Saved Local Variable

- 1 Small Literal Value (13 bits)

- 2 Saved Global Variable

- 2 Large Literal Value (32 bits)

- 2 Unsaved Local Variable

- 4 Unsaved Global Variable

## **Register Tracking Allocator**

```

reg getReg() {

if (\exists r \in regSet and cost(r) == 0)

choose(r)

else {

c = 1;

while(true) {

if ( \exists r \in regSet and cost(r) == c) {

choose r with cost(r) == c and

most distant next use of

associated values;

break;

}

C++;

}

Save contents of r as necessary;

return r;

}

```

- Once a value becomes dead, it may be purged from the register association list without any saves.

- Values no longer used, but unsaved, can be purged (and saved) at zero cost.

- Assignments of a register to a simple variable may be *delayed*—just add the variable to the Register's Association List entry as unsaved.

The assignment may be done later or made *unnecessary* (by a later assignment to the variable)

• At the end of a basic block all unsaved values are stored into memory.

## Example

```

int a,b,c,d; // Globals

a = 5;

b = a + d;

c = b - 7;

b = 10;

```

### Naive Code

| mov        | 5,%10                         |

|------------|-------------------------------|

| st         | %10,[a]                       |

| ld         | [a],%10                       |

| ld         | [d],%11                       |

| add        | %10 <b>,</b> %11 <b>,</b> %10 |

| st         | %10,[b]                       |

| ld         | [b],%10                       |

| sub        | %10 <b>,</b> 7 <b>,</b> %10   |

| st         | %10,[c]                       |

| mov        | 10,%10                        |

| st         | %10,[b]                       |

| 18 instruc | tions are needed (memory      |

|            | take 2 instructions)          |

## With Register Tracking

| Instruction Generated      | %10        | %11         |

|----------------------------|------------|-------------|

| mov 5,%10                  | 5(S)       |             |

| ! Defer assignment to a    | 5(S), a(U) |             |

| ld [d], %11                | 5(S), a(U) | d(S)        |

| !d unused after next inst  |            |             |

| add %10,%11,%11            | 5(S), a(U) | b(U)        |

| !b is dead after next inst |            |             |

| sub %11,7,%11              | 5(S), a(U) | c(U)        |

| ! %11 has lower cost       |            |             |

| st %11, [c]                | 5(S), a(U) |             |

| mov 10, %11                | 5(S), a(U) | b(U), 10(S) |

| ! save unsaved values      |            |             |

| st %10, [a]                |            | b(U), 10(S) |

| st %11,[b]                 |            |             |

12 instructions (rather than 18)

## Pointers, Arrays and Reference Parameters

When an array, reference parameter or pointed-to variable is read, all unsaved register values that might be aliased must be *stored*.

When an array, reference parameter or pointed-to variable is written, all unsaved register values that might be aliased must be *stored*, then *cleared* from the register association list.

Thus if a[3] is in a register and a[i] is assigned to, a[3] must be stored (if unsaved) and removed from the association list.

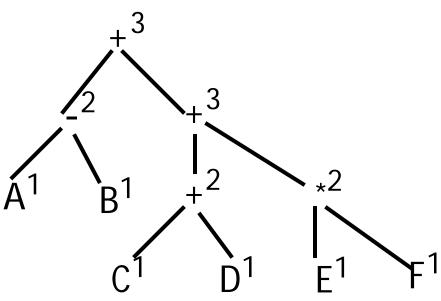

### Optimal Expression Tree Translation—Sethi-Ullman Algorithm

Reference: R. Sethi & J. D. Ullman, "The generation of optimal code for arithmetic expressions," Journal of the ACM, 1970.

Goal: Translate an expression tree using the *fewest* possible registers.

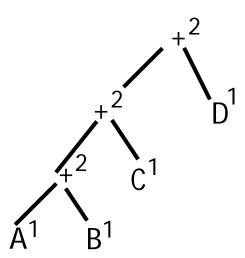

Approach: Mark each tree node, N, with an *Estimate* of the minimum number of registers needed to translate the tree rooted by N.

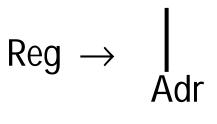

Let RN(N) denote the Register Needs of node N.

In a Load/Store architecture (ignoring immediate operands):

RN(leaf) = 1

RN(Op) = If RN(Left) = RN(Right) Then RN(Left) + 1 Else Max(RN(Left), RN(Right)

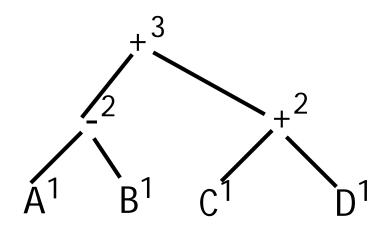

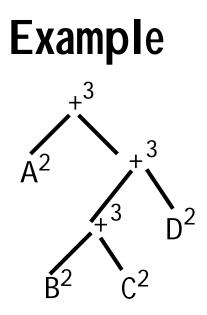

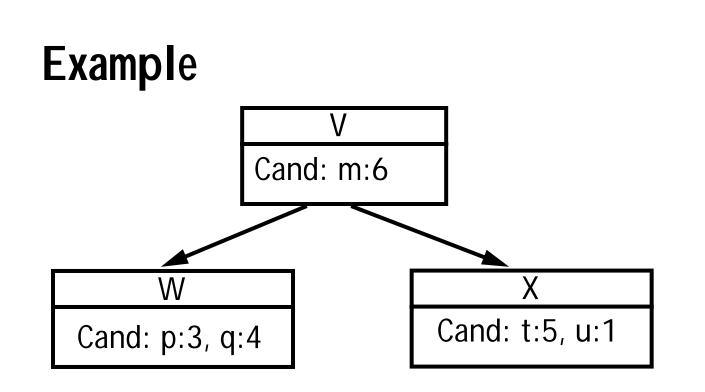

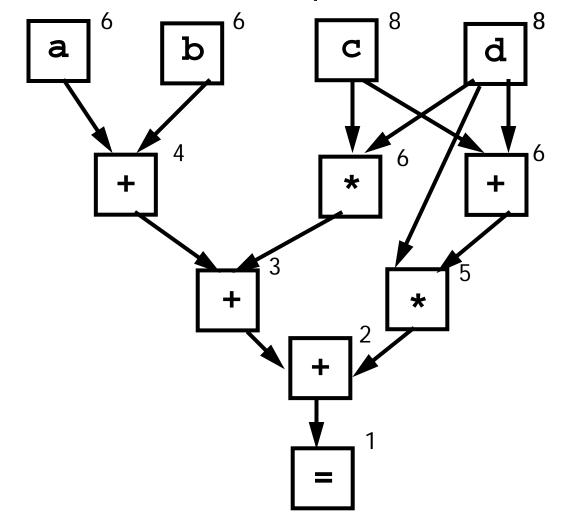

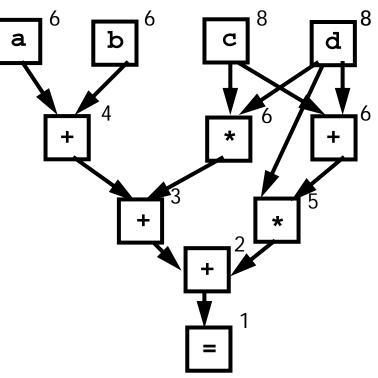

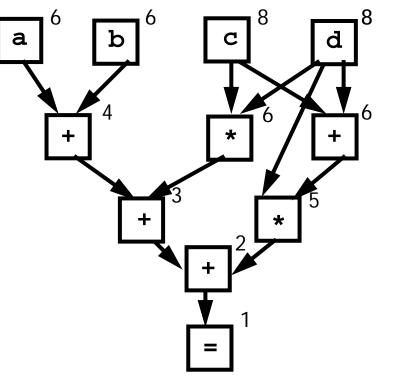

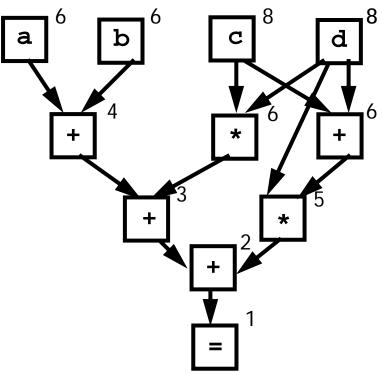

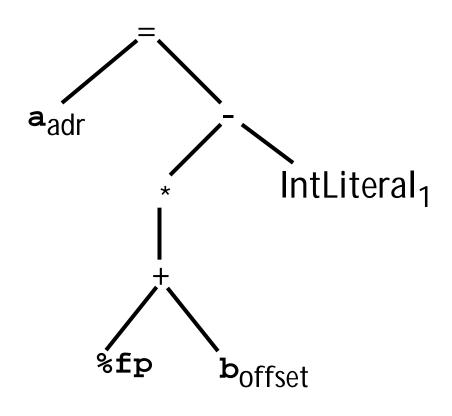

Example:

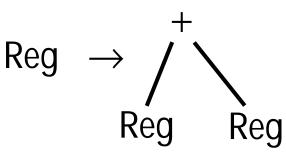

## Key Insight of SU Algorithm

Translate subtree that needs more registers *first*.

Why?

After translating one subtree, we'll need a register to hold its value.

If we translate the more complex subtree first, we'll still have enough registers to translate the less complex expression (without *spilling* register values into memory).

## Specification of SU Algorithm

TreeCG(tree \*T, regList RL);

Operation:

- Translate expression tree T using only registers in RL.

- RL must contain at least 2 registers.

- Result of T will be computed into head(RL).

## Summary of SU Algorithm

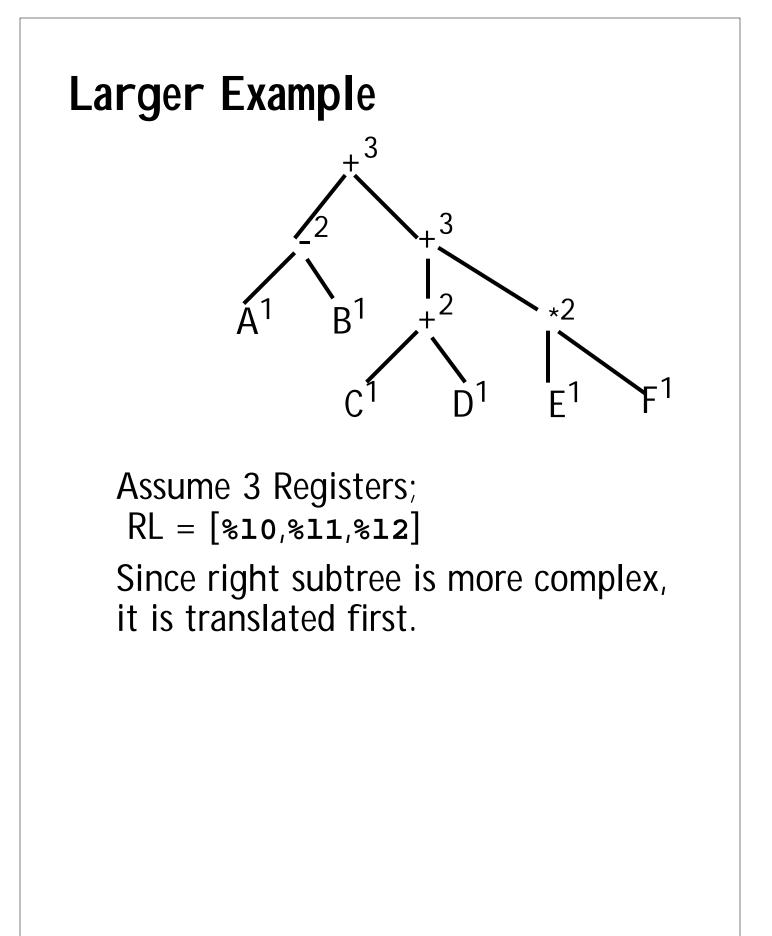

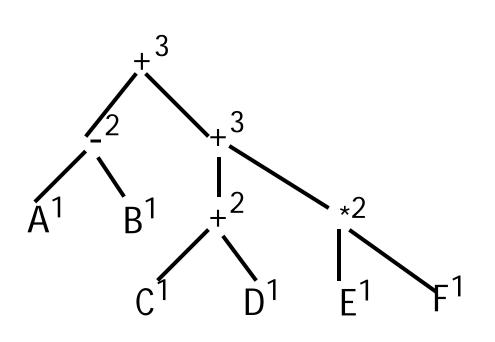

if T is a node (variable or literal) load T into R1 = head(RL)else (T is a binary operator) Let R1 = head(RL)Let R2 = second(RL)if RN(T.left) >= Size(RL) and RN(T.right) >= Size(RL) (A spill is unavoidable) TreeCG(T.left, RL) Store R1 into a memory temp TreeCG(T.right, RL) Load memory temp into R2 Generate (OP R2,R1,R1) elsif RN(T.left) >= RN(T.right)TreeCG(T.left, RL) TreeCG(T.right, tail(RL)) Generate (OP R1,R2,R1) else TreeCG(T.right, RL) TreeCG(T.left, tail(RL)) Generate (OP R2,R1,R1)

## Example (with Spilling)

Assume only 2 Registers; RL = [%10,%11]

We Translate the left subtree first (using 2 registers), store its result into memory, translate the right subtree, reload the left subtree's value, then do the final operation.

1d [A], %10

1d [B], %11

sub %10,%11,%10

st %10, [temp]

1d [C], %10

1d [D], %11

add %10,%11,%10

1d [temp], %11

add %11,%10,%10

| ld  | [C], %10    |

|-----|-------------|

| ld  | [D], %11    |

| add | %10,%11,%10 |

| ld  | [E], %l1    |

| ld  | [F], %12    |

| mul | %11,%12,%11 |

| add | %10,%11,%10 |

| ld  | [A], %l1    |

| ld  | [B], %12    |

| sub | %11,%12,%11 |

| add | %11,%10,%10 |

## **Refinements & Improvements**

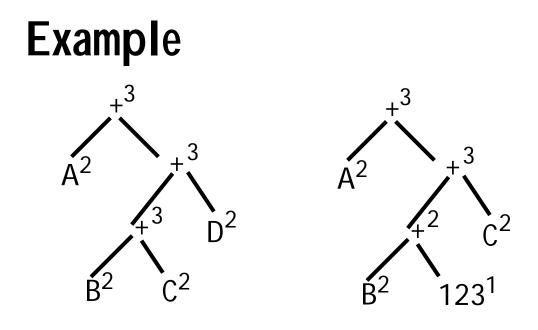

• Register needs rules can be modified to model various architectural features.

For example, Immediate operands, that need not be loaded into registers, can be modeled by the following rule:

RN(literal) = 0 if literal may be used as an immediate operand

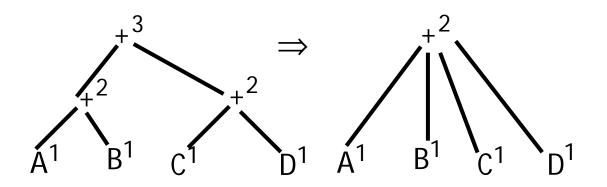

Commutativity & Associativity of operands may be exploited:

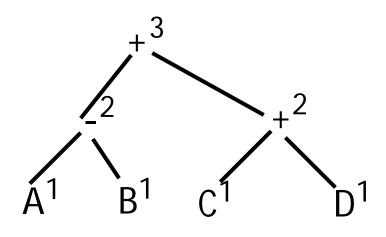

#### Is Minimizing Register Use Always Wise?

SU minimizes the *number* of registers used but at the *cost* of reduced ILP.

Since only 2 registers are used, there is little possibility of parallel evaluation.

When more registers are used, there is often more potential for parallel evaluation:

Here as many as *four* registers may be used to increase parallelism.

## **Reading Assignment**

- Read Section 15.3 (Register Allocation and Temporary Management) from Chapter 15

- Get Class Handout 3 from DOIT.

- Read Chaitin's paper, "Register Allocation via Coloring."

## Optimal Translation for DAGs is Much Harder

If variables or expression values may be *shared* and *reused*, optimal code generation becomes NP-Complete.

Example: a+b\*(c+d)+a\*(c+d)

We must decide how long to hold each value in a register. Best orderings may "skip" between subexpressions

Reference: R. Sethi, "Complete Register Allocation Problems," *SIAM Journal of Computing*, 1975.

### Scheduling Expression Trees

Reference: S. Kurlander, T. Proebsting and C. Fischer, "Efficient Instruction Scheduling for Delayed-Load Architectures," *ACM Transactions on Programming Languages and Systems*, 1995. (Linked from class Web page)

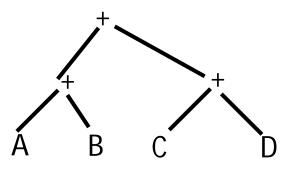

The Sethi-Ullman Algorithm minimizes register usage, without regard to code scheduling.

On machines with *Delayed Loads*, we also want to avoid stalls.

## What is a Delayed Load?

Most pipelined processors require a delay of one or more instructions between a load of register R and the first use of R.

If a register is used "too soon," the processor may stall execution until the register value becomes available.

#### ld [a],%r1

$\leftarrow$  Stall!

add %r1,1,%r1

We try to place an instruction that doesn't use register R immediately after a load of R.

This allows useful work instead of a wasteful stall.

In fact, if we use the fewest possible registers, stalls are *Unavoidable*!

## Why?

Loads increase the number of registers in use.

Binary operations decrease the number of registers in use (2 Operands, 1 Result).

The load that brings the number of registers in use up to the minimum number needed *must* be followed by an operator that uses the just-loaded value. This implies a stall.

We'll need to allocate an *extra register* to allow an independent instruction to fill each delay slot of a load.

#### **Extended Register Needs**

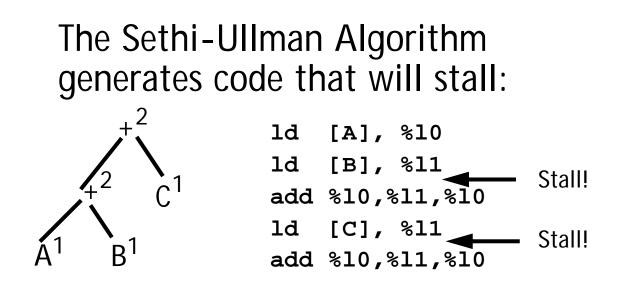

Abbreviated as *ERN* ERN(Identifier) = 2 ERN(Literal) = 1 ERN(Op) = If ERN(Left) = ERN(Right) Then ERN(Left) + 1 Else Max(ERN(Left), ERN(Right))

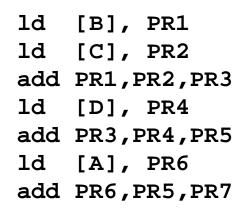

## Idea of the Algorithm

- Generate instructions in the same order as Sethi-Ullman, but use Pseudo-Registers instead of actual machine registers.

- 2. Put generated instructions into a "Canonical Order" (as defined below).

- 3. Map pseudo-registers to actual machine registers.

## What are Pseudo-Registers?

They are unique temporary locations, unlimited in number and generated as needed, that are used to model registers prior to register allocation.

#### Canonical Form for Expression Code

(Assume R registers will be used) Desired instruction ordering:

- 1. R load instructions

- 2. Pairs of Operator/Load instructions

- 3. Remaining operators

This canonical form is obtained by "sliding" load instructions upward (earlier) in the original code ordering. Note that:

- Moving loads upward is *always* safe, since each pseudo-register is assigned to only once.

- No more than R registers are ever live.

Let R = 3, the minimum needed for a delay-free schedule. Put into Canonical Form:

ld [B], %10

ld [C], %11

ld [D], %12

add %10,%11,%10

ld [A], %11

add %10,%12,%10

add %11,%10,%10

(After Register Assignment)

No Stalls!

#### Does This Algorithm Always Produce a Stall-Free, Minimum Register Schedule?

Yes—if one exists!

For very simple expressions (one or two operands) no stall-free schedule exists.

For example: **a=b;**

| ld | [b], | %10 |

|----|------|-----|

| st | %10, | [a] |

## Why Does the Algorithm Avoid Stalls?

Previously, certain "critical" loads had to appear just before an operation that used their value.

Now, we have an "extra" register. This allows critical loads to move up one or more places, avoiding any stalls.

## How Do We Schedule Small Expressions?

Small expressions (one or two operands) are common. We'd like to avoid stalls when scheduling them.

Idea—Blend small expressions together into larger expression trees, using "," and ";" like binary operators.

## **Global Register Allocation**

Allocate registers across an entire subprogram.

A Global Register Allocator must decide:

- What values are to be placed in registers?

- Which registers are to be used?

- For how long is each *Register Candidate* held in a register?

### Live Ranges

Rather than simply allocate a value to a fixed register throughout an entire subprogram, we prefer to *split* variables into *Live Ranges*.

What is a Live Range?

It is the span of instructions (or basic blocks) from a definition of a variable to all its uses.

Different assignments to the same variable may reach distinct & disjoint instructions or basic blocks.

If so, the live ranges are *Independent*, and may be assigned *Different* registers.

#### Example

```

a = init();

for (int i = a+1; i < 1000; i++){

b[i] = 0; }

a = f(i);

print(a);

```

The two uses of variable **a** comprise *Independent* live ranges.

Each can be allocated separately.

If we insisted on allocating variable **a** to a fixed register for the whole subprogram, it would *conflict* with the loop body, greatly reducing its chances of successful allocation.

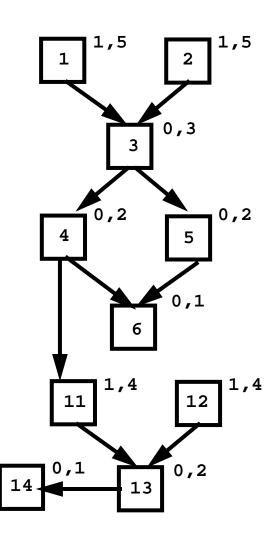

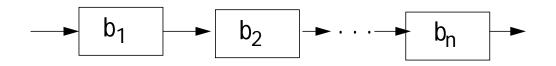

## Granulatity of Live Ranges

Live ranges can be measured in terms of individual instructions or basic blocks.

Individual instructions are more precise but basic blocks are less numerous (reducing the size of sets that need to be computed).

We'll use basic blocks to keep examples concise.

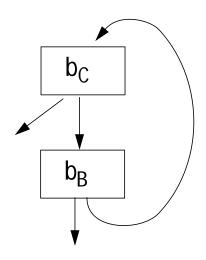

You can define basic blocks that hold only one instruction, so computation in terms of basic blocks is still fully general.

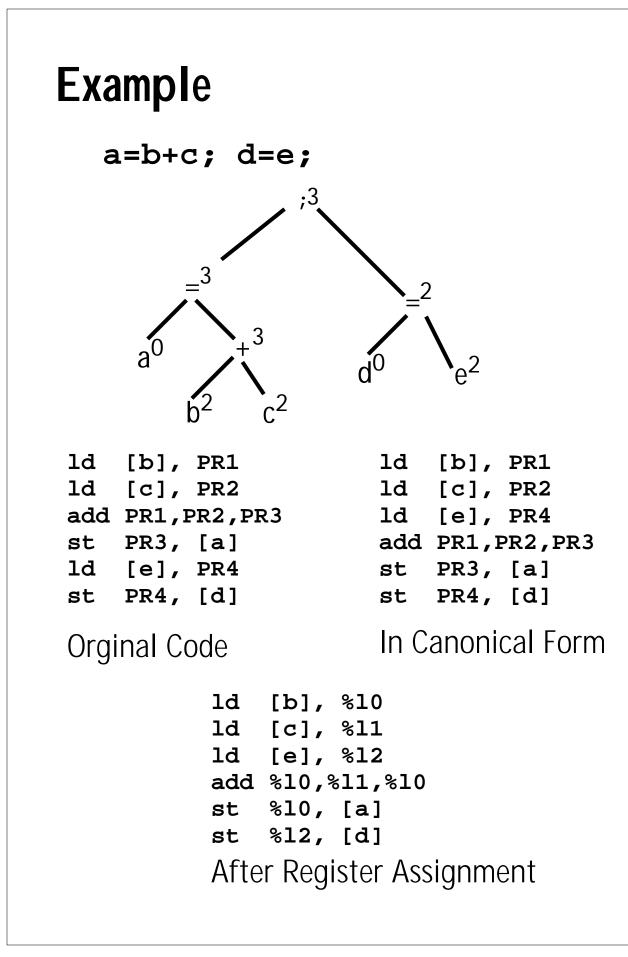

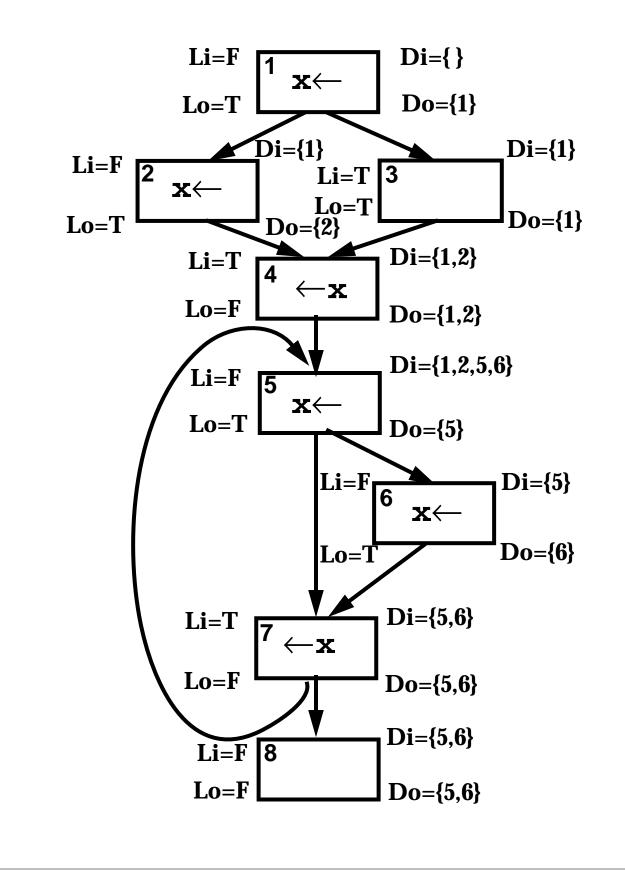

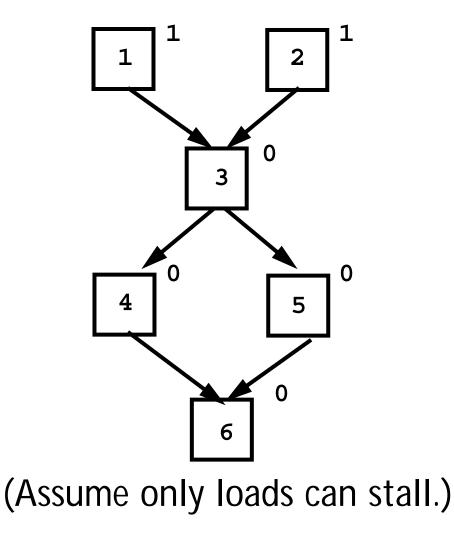

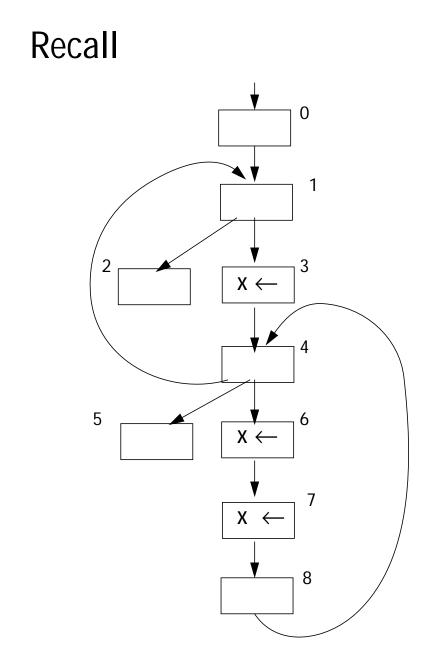

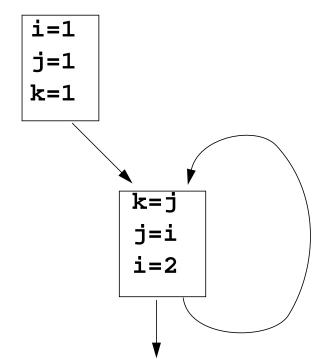

### **Computation of Live Ranges**

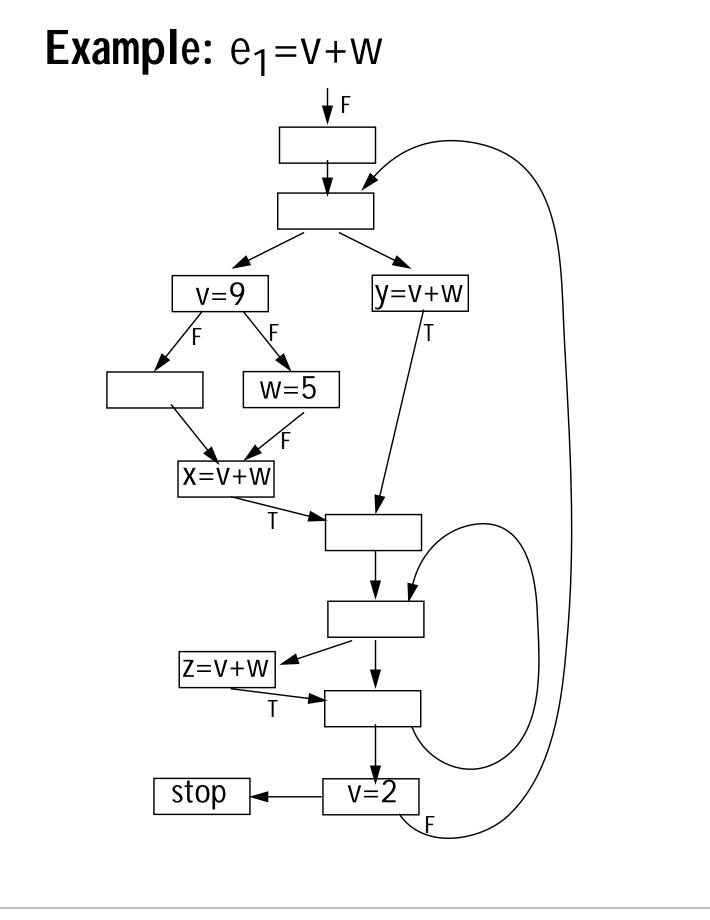

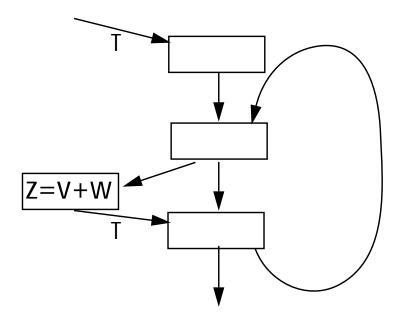

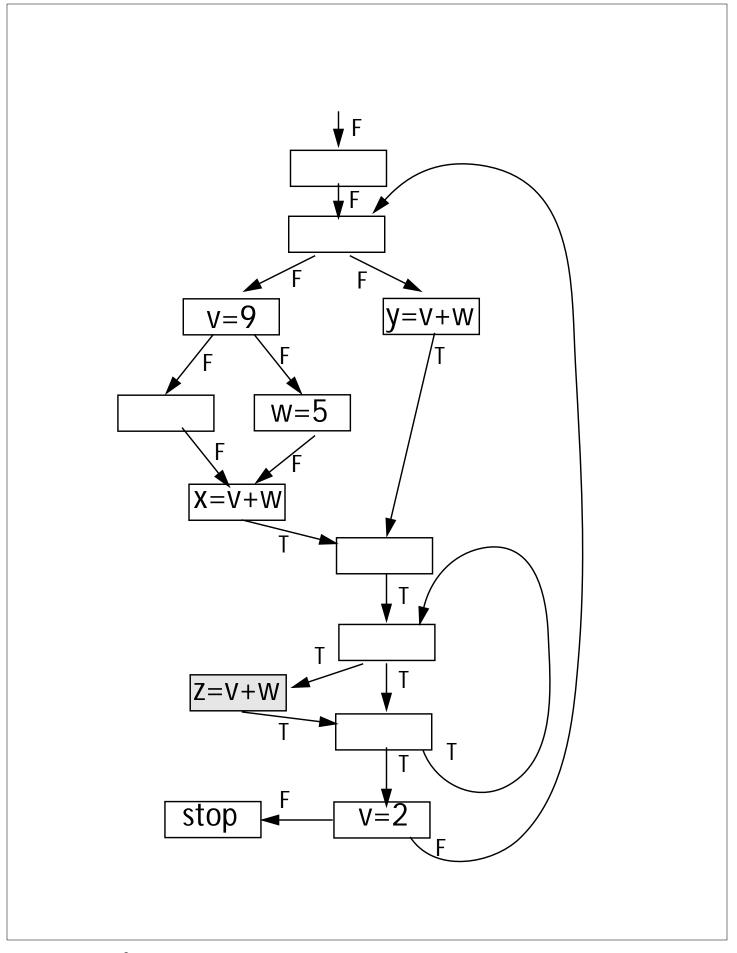

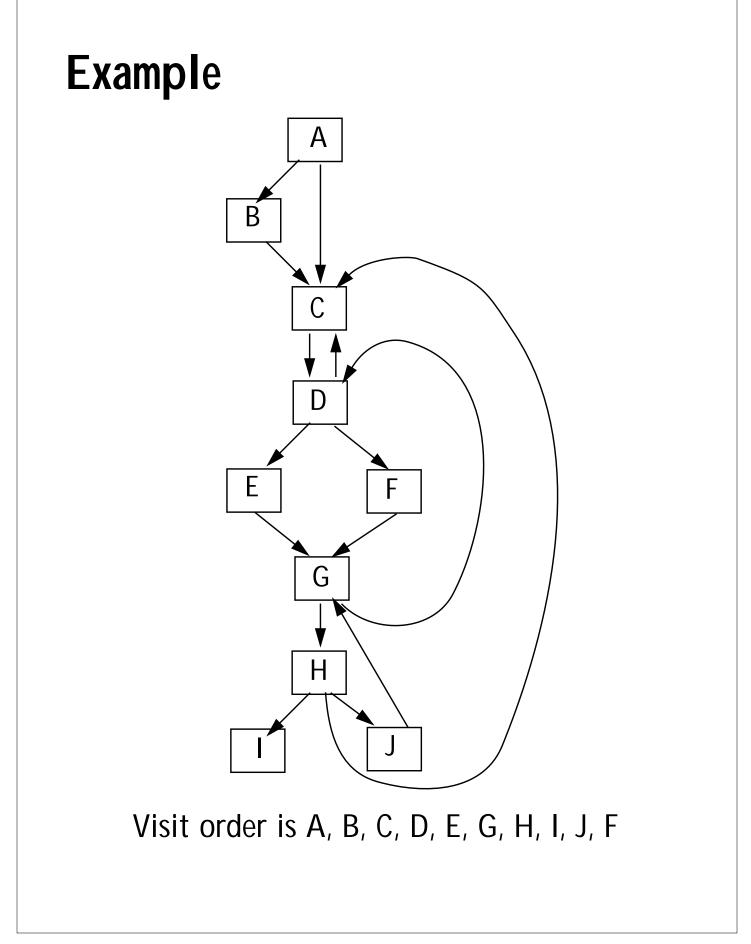

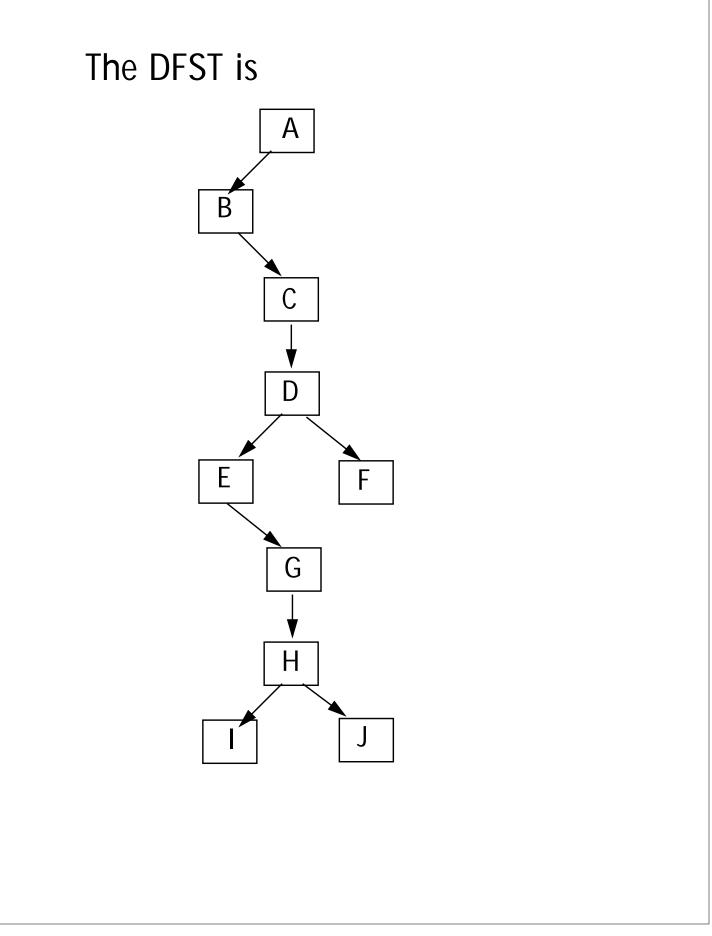

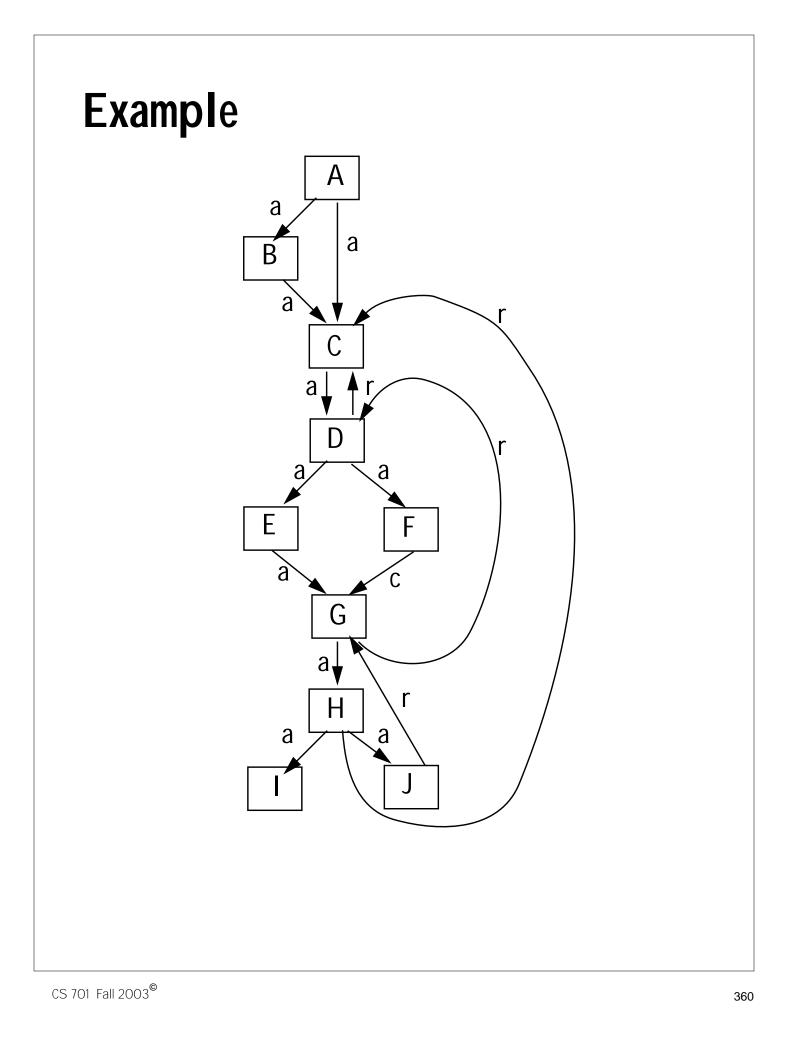

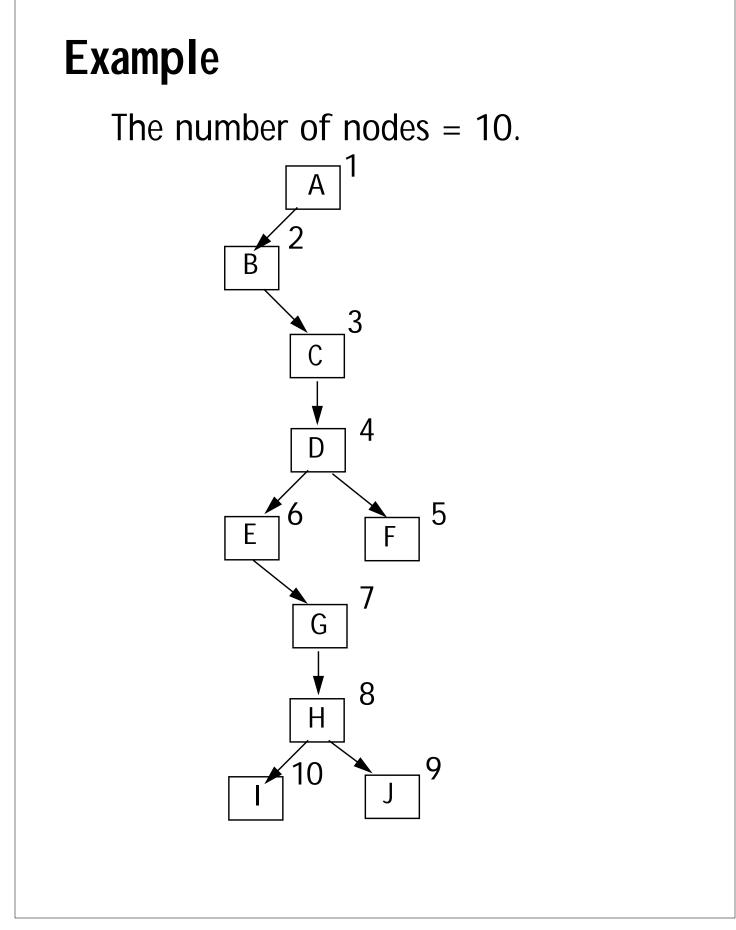

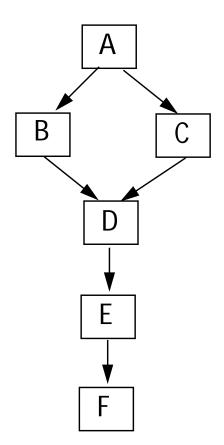

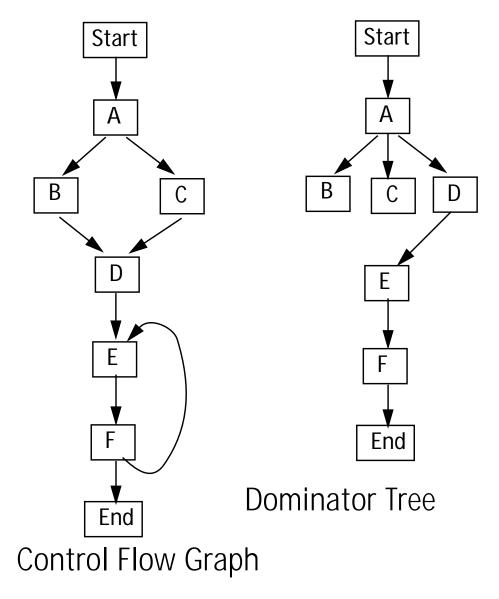

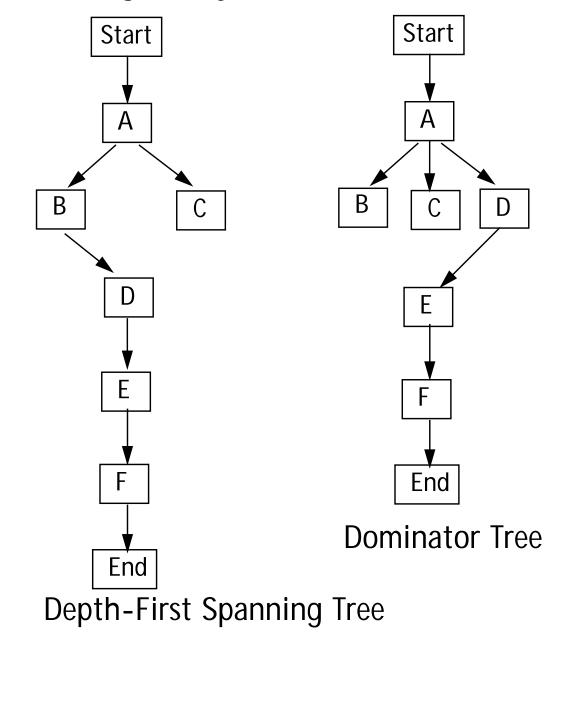

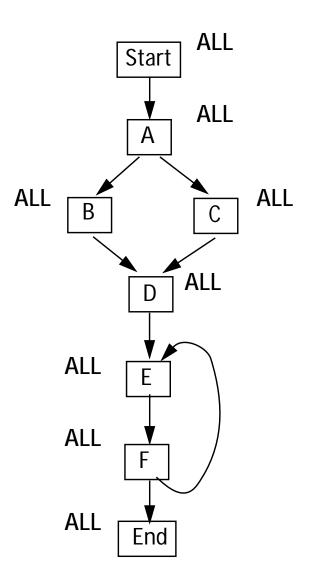

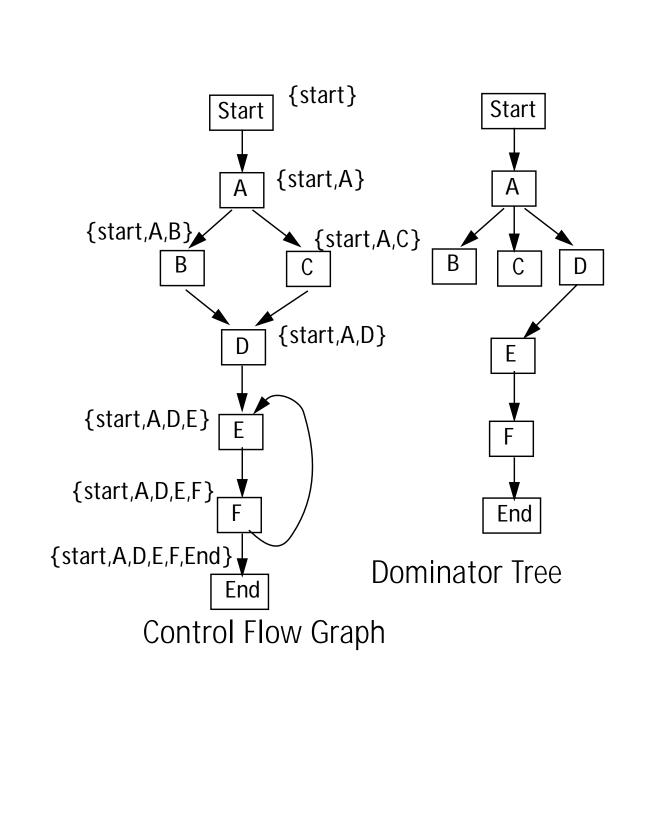

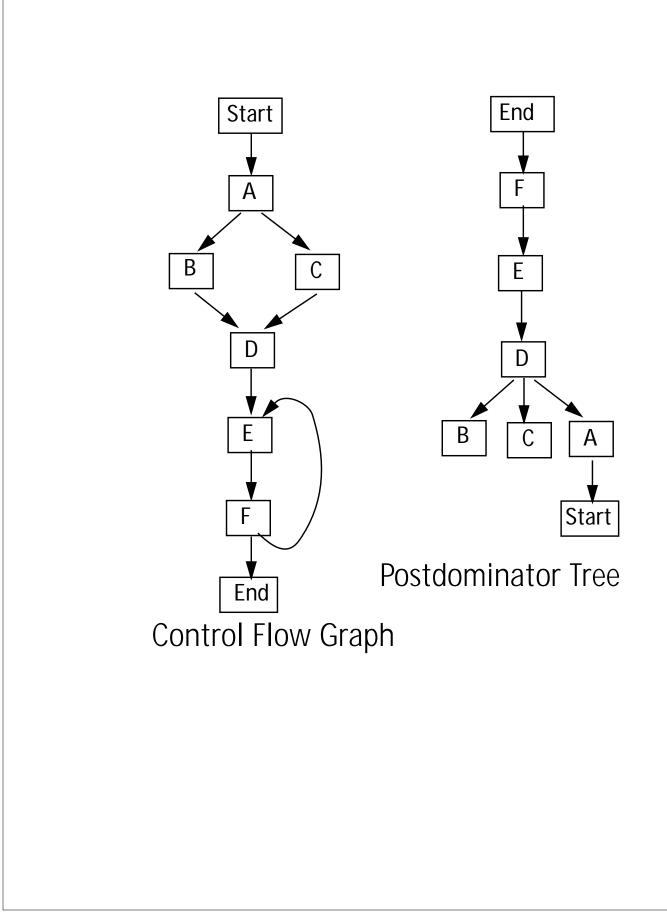

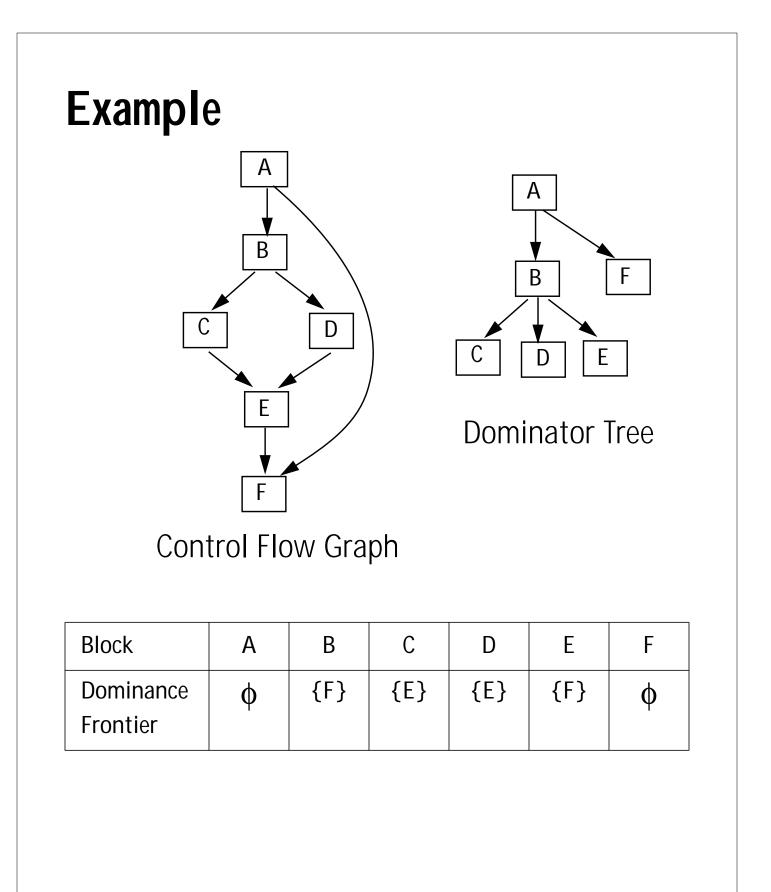

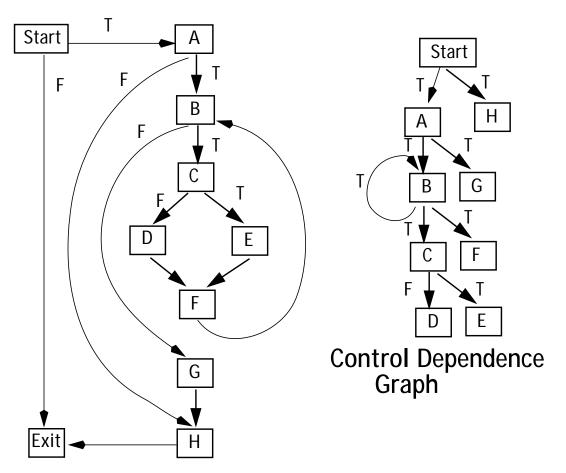

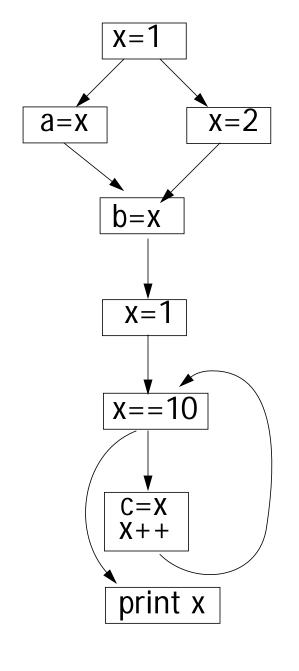

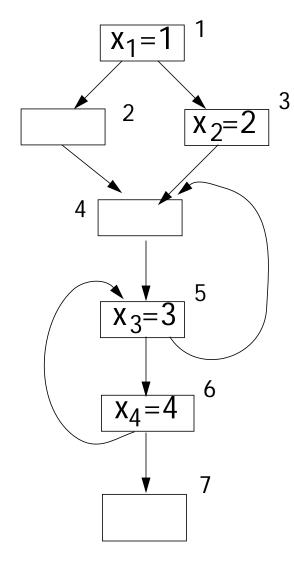

First construct the Control Flow Graph (CFG) of the subprogram.

For a Basic Block b:

- Let Preds(b) = the set of basic blocks that are Immediate Predecessors of b in the CFG.

- Let Succ(b) = the set of basic blocks that are Immediate Successors to b in the CFG.

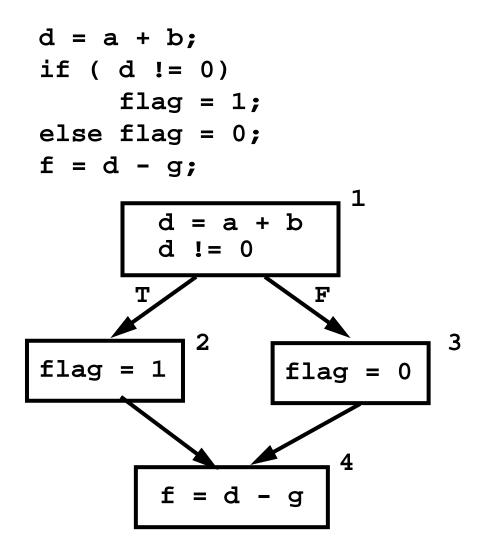

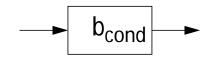

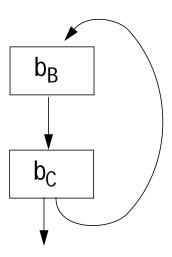

### **Control Flow Graphs**

A Control Flow Graph (CFG) models possible execution paths through a program.

Nodes are basic blocks and arcs are potential transfers of control.

For a Basic Block b and Variable V: Let DefsIn(b) = the set of basic blocks that contain definitions of V that reach (may be used in) the beginning of Basic Block b.

Let DefsOut(b) = the set of basic blocks that contain definitions of V that reach (may be used in) the end of Basic Block b.

If a definition of V reaches b, then the register that holds the value of that definition must be allocated to V in block b.

Otherwise, the register that holds the value of that definition may be used for other purposes in b.

The sets Preds and Succ are derived from the structure of the CFG.

They are given as part of the definition of the CFG.

DefsIn and DefsOut must be computed, using the following rules:

- 1. If Basic Block b contains a definition

of V then

DefsOut(b) = {b}

- 2. If there is no definition to V in b then DefsOut(b) = DefsIn(b)

- 3. For the First Basic Block,  $b_0$ : DefsIn( $b_0$ ) =  $\phi$

- 4. For all Other Basic Blocks  $DefsIn(b) = \bigcup_{p \in Preds(b)} DefsOut(p)$

## **Reading Assignment**

- Read George and Appel's paper, "Iterated Register Coalescing." (Linked from Class Web page)

- Read Larus and Hilfinger's paper, "Register Allocation in the SPUR Lisp Compiler."

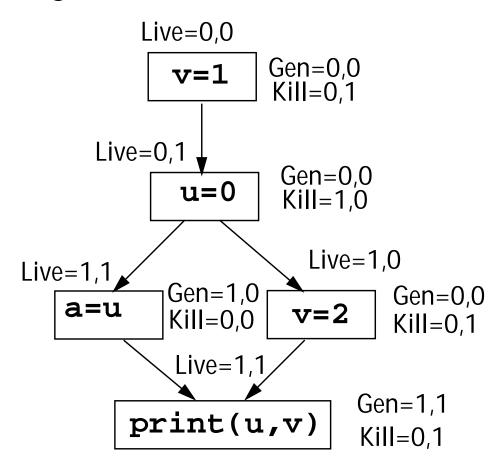

## **Liveness Analysis**

Just because a definition reaches a Basic Block, b, *does not* mean it must be allocated to a register at b.

We also require that the definition be *Live* at b. If the definition is dead, then it will no longer be used, and register allocation is unnecessary.

For a Basic Block b and Variable V: Liveln(b) = true if V is Live (will be used before it is redefined) at the beginning of b.

LiveOut(b) = true if V is Live (will be used before it is redefined) at the end of b. LiveIn and LiveOut are computed, using the following rules:

- 1. If Basic Block b has no successors then LiveOut(b) = false

- 2. For all Other Basic Blocks

```

LiveOut(b) = \bigvee LiveIn(s)

s \in Succ(b)

```

```

3. Liveln(b) =

If V is used before it is defined in

Basic Block b

Then true

Elsif V is defined before it is

used in Basic Block b

Then false

Else LiveOut(b)

```

## **Merging Live Ranges**

It is possible that each Basic Block that contains a definition of v creates a *distinct* Live Range of V.

∀ Basic Blocks, b, that contain a definition of V:

Range(b) =  $\{b\} \cup \{k \mid b \in Defsln(k) \& Liveln(k)\}$

This rule states that the Live Range of a definition to V in Basic Block b is b plus all other Basic Blocks that the definition of V reaches and in which V is live. If two Live Ranges overlap (have one of more Basic Blocks in common), they *must* share the same register too. (Why?)

Therefore,

```

If Range(b<sub>1</sub>) \cap Range(b<sub>2</sub>) \neq \phi

Then replace

```

Range(b<sub>1</sub>) and Range(b<sub>2</sub>) with Range(b<sub>1</sub>)  $\cup$  Range(b<sub>2</sub>)

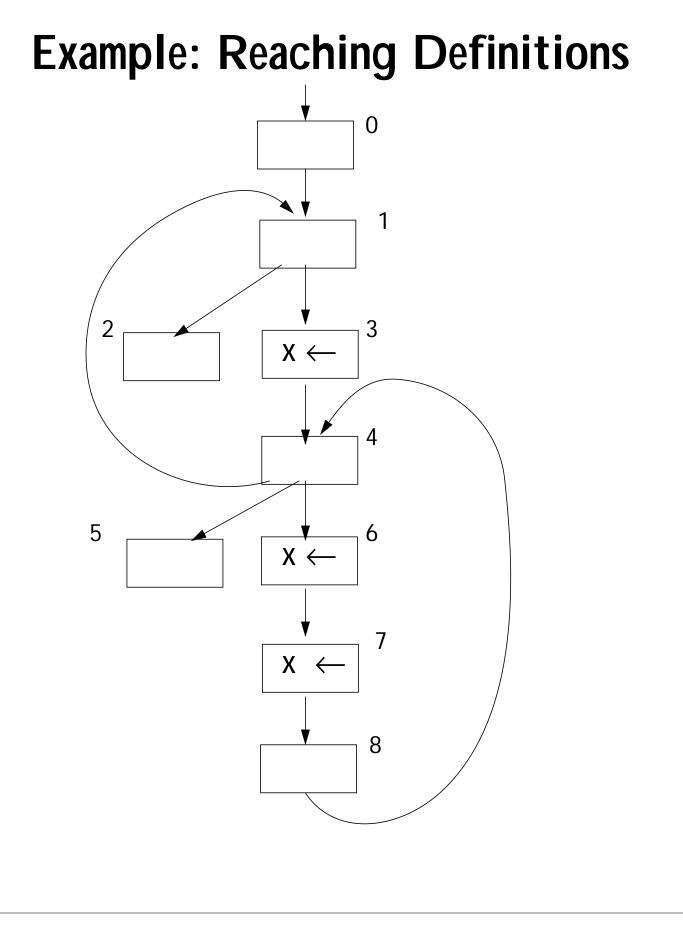

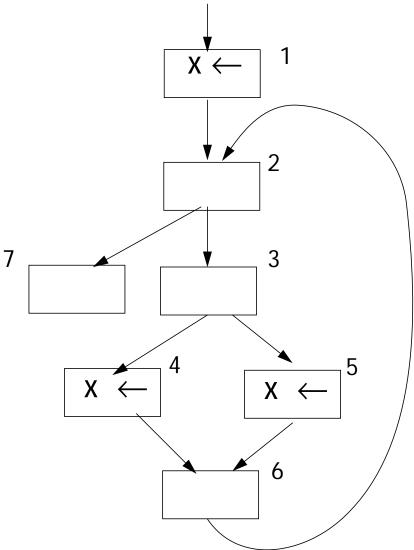

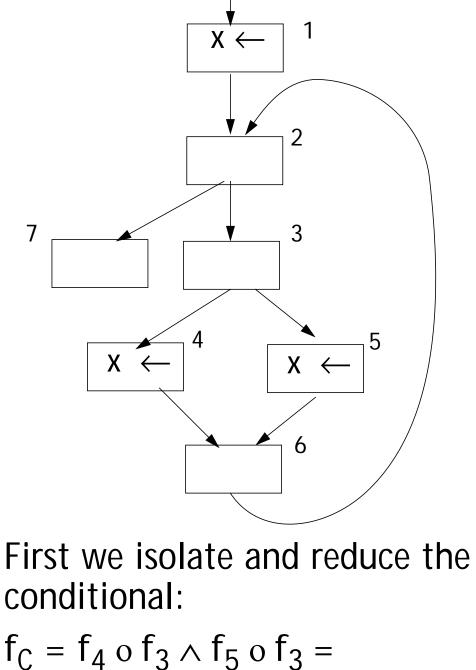

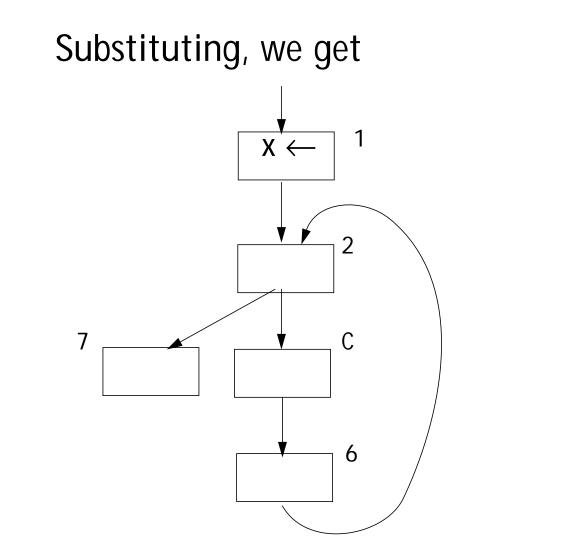

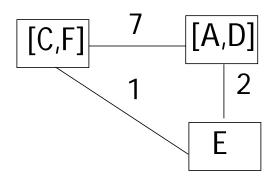

The Live Ranges we Compute are Range(1) =  $\{1\} \cup \{3,4\} = \{1,3,4\}$ Range(2) =  $\{2\} \cup \{4\} = \{2,4\}$ Range(5) =  $\{5\} \cup \{7\} = \{5,7\}$ Range(6) =  $\{6\} \cup \{7\} = \{6,7\}$ Ranges 1 and 2 overlap, so  $Range(1) = Range(2) = \{1, 2, 3, 4\}$ Ranges 5 and 6 overlap, so  $Range(5) = Range(6) = \{5, 6, 7\}$

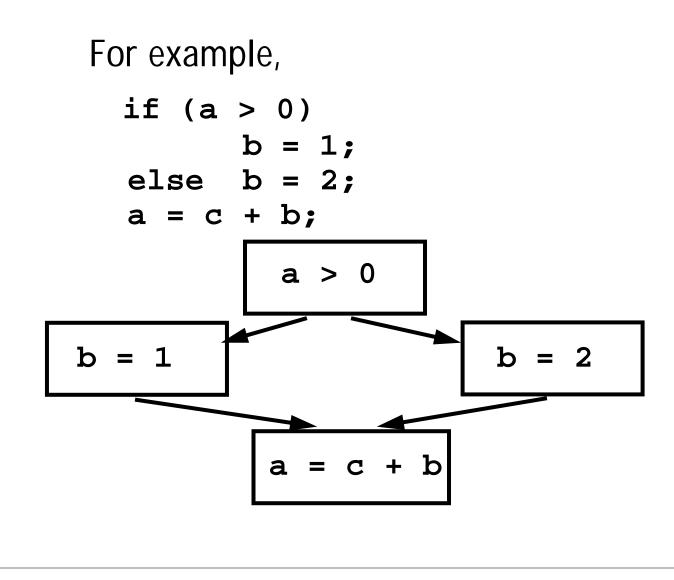

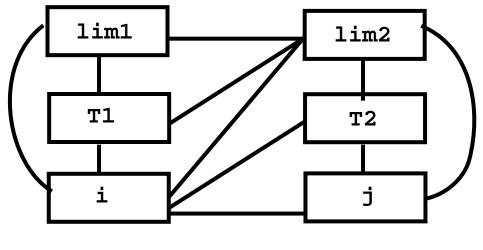

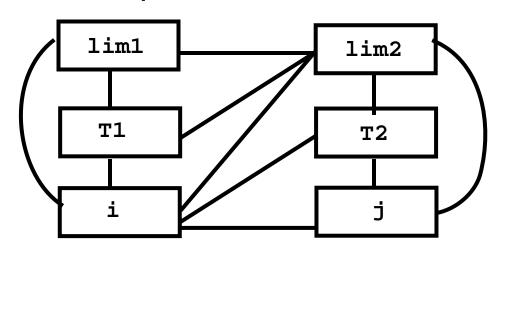

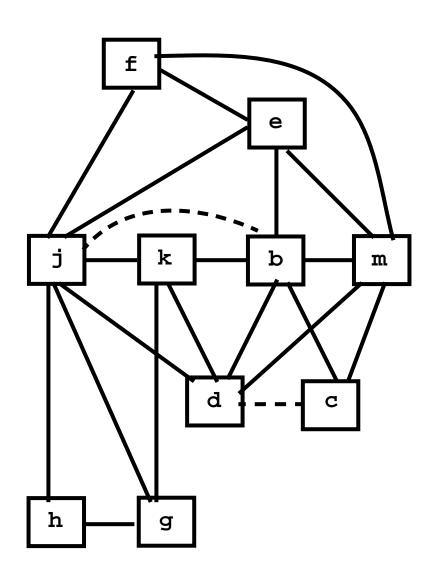

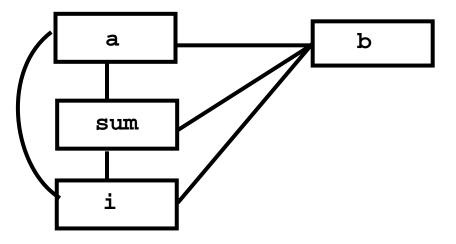

### Interference Graph

An *Interference Graph* represents interferences between Live Ranges.

Two Live Ranges *interfere* if they share one or more Basic Blocks in common.

Live Ranges that interfere *must* be allocated different registers.

In an Interference Graph:

- Nodes are Live Ranges

- An undirected arc connects two Live Ranges if and only if they interfere

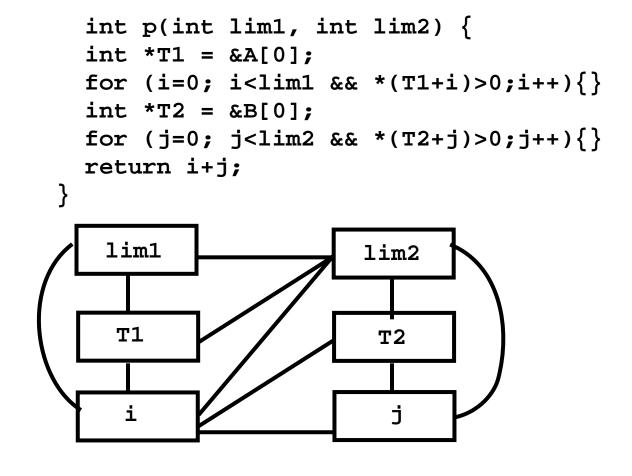

#### Example

```

int p(int lim1, int lim2) {

for (i=0; i<lim1 && A[i]>0;i++){}

for (j=0; j<lim2 && B[j]>0;j++){}

return i+j;

}

```

We optimize array accesses by placing **&A[0]** and **&B[0]** in temporaries:

```

int p(int lim1, int lim2) {

int *T1 = &A[0];

for (i=0; i<lim1 && *(T1+i)>0;i++){}

int *T2 = &B[0];

for (j=0; j<lim2 && *(T2+j)>0;j++){}

return i+j;

}

```

# Register Allocation via Graph Coloring

We model global register allocation as a Coloring Problem on the Interference Graph

We wish to use the fewest possible colors (registers) subject to the rule that two connected nodes can't share the same color.

## Optimal Graph Coloring is NP-Complete

Reference:

"Computers and Intractability," M. Garey and D. Johnson, W.H. Freeman, 1979.

We'll use a Heuristic Algorithm originally suggested by Chaitin et. al. and improved by Briggs et. al.

References:

"Register Allocation Via Coloring," G. Chaitin et. al., Computer Languages, 1981.

"Improvement to Graph Coloring Register Allocation," P. Briggs et. al., PLDI, 1989.

# **Coloring Heuristic**

To R-Color a Graph (where R is the number of registers available)

- While any node, n, has < R neighbors: Remove n from the Graph. Push n onto a Stack.

- 2. If the remaining Graph is non-empty: Compute the Cost of each node. The Cost of a Node (a Live Range) is the number of extra instructions needed if the Node isn't assigned a register, scaled by 10<sup>loop\_depth</sup>. Let NB(n) =

Number of Neighbors of n. Remove that node n that has the smallest Cost(n)/NB(n) value. Push n onto a Stack. Return to Step 1. 3. While Stack is non-empty: Pop n from the Stack.

> If n's neighbors are assigned fewer than R colors

Then assign n any unassigned color Else leave n uncolored.

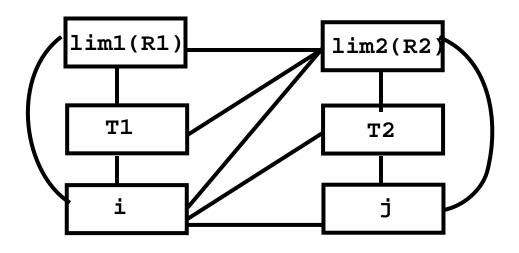

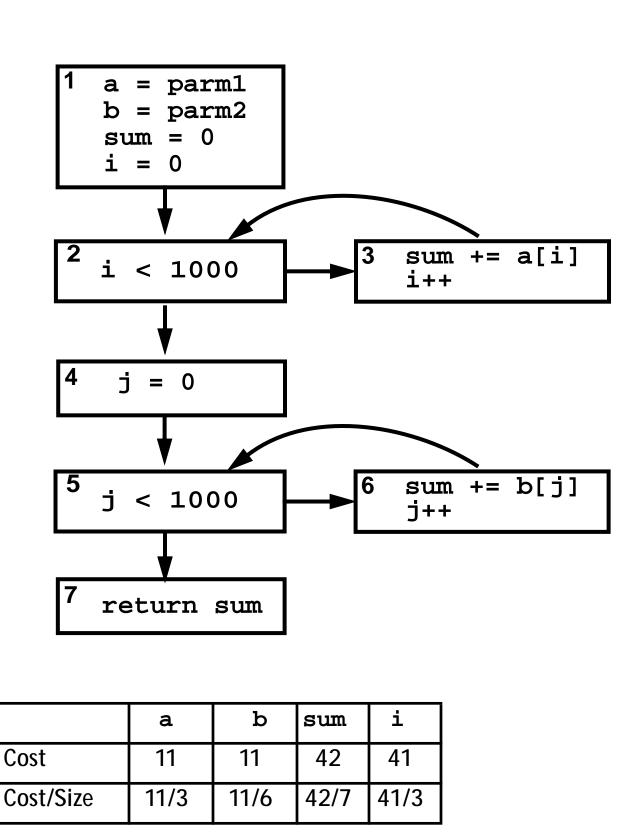

### Example

|                    | liml | lim2 | T1   | Т2   | i    | j    |

|--------------------|------|------|------|------|------|------|

| Cost               | 11   | 11   | 11   | 11   | 42   | 42   |

| Cost/<br>Neighbors | 11/3 | 11/5 | 11/3 | 11/3 | 42/5 | 42/3 |

#### Do a 3 coloring

Since no node has fewer than 3 neighbors, we remove a node based on the minimum Cost/Neighbors value.

lim2 is chosen.

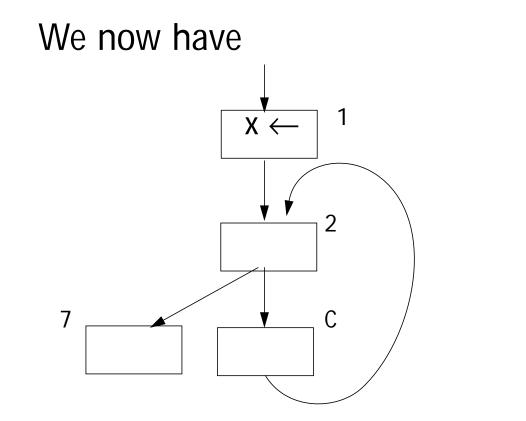

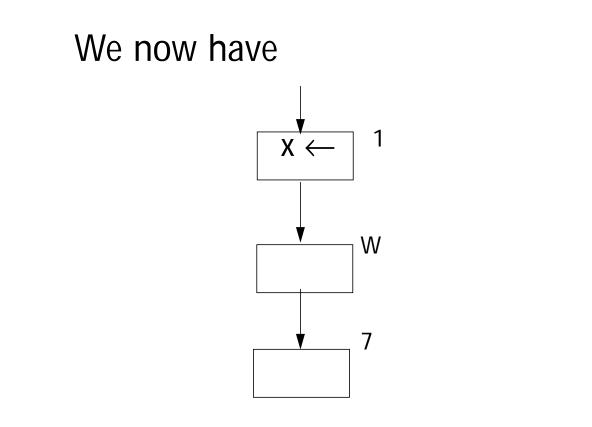

We now have:

Remove (say) 1im1, then т1, т2, j and i (order is arbitrary).

Assuming the colors we have are R1, R2 and R3, the register assignment we choose is

i:R1, j:R2, т2:R3, т1:R2, lim1:R3, lim2:spill

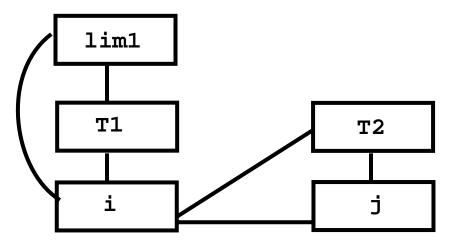

# **Color Preferences**

Sometimes we wish to assign a particular register (color) to a selected Live Range (e.g., a parameter or return value) *if possible*.

We can mark a node in the Interference Graph with a *Color Preference*.

When we unstack nodes and assign colors, we will avoid choosing color c if an uncolored neighbor has indicted a preference for it. If only color c is left, we take it (and ignore the preference).

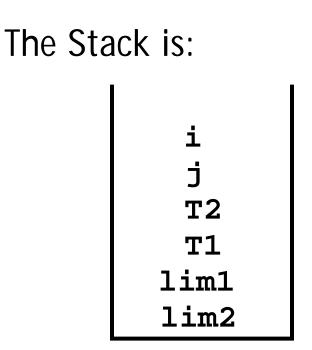

# Example

Assume in our previous example that lim1 has requested register R1 and lim2 has requested register R2 (because these are the registers the parameters are passed in).

| i         |  |

|-----------|--|

| j         |  |

| Т2        |  |

| <b>T1</b> |  |

| lim1      |  |

| lim2      |  |

Now when i, j and T1 are unstacked, they respect lim1's and lim2's preferences:

i:R3, j:R1, т2:R2, т1:R2, lim1:R1, lim2:spill

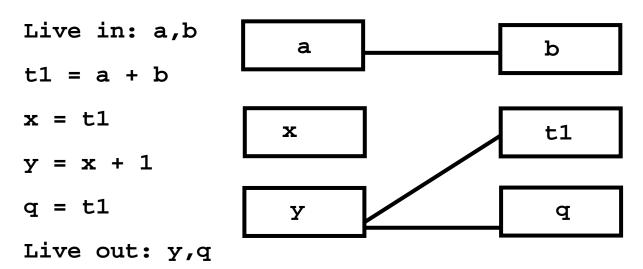

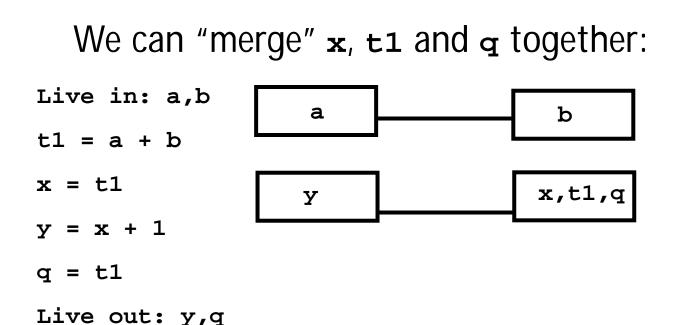

### Using Coloring to Optimize Register Moves

A nice "fringe benefit" of allocating registers via coloring is that we can often *optimize away* register to register moves by giving the source and target the *same color*.

Consider

We'd like **x**, **t1** and **q** to get the same color. How do we "force" this?

Now a 2-coloring that optimizes away both register to register moves is trivial.

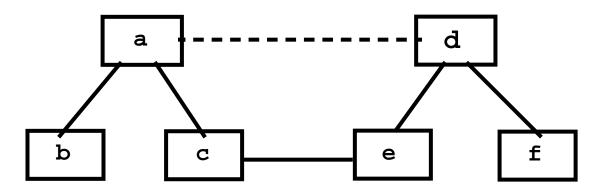

# **Reckless Coalescing**

Originally, Chaitin suggested merging *all* move-related nodes that don't interfere.

This is *reckless*—the merged node may not be colorable!

(Is it worth a spill to save a move??)

This Graph is 2-colorable before the reckless merge, but *not* after.

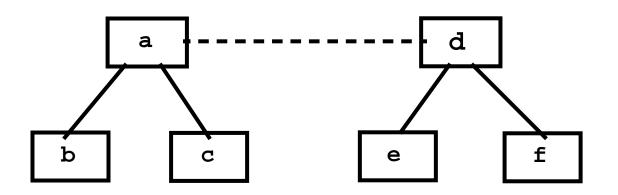

# **Conservative Coalescing**

In response to Chaitin's reckless coalescing approach, Briggs suggested a *more conservative* approach.

See "Improvement to Graph Coloring Register Allocation," P. Briggs et. al., ACM Toplas, May 1994. Briggs suggested that two moverelated nodes should be merged *only if* the combined source and target node has fewer than R neighbors.

This *guarantees* that the combined node will be colorable, but may miss some optimization opportunities.

After a merge of nodes a and a, there will be four neighbors, but a 2-coloring is still possible.

# **Iterated Coalescing**

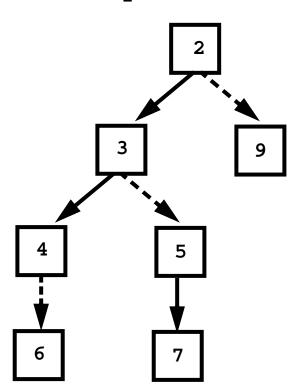

This is an intermediate approach, that seeks to be safer than reckless coalescing and more effective than conservative coalescing. It was proposed by George and Appel. 1. Build:

Create an Interference Graph, as usual. Mark source-target pairs with a special move-related arc (denoted as a dashed line).

2. Simplify:

Remove and stack non-move-related nodes with < R neighbors.

3. Coalesce:

Combine move-related pairs that will have < R neighbors after coalescing.

Repeat steps 2 and 3 until only nodes with R or more neighbors or moverelated nodes remain or the graph is empty. 4. Freeze:

If the Interference Graph is non-empty: Then If there exists a move-related node with < R neighbors Then: "Freeze in" the move and make the node non-move-related. Return to Steps 2 and 3. Else: Use Chaitin's Cost/Neighbors criterion to remove and stack a node. Return to Steps 2 and 3.

5. Unstack:

Color nodes as they are unstacked as per Chaitin and Briggs.

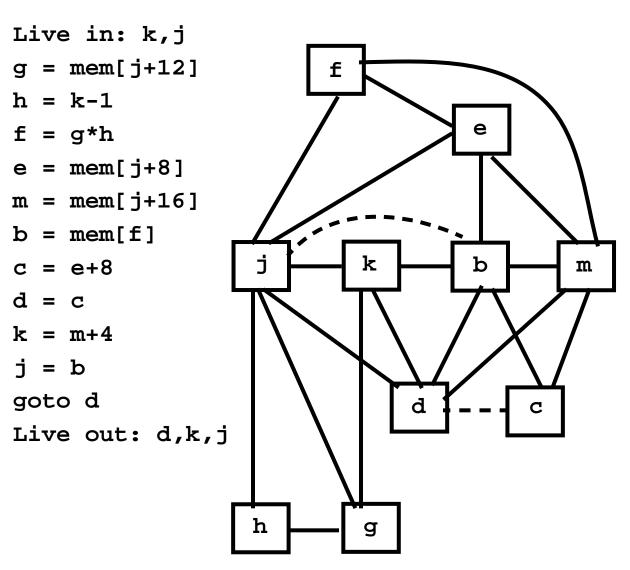

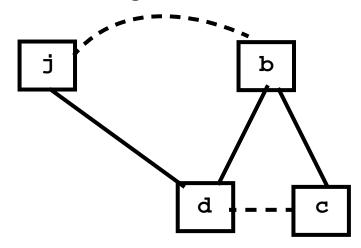

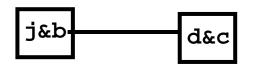

#### Example

Assume we want a 4-coloring.

Note that neither јър nor аъс can be conservatively colored.

We simplify by removing nodes with fewer than 4 neighbors.

We remove and stack: g, h, k, f, e, m

The remaining Interference Graph is

We can now conservatively coalesce the move-related pairs to obtain

These remaining nodes can now be removed and stacked.

| d&c<br>j&b |  |

|------------|--|

| m          |  |

| е          |  |

| f          |  |

| k          |  |

| g          |  |

| h          |  |

We can now unstack and color: d&c:R1, j&b:R2, m:R3, e:R4, f:R1, k:R3, h:R1, g:R4

No spills were required and both moves were optimized away.

# **Reading Assignment**

Read David Wall's paper, "Global Register Allocation at Link Time."

### Priority-Based Register Allocation

Alternatives to Chaitin-style register allocation are presented in:

- Hennessy and Chow, "The prioritybased coloring approach to register allocation," ACM TOPLAS, October 1990.

- Larus and Hilfinger, "Register allocation in the SPUR Lisp compiler," SIGPLAN symposium on Compiler Construction, 1986.

These papers suggest two innovations:

1. Use of a *Priority Value* to choose nodes to color in an Interference Graph.

A Priority measures

(Spill cost)/(Size of Live Range)

The idea is that small live ranges with a high spill cost are ideal candidates for register allocation.

As the size of a live range grows, it becomes less attractive for register allocation (since it "ties up" a register for a larger portion of a program).

#### 2. Live Range Splitting

Rather than spill an entire live range that can't be colored, the live range is split into two or more smaller live ranges that may be colorable.

# Large vs. Small Live Ranges

A large live range has less spill code.

Values are directly read from and written to a register.

*But*, a large live range is harder to allocate, since it may conflict with many other register candidates.

A small live range is easier to allocate since it competes with fewer register candidates.

*But*, more spill code is needed to load and save register values across live ranges.

In the limit a live range can shrink to a single definition or use of a register.

*But*, then we really don't have an effective register allocation at all!

# Terminology

In an Interference Graph:

- A node with fewer neighbors than colors is termed *unconstrained*. It is trivial to color.

- A node that is not unconstrained is termed *constrained*. It may need to be split or spilled.

PriorityRegAlloc(proc, regCount) {

ig  $\leftarrow$  buildInterferenceGraph(proc) unconstrained  $\leftarrow$

{  $n \in nodes(ig)$  | neighborCount(n) < regCount } constrained  $\leftarrow$

$\{ n \in nodes(ig) \mid neighborCount(n) \ge regCount \}$

```

while(constrained \neq \phi) {

for (c \in constrained such that not colorable(c)

and canSplit(c) ) {

c1, c2 \leftarrow split(c)

constrained \leftarrow constrained - {c}

if (neighborCount(c1) < regCount)

unconstrained \leftarrow unconstrained U { c1}

else constrained \leftarrow constrained U {c1}

if ( neighborCount(c2) < regCount )

unconstrained \leftarrow unconstrained U { c2}

else constrained \leftarrow constrained U {c2}

for (d \in neighbors(c) such that

d \in unconstrained and

neighborCount(d) \geq regCount ){

unconstrained \leftarrow unconstrained - {d}

constrained \leftarrow constrained U {d}

}

} // End of both for loops

```

/\* At this point all nodes in constrained are colorable or can't be split \*/

```

Select p ∈ constrained such that

priority(p) is maximized

if ( colorable(p) )

color(p)

else spill(p)

} // End of While

color all nodes ∈ unconstrained

```

}

# How to Split a Constrained Node

- There are many possible partitions of a live range; too many to fully explore.

- Heuristics are used instead. One simple heuristic is:

- Remove the first basic block (or instruction) of the live range. Put it into a new live range, NR.

- Move successor blocks (or instructions) from the original live range into NR, as long as NR remains colorable.

- Single Basic Blocks (or instructions) that can't be colored are spilled.

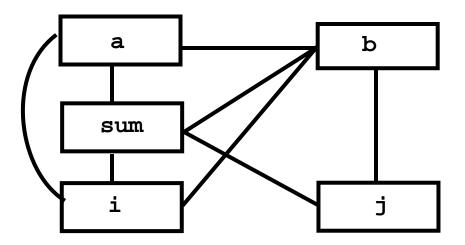

### Example

int sum(int a[], int b[]) {

int sum = 0;

for (int i=0; i<1000; i++)

sum += a[i];

for (int j=0; j<1000; j++)

sum += b[j];

return sum;

}</pre>

Assume we want a 3-coloring.

We first simplify the graph by removing unconstrained nodes (those with < 3 neighbors).

Node j is removed. We now have:

At this point, each node has 3 neighbors, so either spilling or splitting is necessary.

A spill really isn't attractive as each of the 4 register candidates is used within a loop, magnifying the costs of accessing memory.

# **Coloring by Priorities**

We'll color constrained nodes by priority values, with preference given to large priority values.

Variables i, sum and a are assigned colors R1, R2 and R3.

Variable ь can't be colored, so we will try to split it. ь's live range is blocks 1 to 6, with 1 as ь's entry point.

Blocks 1 to 3 can't be colored, so ь is spilled in block 1. However, blocks 4 to 6 form a split live range that can be colored (using кз).

We will reload ь into кз in block 4, and it will be register-allocated throughout the second loop. The added cost due to the split is minor a store in block 1 and a reload in block 4.

# **Choice of Spill Heuristics**

We have seen a number of heuristics used to choose the live ranges to be spilled (or colored).

These heuristics are typically chosen using one's intuition of what register candidates are most (or least) important. Then a heuristic is tested and "fine tuned" using a variety of test programs.

Recently, researchers have suggested using machine learning techniques to automatically determine effective heuristics.

In "Meta Optimization: Improving Compiler Heuristics with Machine Learning," Stephenson, Amarasinghe, et al, suggest using *genetic programming* techniques in which priority functions (like choice of spill candidates) are mutated and allowed to "evolve."

Although the approach seems rather random and unfocused, it can be effective. Priority functions *better than* those used in real compilers have been reported, with research still ongoing.

### Interprocedural Register Allocation

The goal of register allocation is to keep frequently used values in registers.

Ideally, we'd like to go to memory only to access values that may be aliased or pointed to.

For example, array elements and heap objects are routinely loaded from and stored to memory each time they are accessed. With alias analysis, optimizations like Scalarization are possible.

```

for (i=0; i<1000; i++)

for (j=0; j<1000; j++)

a[i] += i * b[j];</pre>

```

is optimized to

```

for (i=0; i<1000; i++){

int Ai = a[i];

for (j=0; j<1000; j++)

Ai += i * b[j];

a[i] = Ai;

}</pre>

```

# Attacking Call Overhead

- Even with good global register allocation calls are still a problem.

- In general, the caller and callee may use the same registers, requiring saves and restores across calls.

- Register windows help, but they are inflexible, forcing all subprograms to use the same number of registers.

- We'd prefer a register allocator that is sensitive to the calling structure of a program.

# **Reading Assignment**

- Read "Minimum Cost Interprocedural Register Allocation," by S. Kurlander et al. (linked from class Web page).

- Get Handout #4 from Dolt.

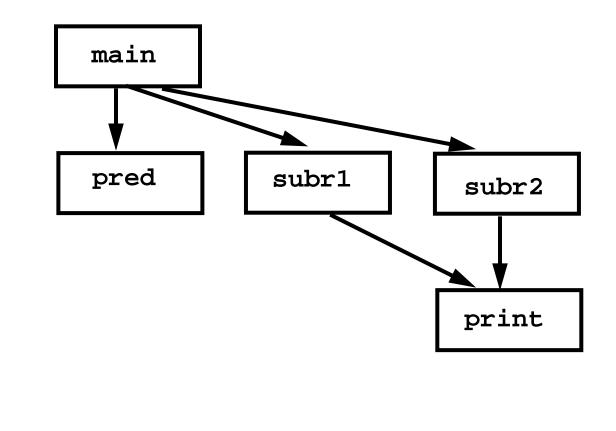

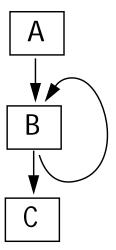

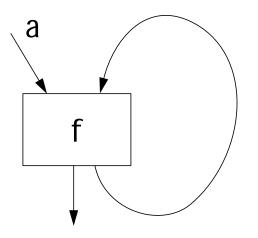

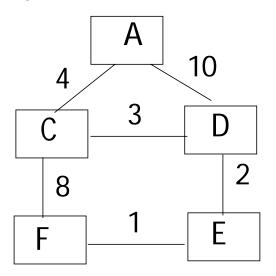

# Call Graphs

A *Call Graph* represents the calling structure of a program.

- Nodes are subprograms (procedures and functions).

- Arcs represent calls between subprograms. An arc from A to B denotes that a call to B appears within A.

- For an indirect call (a function parameter or a function pointer) an arc is added to all potential callees.

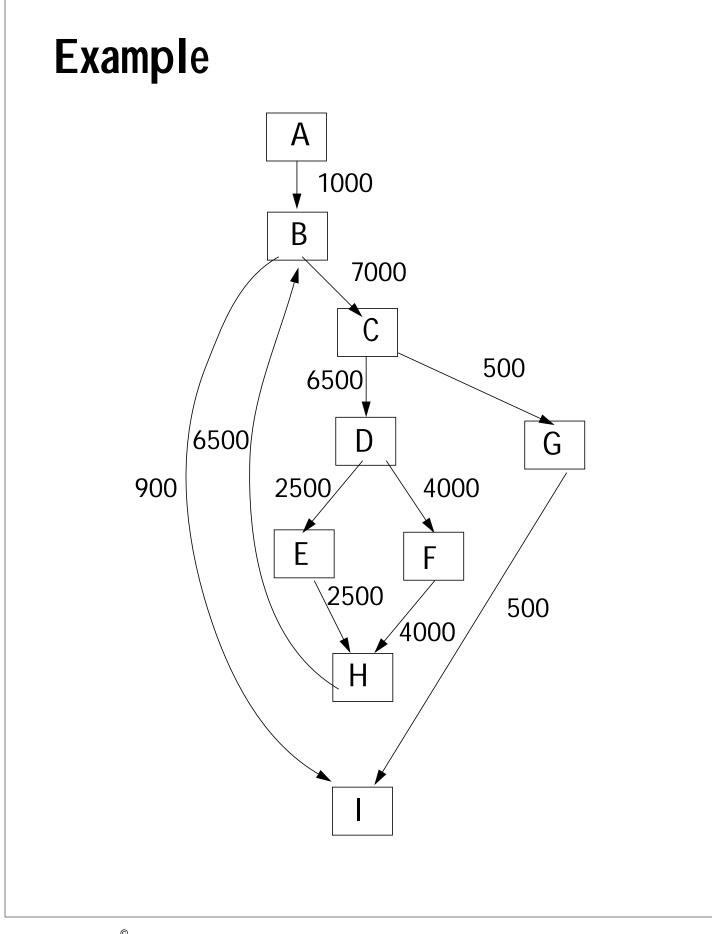

#### Example

```

main() {

if (pred(a,b))

subr1(a)

else subr2(b);}

bool pred(int a, int b){

return a==b; }

subr1(int a){ print(a);}

subr2(int x){ print(2*x);}

```

## Wall's Interprocedural Register Allocator

Operates in two phases:

- Register candidates are identified at the subprogram level.

Each candidate (a single variable or a set of non-interfering live ranges) is compiled as if it won't get a register.

At link-time unnecessary loads and stores are edited away *if* the candidate *is* allocated a register.

- 2. At link-time, when all subprograms are known and available, register candidates are allocated registers.

## Identifying Interprocedural Register Sharing

If two subprograms are not connected in the call graph, a register candidate in each can share the same register without any saving or restoring across calls.

A register candidate from pred, subr1 and subr2 can all share one register. At the interprocedural level we must answer 2 questions:

- 1. A local candidate of one subprogram can share a register with candidates of what other subprograms?

- 2. Which local register candidates will yield the greatest benefit if given a register?

Wall designed his allocator for a machine with 52 registers. This is enough to divide all the registers among the subprograms without any saves or restores at call sites.

With fewer registers, spills, saves and restores will often be needed (if registers are used aggressively within a subprogram).

# Restrictions on the Call Graph

Wall limited calls graphs to DAGs since cycles in a call graph imply recursion, which will force saves and restores (why?)

# **Cost Computations**

Each register candidate is given a per-call cost, based on the number of saves and restores that can be removed, scaled by  $10^{loop\_depth}$ .

This benefit is then multiplied by the *expected* number of calls, obtained by summing the total number of call sites, scaled by loop nesting depth.

## **Grouping Register Candidates**

We now have an estimate of the benefit of allocating a register to a candidate. Call this estimate cost(candidate)

We estimate potential interprocedural sharing of register candidates by assigning each candidate to a *Group*.

All candidates within a group can share a register. No two candidates in any subprogram are in the same group.

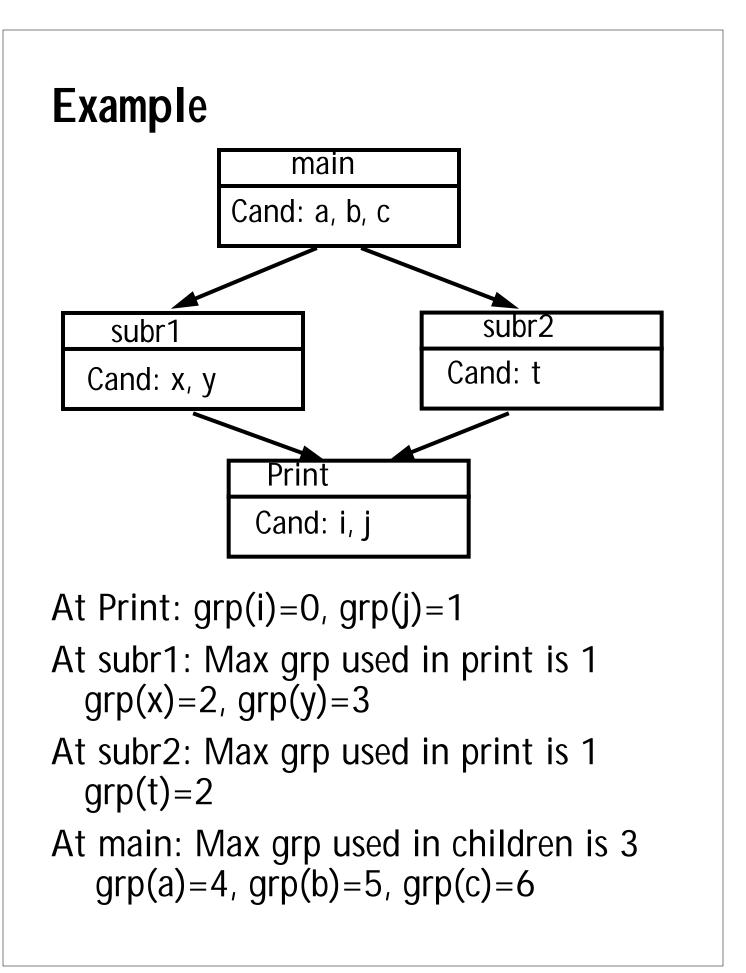

```

Groups are assigned during a reverse

depth-first traversal of the call graph.

AsgGroup(node n) {

if (n is a leaf node)

grp = 0

else { for (each c \in children(n)) {

AsgGroup(c) }

grp =

1+ Max (Max group used in c)

c \in children(n)

}

for (each r \in registerCandidates(n)){

assign r to grp

grp++ }

}

Global variables are assigned to a

singleton group.

```

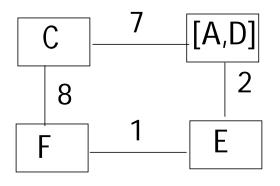

If A calls B (directly or indirectly), then none of A's register candidates are in the same group as any of B's register candidates.

This *guarantees* that A and B will use different registers.

Thus no saves or restores are needed across a call from A to B.

## Assigning Registers to Groups

$Cost(group) = \sum_{candidates} cost(candidates)$

We assign registers to groups based on the cost of each group, using an "auction."

for (r=0; r < RegisterCount; r++) {

Let G be the group with the

greatest cost that has not yet

been assigned a register.

Assign r to G</pre>

}

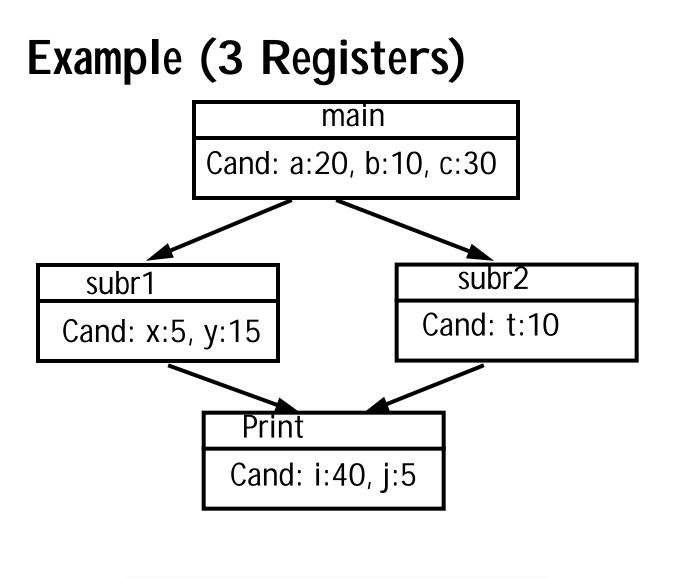

| Group | Members | Cost |

|-------|---------|------|

| 0     | i       | 40   |

| 1     | j       | 5    |

| 2     | x, t    | 15   |

| 3     | У       | 15   |

| 4     | а       | 20   |

| 5     | b       | 10   |

| 6     | С       | 30   |

The 3 registers are given to the groups with the highest weight,

i (40), c(30), a(20).

Is this optimal?

No! If y and t are grouped together, y and t (cost=25) get the last register.

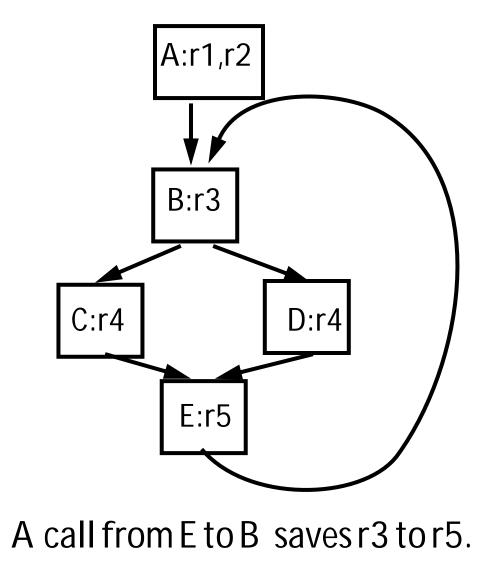

## Recursion

To handle recursion, any call to a subprogram "up" in the call graph must save and restore all registers possibly in use between the caller and callee.

#### Performance

Wall found interprocedural register allocation to be very effective (given 52 Registers!).

Speedups of 10-28% were reported. Even with only 8 registers, speedups of 5-20% were observed.

#### Optimal Interprocedural Register Allocation

Wall's approach to interprocedural register allocation isn't optimal because register candidates aren't grouped to achieve maximum benefit.

Moreover, the placement of save and restore code *if needed* isn't considered.

These limitations are addressed by Kurlander in "Minimum Cost Interprocedural Register Allocation."

#### Optimal Save-Free Interprocedural Register Allocation

- Allocation is done on a cycle-free call graph.

- Each subprogram has one or more register candidates, c<sub>i</sub>.

- Each register candidate, c<sub>i</sub>, has a cost (or benefit), w<sub>i</sub>, that is the improvement in performance if c<sub>i</sub> is given a register. (This w<sub>i</sub> value is scaled to include nested loops and expected call frequencies.)

#### Interference Between Register Candidates

The notion of interference is extended to include interprocedural register candidates:

- Two Candidates in the same subprogram always interfere. (Local non-interfering variables and

- values have already been grouped into interprocedural register candidates.)

- If subprogram P calls subprogram Q (directly or indirectly) then register candidates within P always interfere with register candidates within Q.

The algorithm can group candidate p with either t or u (since they don't interfere). It can also group candidate q with either t or u.

If two registers are available, it must "discover" that assigning R1 to q&t, and R2 to m is optimal.

Non-interfering register candidates are grouped into registers so as to solve:

$$\begin{array}{l} \text{Maximize} \quad \sum_{k} W_{j} \\ \textbf{c}_{j} \in \bigcup_{i=1}^{k} \textbf{R}_{i} \end{array}$$

That is, we wish to group sets of noninterfering register candidates into k registers such that the overall benefit is maximized.

But how do we solve this?

Certainly examining all possible groupings will be prohibitively expensive!

Kurlander solved this problem by mapping it to a known problem in Integer Programming:

the Dual Network Flow Problem.

Solution techniques for this problem are well known—libraries of standard solution algorithms exist.

Moreover, this problem can be solved in *polynomial time*.

That is, it is "easier" than optimal global (intraprocedural) register allocation, which is NP-complete!

# **Reading Assignment**

- Read Section 15.4 (Code Scheduling) of Chapter 15.

- Read Gibbon's and Muchnick's paper, "Efficient Instruction Scheduling for a Pipelined Architecture."

- Read Kerns and Eggers' paper, "Balanced Scheduling: Instruction Scheduling When Memory Latency is Uncertain." (Linked from the class Web page.)

## Adding Saves & Restores

Wall designed his save-free interprocedural allocator for a machine with 52 registers.

Most computers have far fewer registers, and hence saving and restoring across calls, *when profitable*, should be allowed.

Kurlander's Technique can be extended to include save/restore costs. If the cost of saving and restoring is *less* than the benefit of allocating an extra register, saving is done. Moreover, saving is done where it is *cheapest* (not closest!).

## Example

```

main() { ... p(); ...}

p(){ ...

for (i=0; i<1000000; i++){

q():

}

}</pre>

```

We first allocate registers in a savefree mode. After all Registers have been allocated, q may need additional registers.

Most allocators would add save/ restore code at q's call site (or q's prologue and epilogue).

An optimal allocator will place save/ restore code at p's call site, freeing a register that p doesn't even want (but that q does want!)

## **Extending the Cost Model**

- As before, we group register candidates of different subprograms into registers.

- Now only candidates within the same subprogram automatically interfere.

- Saves are placed on the edges of the call graph.

- We aim to solve

where S<sub>m</sub> is the per/register save/ restore cost and Saved<sub>m</sub> is the number of registers saved on edge e<sub>m</sub>.

- As registers are saved, they may be reused in child subprograms.

- This optimization problem can be solved as a Network Dual Flow Problem.

- Again, the solution algorithm is *polynomial*.

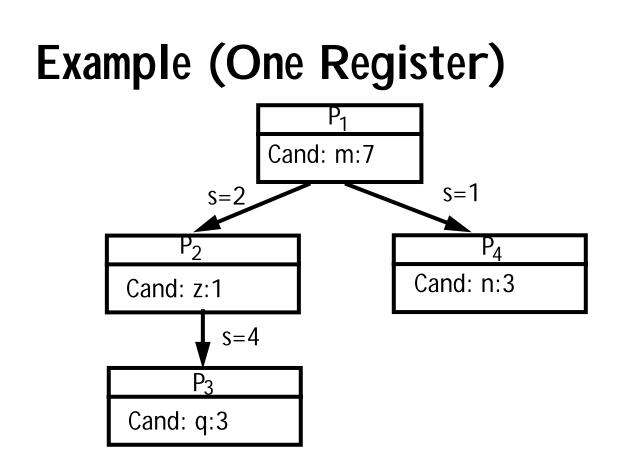

$P_1$  gets R1 save-free for m.

A save on  $P_1 \rightarrow P_4$  costs 1 and gives a register to n (net profit =2), so we do it.

A save on  $P_1 \rightarrow P_2$  for z costs 2, and yields 1, which isn't profitable.

A save on  $P_2 \rightarrow P_3$  for q costs 4, and yields 3, which isn't profitable.

A save on  $P_1 \rightarrow P_2$  for q costs 2, and yields 3, which *is* a net gain.

# Handling Global Variables

- Wall's technique handled globals by assuming they interfere with all subprograms and all other globals.

- Kurlander's approach is incremental (and non-optimal):

First, an optimal allocation for r registers is computed.

Next, one register is "stolen" and assigned interprocedurally to the most beneficial global.

(Subprograms that don't use the global can save and restore it locally, allowing local reuse).

An optimal allocation using R-1 registers is computed. If this solution plus the shared global is more profitable than the R register solution, the global allocation is "locked in."

Next, another register is "stolen" for a global, leaving R-2 for interprocedural allocation.

This process continues until stealing another register for a global isn't profitable.

#### Why is Optimal Interprocedural Register Allocation Easier than Optimal IntraProcedural Allocation?

This result seems counter-intuitive. How can allocating a whole program be *easier* (computationally) than allocating only one subprogram.

Two observations provide the answer:

- Interprocedural allocation assumes some form of local allocation has occurred (to identify register candidates).

- Interprocedural interference is *transitive* (if A interferes with B and B interferes with C then A interferes with B). But intraprocedural interference *isn't* transitive!

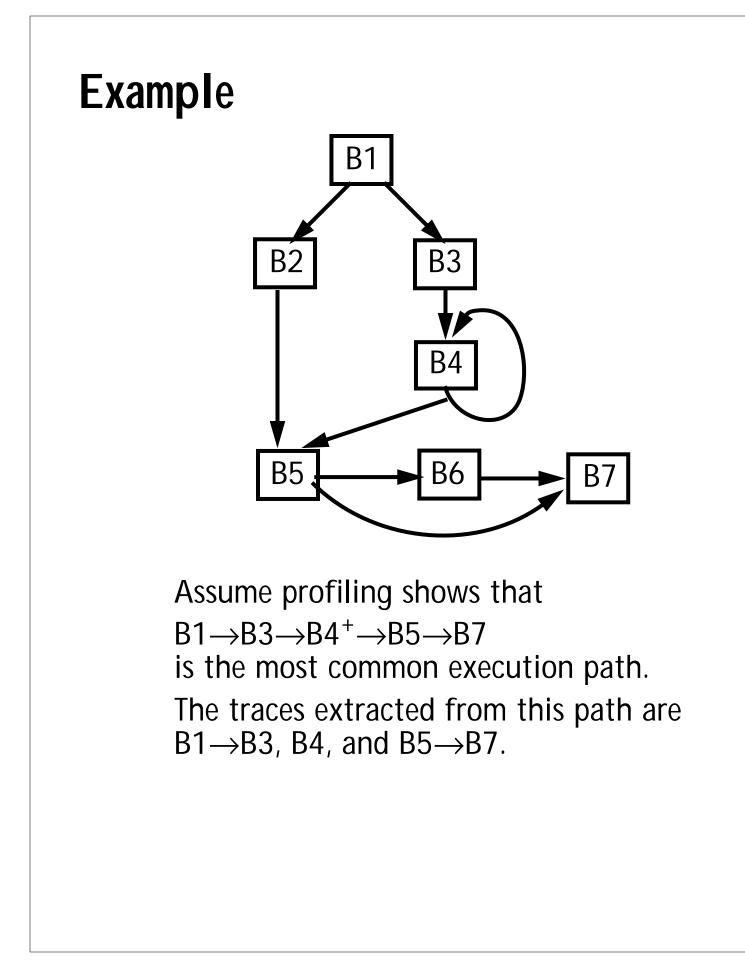

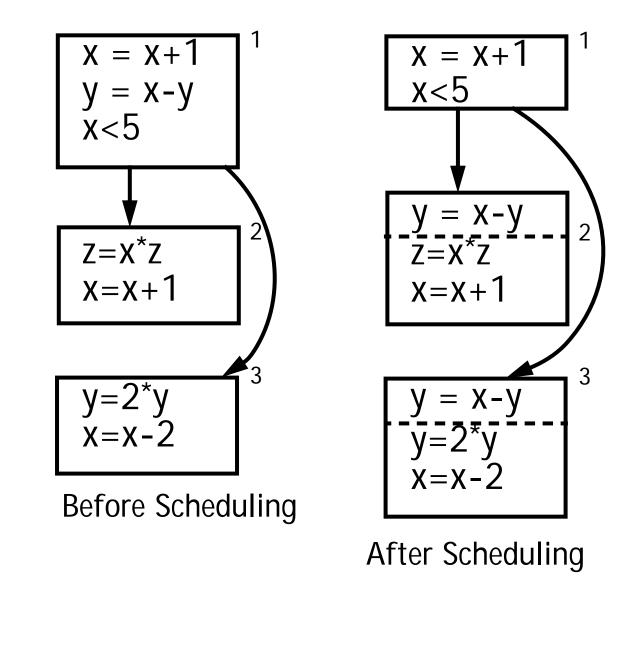

# Code Scheduling

Modern processors are pipelined.

They give the impression that all instructions take unit time by executing instructions in *stages* (steps), as if on an assembly line.

Certain instructions though (loads, floating point divides and square roots, delayed branches) take more than one cycle to execute.

These instructions may *stall* (halt the processor) or require a nop (null operation) to execute properly.

A *Code Scheduling* phase may be needed in a compiler to avoid stalls or eliminate nops.

## Scheduling Expression DAGs

After generating code for a DAG or basic block, we may wish to schedule (reorder) instructions to reduce or eliminate stalls.

A *Postpass Scheduler* is run after code selection and register allocation.

Postpass schedulers are very general and flexible, since they can be used with code generated by any compiler with any degree of optimization

*But*, since they can't modify register allocations, they can't always avoid stalls.

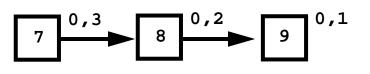

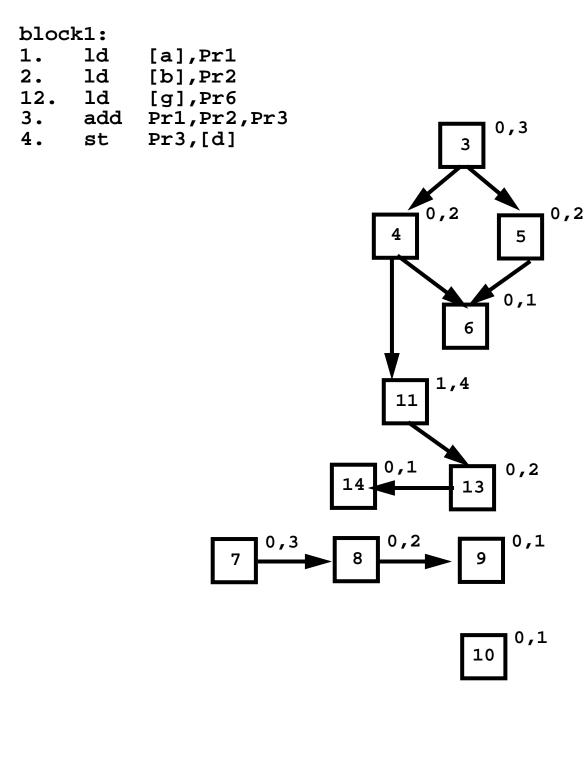

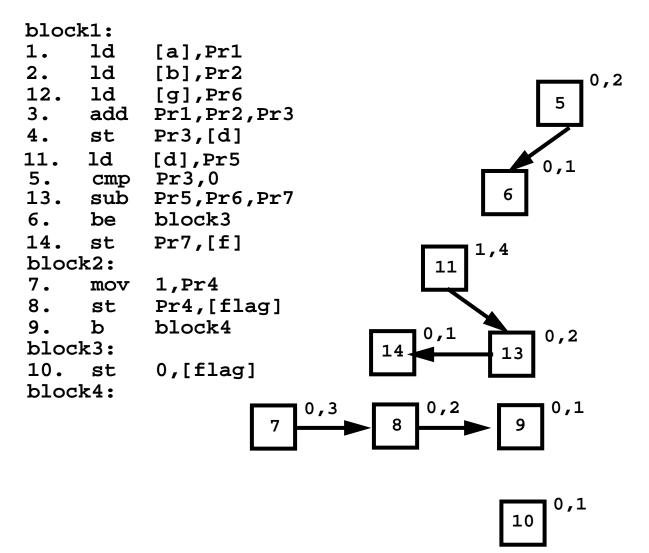

## **Dependency DAGs**

Obviously, not all reorderings of generated instructions are acceptable.

Computation of a register value must precede all uses of that value. A store of a value must precede all loads that might read that value.

A *Dependency Dag* reflects essential ordering constraints among instructions:

- Nodes are Instructions to be scheduled.

- An arc from Instruction i to Instruction j indicates that i must be executed before j may be executed.

# Kinds of Dependencies

We can identify several kinds of dependencies:

• True Dependence:

An operation that uses a value has a true dependence (also called a flow dependence) upon an earlier operation that computes the value. For example:

| mov | 1, % | 12 |     |

|-----|------|----|-----|

| add | %12, | 1, | %12 |

• Anti Dependence:

An operation that writes a value has a anti dependence upon an earlier operation that reads the value. For example:

```

add %12, 1, %10

mov 1, %12

```

• Output Dependence:

An operation that writes a value has a output dependence upon an earlier operation that writes the value. For example:

mov 1, %12 mov 2, %12

Collectively, true, anti and output dependencies are called data dependencies. Data dependencies constrain the order in which instructions may be executed.

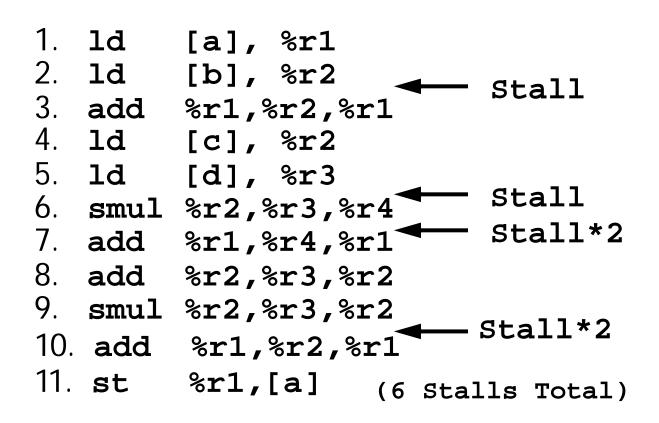

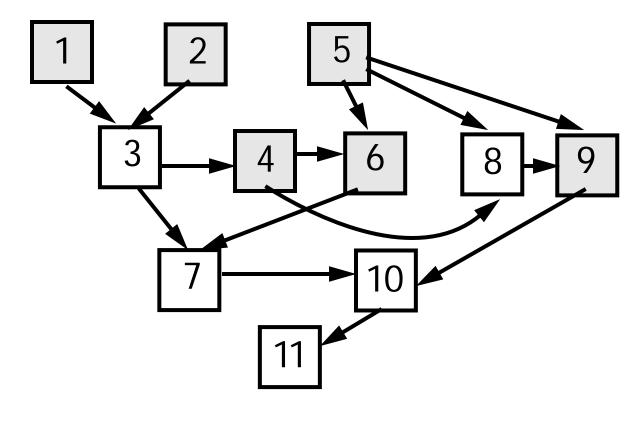

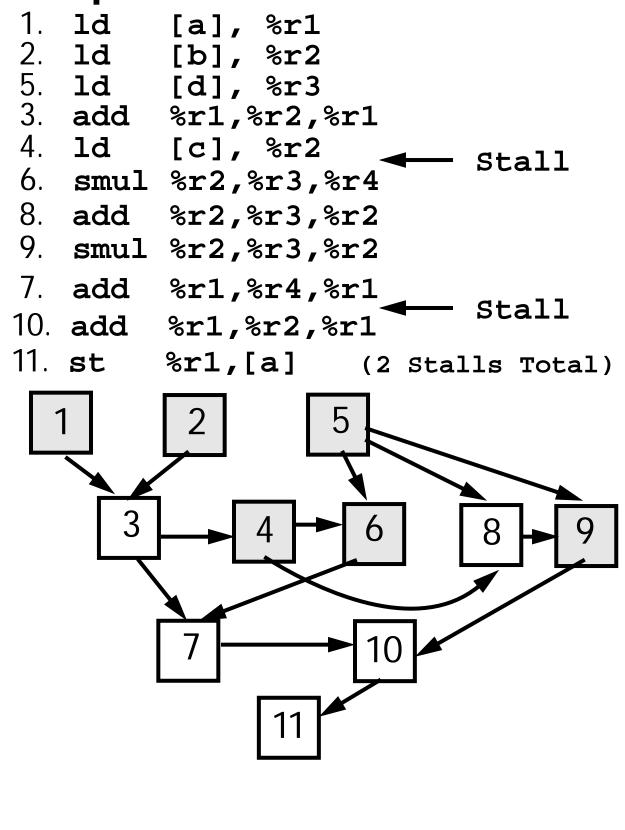

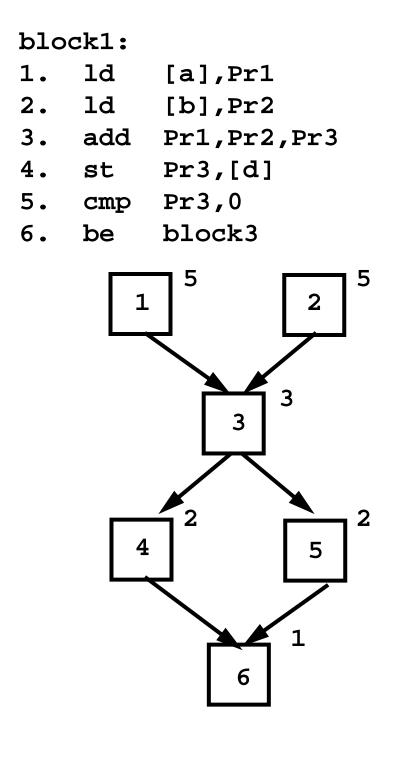

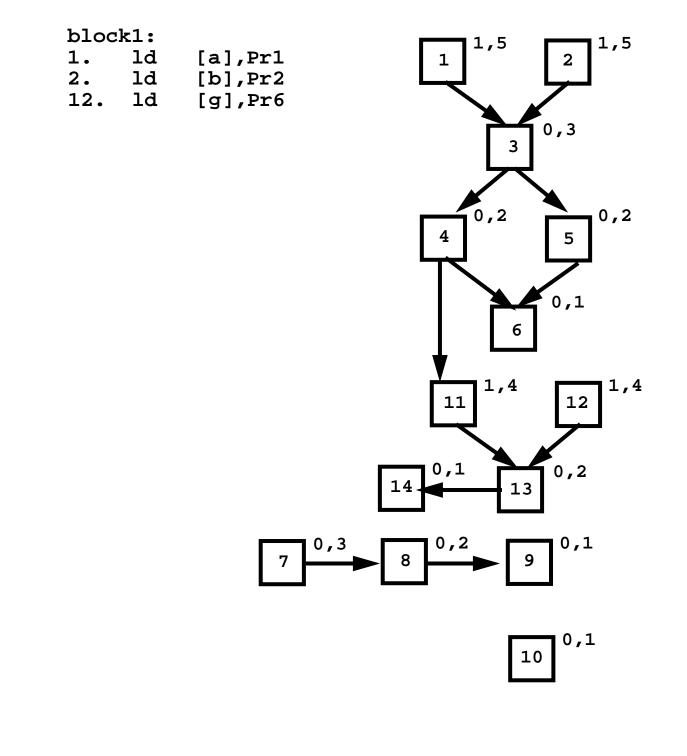

## Example

Consider the code that might be generated for

a = ((a+b) + (c\*d)) + ((c+d) \* d);

We'll assume 4 registers, the minimum possible, and we'll reuse already loaded values.

Assume a 1 cycle stall between a load and use of the loaded value and a 2 cycle stall between a multiplication and first use of the product.

#### Scheduling Requires Topological Traversal

Any valid code schedule is a *Topological Sort* of the dependency dag.

To create a code schedule you

- (1) Pick any root of the Dag.

- (2) Remove it from the Dag and schedule it.

- (3) Iterate!

Choosing a *Minimum Delay* schedule is NP-Complete:

"Computers and Intractability," M. Garey and D. Johnson, W.H. Freeman, 1979.

#### Dynamically Scheduled (Out of Order) Processors

To avoid stalls, some processors can execute instructions *Out of Program Order*.

If an instruction can't execute because a previous instruction it depends upon hasn't completed yet, the instruction can be "held" and a successor instruction executed instead.

When needed predecessors have completed, the held instruction is released for execution.

#### Example

# Limitations of Dynamic Scheduling

- 1. Extra processor complexity.

- 2. Register renaming (to avoid *False Dependencies*) may be needed.

- 3. Identifying instructions to be delayed takes time.

- 4. Instructions "late" in the program can't be started earlier.

# **Reading Assignment**

- Read Goodman and Hsu's paper, "Code Scheduling and Register Allocation in Large Basic Blocks."

- Read Bernstein and Rodeh's paper, "Global Instruction Scheduling for Superscalar Machines." (Linked from the class Web page.)

#### Gibbons & Muchnick Postpass Code Scheduler

- 1. If there is only one root, schedule it.

- 2. If there is more than one root, choose that root that won't be stalled by instructions already scheduled.

- If more than one root can be scheduled without stalling, consider the following rules (in order);

- (a) Does this root stall any of its successors?

(If so, schedule it immediately.)

- (b) How many new roots are exposed if this node is scheduled? (More is better.)

(c) Which root has the longest weighted path to a leaf (using instruction delays as the weight). (The "critical path" in the DAG gets priority.)

#### Example

#### **False Dependencies**

We still have delays in the schedule that was produced because of "false dependencies."

Both ъ and с are loaded into %r2. This limits the ability to move the load of с prior to any use of %r2 that uses ъ.

To improve our schedule we can use a processor that renames registers *or* allocate additional registers to remove false dependencies.

## **Register Renaming**

Many out of order processors automatically rename distinct uses of the same architectural register to distinct internal registers.

```

Thus

ld [a],%r1

ld [b],%r2

add %r1,%r2,%r1

ld [c],%r2

is executed as if it were

```

```

ld [a],%r1

ld [b],%r2

add %r1,%r2,%r3

ld [c],%r4

Now the final load can be executed

prior to the add, eliminating a stall.

```

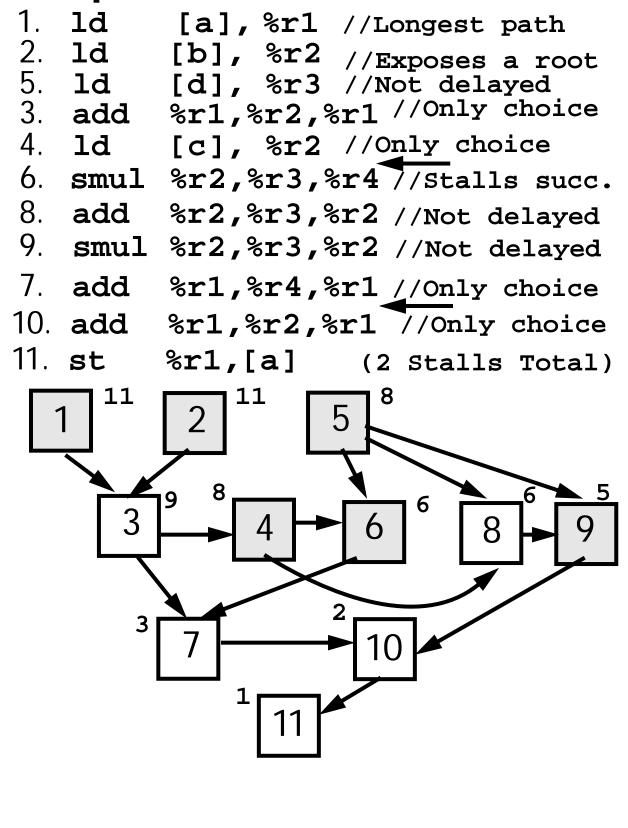

## **Compiler Renaming**

A compiler can also use the idea of renaming to avoid unnecessary stalls.

An extra register may be needed (as was the case for scheduling expression trees).

Also, a *round-robin* allocation policy is needed. Registers are reused in a *cyclic* fashion, so that the most recently freed register is reused last, not first.

#### Example

#### After Scheduling:

4. ld [C],%r3 //Longest path 5. **1d** [d],%r4 //Exposes a root 1. ld [a],%r1 //Stalls succ. 2. ld [b], %r2 //Exposes a root 6. smul %r3,%r4,%r5 //Stalls succ. 8. add %r3,%r4,%r3 //Longest path 9. smul %r3,%r4,%r3 //Stalls succ. 3. add %r1,%r2,%r1 //Only choice 7. add %r1,%r5,%r2 //Only choice 10. add %r2,%r3,%r2 //Only choice 11. st %r2,[a] (0 Stalls Total) 6 8 6 2 5 8 4 6 3 6 8 2 3 10 1

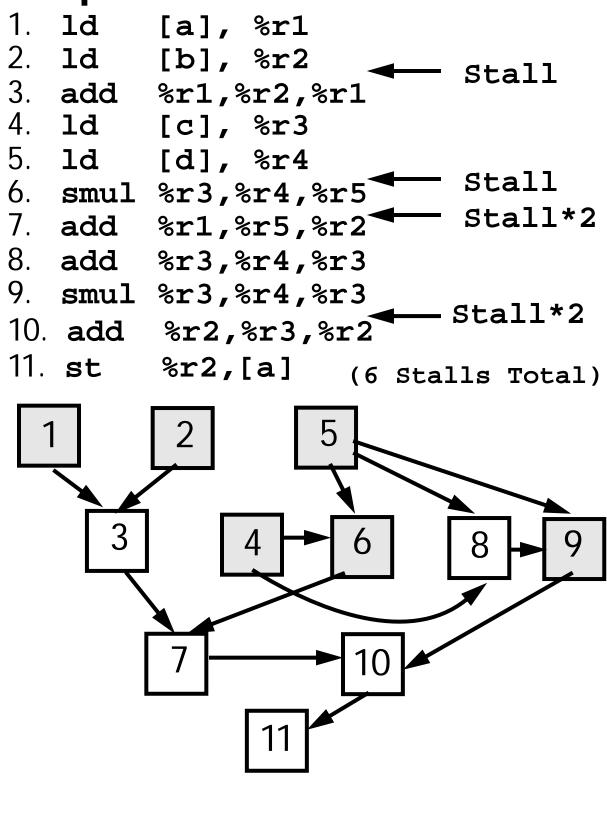

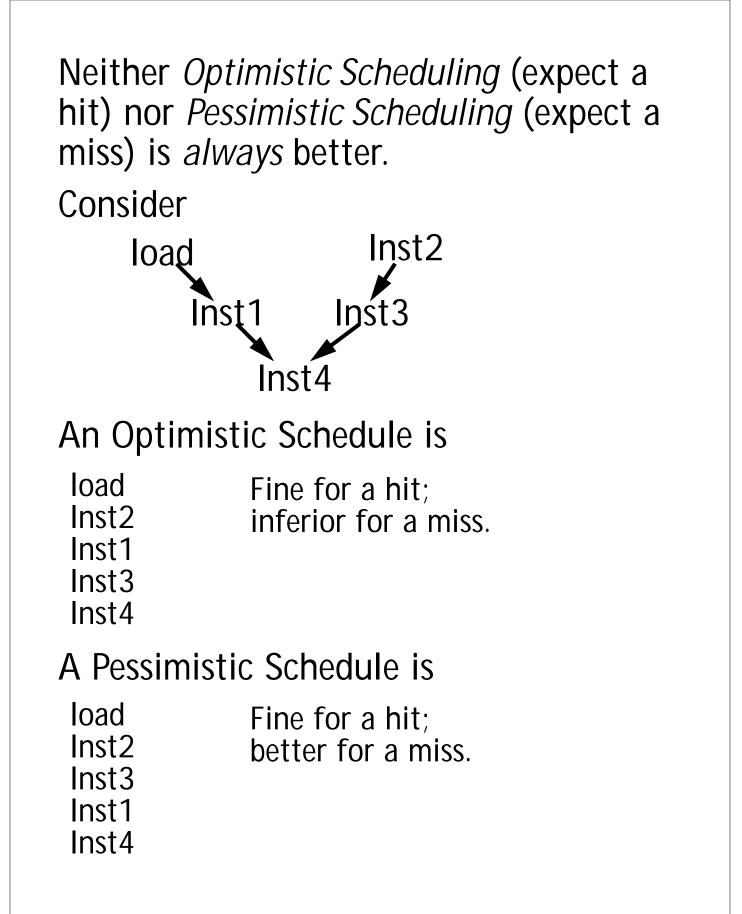

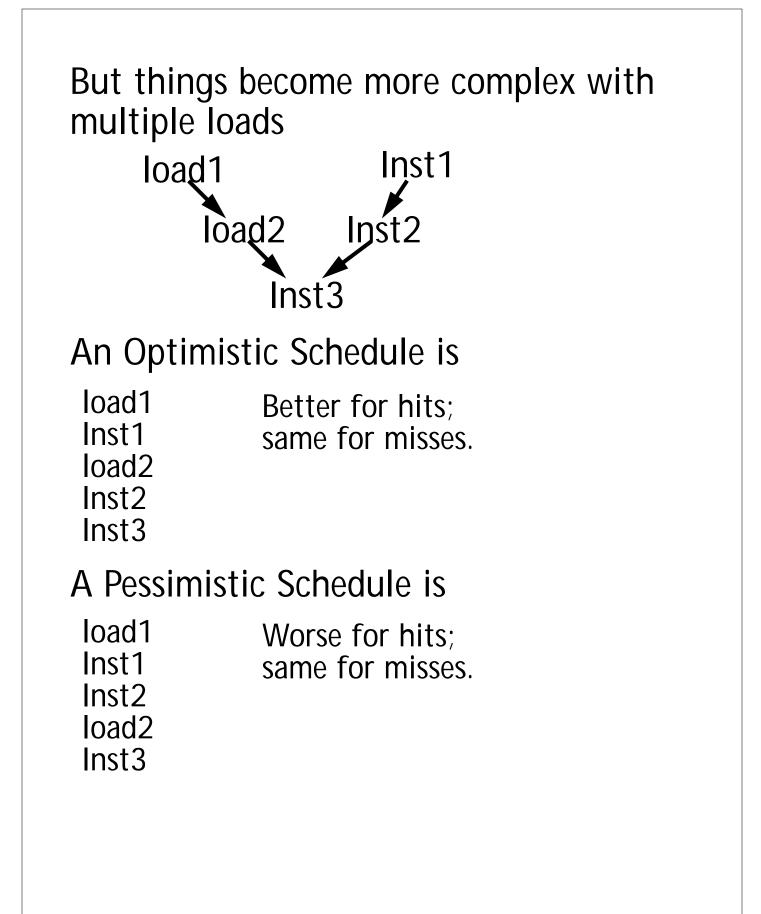

# **Balanced Scheduling**

When scheduling a load, we normally anticipate the *best* case, a hit in the primary cache.

On older architectures this makes sense, since we stall execution on a cache miss.

Many newer architectures are *non-blocking*. This means we can continue execution after a miss until the loaded value is used.

Assume a Cache miss takes N cycles (N is typically 10 or more).

Do we schedule a load anticipating a 1 cycle delay (a hit) or an N cycle delay (a miss)?

#### **Balance Placement of Loads**

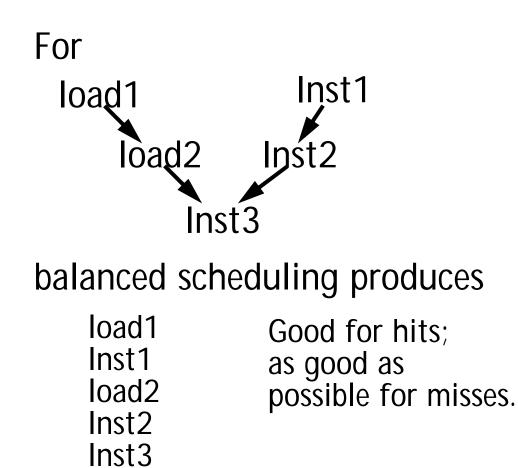

Eggers suggests a *balanced scheduler* that spaces out loads, using available independent instructions as "filler."

The insight is that scheduling should not be driven by worst-case latencies but rather by available *Independent* Instructions.

For

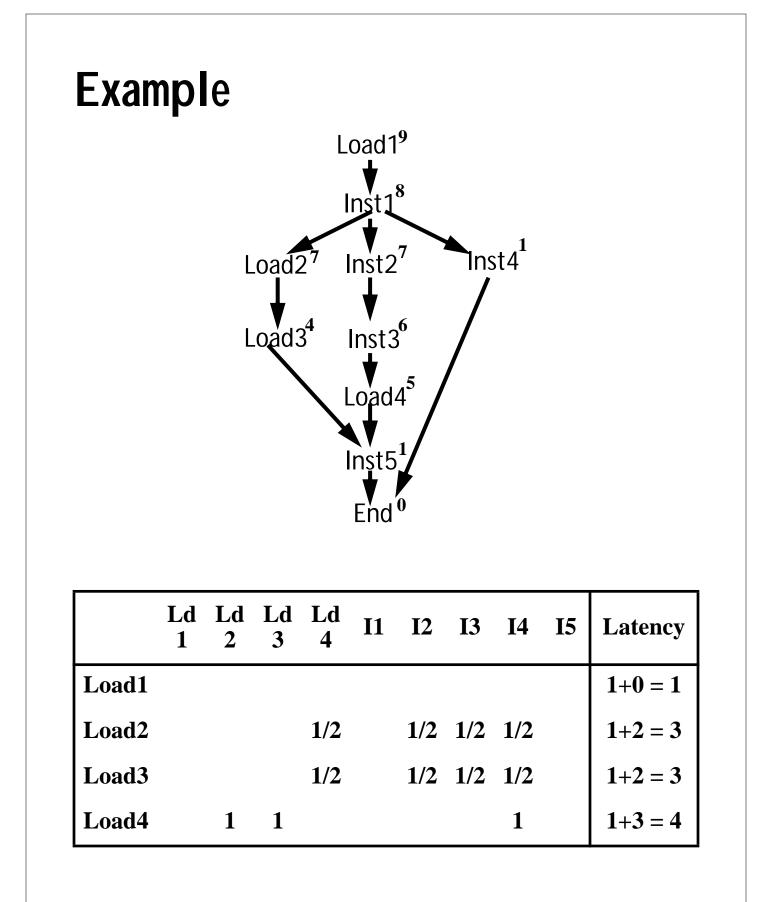

# Idea of the Algorithm

Look at each Instruction, i, in the Dependency DAG.

Determine which loads can run in parallel with i and use all (or part) of i's execution time to cover the latency of these loads. Compute available latency of each load:

Give each load instruction an initial latency of 1.

For (each instruction i in the Dependency DAG) do:

# Consider Instructions Independent of i:

$G_{ind} = DepDAG -$

(AllPred(i) U AllSucc(i) U {i})

For (each connected subgraph c in G<sub>ind</sub>) do:

Find m = maximum number of load instructions on any path in c.

For (each load d in c) do: add 1/m to d's latency.

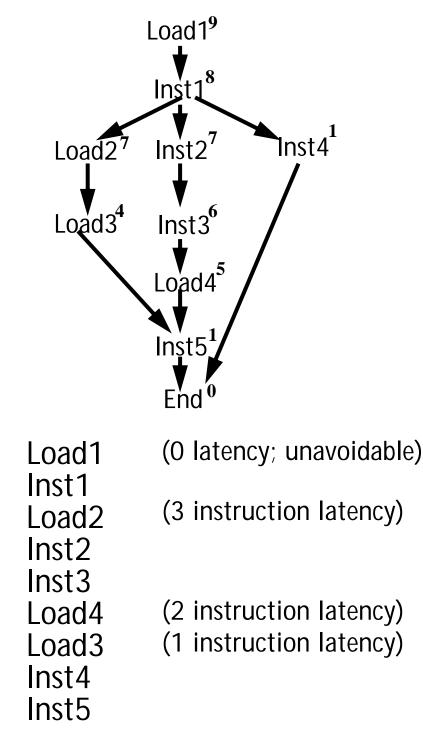

# Computing the Schedule Using Adjusted Latencies

Once latencies are assigned to each load (other instructions have a latency of 1), we annotate each instruction in the Dependency DAG with its critical path weight: the maximum latency (along any path) from the instruction to a Leaf of the DAG.

Instructions are scheduled using critical path values; the root with the highest critical path value is always scheduled next. In cases of ties (same critical path value), operations with the longest latency are scheduled first.

# Using the annotated Dependency Dag, instructions can be scheduled:

#### Goodman/Hsu Integrated Code Scheduler

Prepass Schedulers:

Schedule code prior to register allocation.

Can overuse registers—Always using a "fresh" register maximizes freedom to rearrange Instructions.

Postpass Schedulers:

Schedule code after register allocation.

Can be limited by "false dependencies" induced by register reuse.

Example is Gibbons/Muchnick heuristic.

## **Integrated Schedulers**

Capture best of both approaches.

When registers are plentiful, use additional registers to avoid stalls.Goodman & Hsu call this *CSP*: Code Scheduling for Pipelines.

When registers are scarce, switch to a policy that frees registers. Goodman & Hsu call this *CSR*:

Code Scheduling to free Registers.

Assume code is generated in single assignment form, with a unique pseudo-register for each computed value.

We schedule from a DAG where nodes are operations (to be mapped to instructions), and arcs represent data dependencies.

Each node will have an associated Cost, that measures the execution and stall time of the instruction that the node represents.

Nodes are labeled with a critical path cost, used to select the "most critical" instructions to schedule.

#### Definitions

Leader Set:

Set of DAG nodes ready to be scheduled, possibly with an interlock.

Ready Set:

Subset of Leader Set; Nodes ready to be scheduled without an interlock.

AvailReg:

A count of currently unused registers.

MinThreshold:

Threshold at which heuristic will switch from avoiding interlocks to reducing registers in use.

#### Goodman/Hsu Heuristic:

```

while (DAG \neq \phi) {

if (AvailReg > MinThreshold)

if (ReadySet \neq \phi)

Select Ready node with Max cost

else Select Leader node with Max cost

else // Reduce Registers in Use

if (\exists node \in ReadySet that frees registers) {

Select node that frees most registers

If (selected node isn't unique)

Select node with Max cost }

elsif (\exists node \in LeaderSet that frees regs){

Select node that frees most registers

If (selected node isn't unique)

Select node with fewest interlocks}

else find a partially evaluated path and

select a leader from this path

else Select any node in ReadySet

else Select any node in LeaderSet

Schedule Selected node

Update AvailReg count }//end while

```

## Example

We'll again consider

a = ((a+b) + (c\*d)) + ((c+d) \* d); Again, assume a 1 cycle stall between a load and use of its value and a 2 cycle stall between a multiplication and first use of the product.

We'll try 4 registers (the minimum), then 5 registers.

Should MinThreshold be 0 or 1?

At MinThreshold = 1, we always have a register to hold a result, but we may force a register to be spilled too soon!

At MinThreshold = 0, we may be forced to spill a register to free a result register.

But, we'll also be able to schedule more aggressively.

Is a spill or stall worse?

Note that we may be able to "hide" a spill in a delay slot!

We'll be aggressive and use MinThreshold = 0.

#### 4 Registers Used (1 Stall)

| Instru | iction       | Comment              | Regs<br>Used |

|--------|--------------|----------------------|--------------|

| ld     | [c], %r1     | Choose ready, cost=8 | 1            |

| ld     | [d], %r2     | Choose ready, cost=8 | 2            |

| ld     | [a], %r3     | Choose ready, cost=6 | 3            |

| smul   | %r1,%r2,%r4  | Choose ready, cost=6 | 4            |

| add    | %r1,%r2,%r1  | Free a register      | 4            |

| smul   | %r1,%r2,%r1  | Free a register      | 3            |

| ld     | [b], %r2     | Choose ready, cost=6 | 4            |

| add    | %r3,%r2,%r3← | Choose a leader      | 3            |

| add    | %r3,%r4,%r3  | No choice            | 2            |

| add    | %r3,%r1,%r3  | No choice            | 1            |

| st     | %r3,[a]      | No choice            | 0            |

#### 5 Registers Used (No Stalls)