## CS/ECE 252: INTRODUCTION TO COMPUTER ENGINEERING COMPUTER SCIENCES DEPARTMENT UNIVERSITY OF WISCONSIN-MADISON

Prof. Mark D. Hill TAs Marc de Kruijf & Sanghamitra Roy

> Midterm Examination 2 In Class (50 minutes) Wednesday, March 14, 2007 Weight: 15%

### CLOSED BOOK, NOTE, CALCULATOR, PHONE, & COMPUTER.

The exam in two-sided and has 9 pages, including two blank pages at the end.

Plan your time carefully, since some problems are longer than others.

NAME: \_\_\_\_\_

ID#\_\_\_\_\_

| Problem<br>Number | Maximum<br>Points | Actual<br>Points |

|-------------------|-------------------|------------------|

| 1                 | 3                 | MK               |

| 2                 | 4                 | MK               |

| 3                 | 4                 | МК               |

| 4                 | 3                 | MK               |

| 5                 | 4                 | МК               |

| 6                 | 4                 | SR               |

| 7                 | 4                 | SR               |

| 8                 | 4                 | SR               |

| Total             | 30                |                  |

### Problem 1 (3 points)

Write the Boolean expression corresponding to the following truth table. You need not simplify the expression.

| Α | В | С | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

# $\overline{A} \overline{B} \overline{C} + \overline{A} \overline{B} C + \overline{A} \overline{B} C$

#### Problem 2 (4 points)

Suppose a 32-bit instruction takes the following format:

| OPCODE SR | DR | IMM |

|-----------|----|-----|

|-----------|----|-----|

If there are 75 opcodes and 32 registers:

a) What is the minimum number of bits required to represent the OPCODE?

$\lceil \log_2 75 \rceil = 7$

b) What are the minimum number of bits required to represent SR and DR?

$\lceil \log_2 32 \rceil = 5$

c) What is the range of values that can be represented by the immediate (IMM)? Assume IMM is a 2's complement value.

$32 - 7 - 2 \times 5 = 15 \rightarrow 2^{15}$  values  $\rightarrow$  range:  $-2^{14}$  to  $2^{14} - 1$

# Problem 3 (4 points)

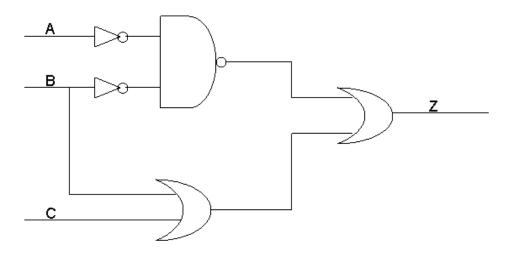

The figure below shows a combinational logic circuit. Complete the truth table corresponding to this circuit. What 3-input gate is equivalent to this logic circuit?

| Α | В | С | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Equivalent 3-input gate is: 3-input OR gate

## Problem 4 (3 points)

A load to a memory uses a 14-bit address A[13:0] to obtain a 12-bit value V[11:0]. What is the total number of bits that can be stored in the memory?

2<sup>14</sup> addresses, 12 bits per address → 2<sup>14</sup> x 12 bits of memory total

#### Problem 5 (4 points)

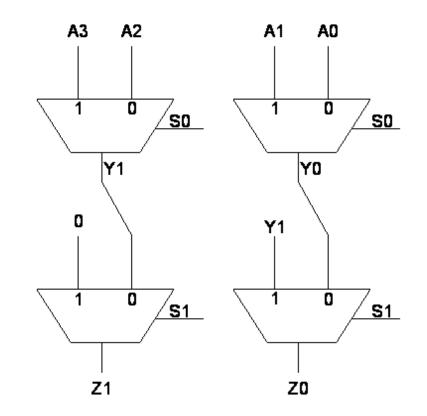

The figure below shows a combinational logic circuit with 4 2-to-1 multiplexers. If S0 = 1 and S1 = 0, what will be the values of Z0 and Z1? Express your answer in terms of A0, A1, A2 and A3. Note that two wires with the same name are assumed to be connected to each other.

Z1 = A3

# Problem 6 (4 points)

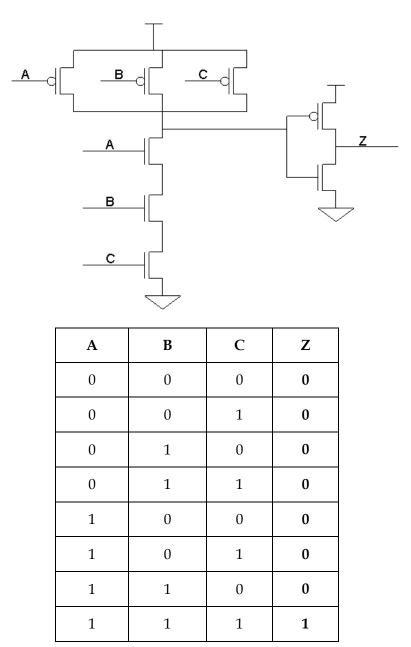

Fill in the truth table for the following transistor level circuit. Note that two wires with the same name are assumed to be connected to each other.

**Note:** This is the truth table for AND gate, if you did the truth table for a NAND gate overlooking the inverter, you received partial credit.

# **Problem 7 (4 points)**

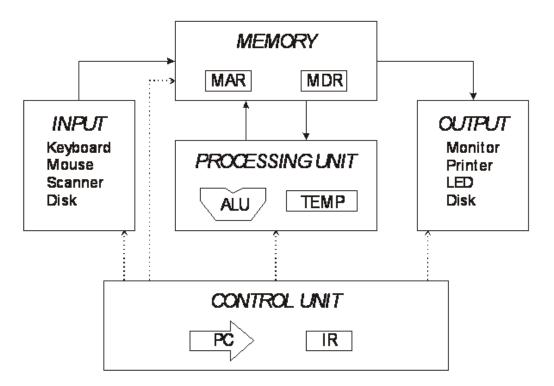

The figure below shows a block diagram of the Von Neumann model.

List the steps in the FETCH stage of instruction processing in the Von Neumann model. A hint has been provided for you:

## Transfer contents of PC to MAR

Send "read" signal to memory

Read contents of MDR, store in IR

**Increment PC**

#### Problem 8 (4 points)

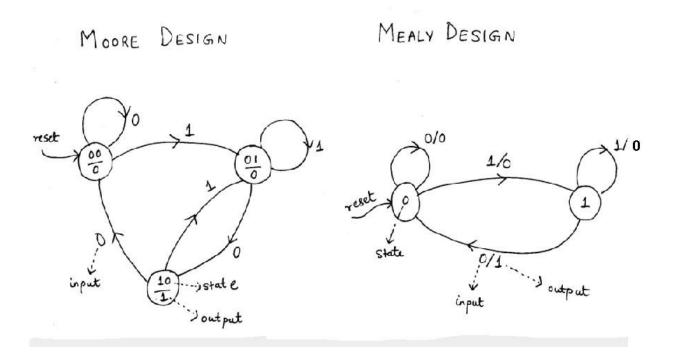

A pattern detector is a finite state machine that outputs "1" when a particular sequence is detected and outputs "0" otherwise.

a) Draw the finite state machine diagram for a pattern detector which detects the sequence '10'. The pattern detector takes a single bit (1 or 0) as input every clock cycle and outputs a 1 or 0 depending on whether or not the '10' sequence is seen in the input stream. Thus for an input stream '11000101' the output will be '00100010'

- b) How many flip-flops (storage elements) will be needed to implement this pattern detector?

- 2 Flip-flops will be needed for the Moore machine design having 3 states.

#### 1 Flip-flop will be needed for the Mealy machine design with 2 states.

Scratch Sheet 1 (in case you need additional space for some of your answers)

Scratch Sheet 2 (in case you need additional space for some of your answers)