KV the Konqueror

Vol. 3 No. 7

## Debating the Fuzzy Boundaries

## acm UCCU architecting tomorrow's computing

September 2005

# Make Way for Multiprocessors

Scaling with CMPs Performance at What Price? Multicore Programming

# JUNK MAIL. MISSING THE TRAIN. APPLICATION INTEGRATION. HAIR LOSS. BAD MUSIC. PAPER CUTS.

© 2005 Microsoft Corporation. All rights reserved. Microsoft, the Windows logo, Windows Server System, and "Your potential. Our passion." are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

#### Your potential. Our passion.<sup>™</sup> Microsoft<sup>®</sup>

#### WINDOWS SERVER SYSTEM WITH .NET MAKES APPLICATION INTEGRATION LESS PAINFUL.

.....

The list of potentially unpleasant things in your day is long. But now, the list just got a bit shorter. How? With the help of Windows Server System<sup>™</sup> and Microsoft<sup>®</sup>.NET.

The .NET Framework, an integral component of Windows Server System, is the development and execution environment that allows your different components and applications to work together seamlessly. That means applications are easier to build, manage, deploy, and integrate. The .NET Framework uses industry standards such as XML and Web Services which allow enterprise applications to be connected to infrastructure of any kind. In addition, the productivity enhancing features of .NET, such as automatic mapping of data to and from XML, also help to simplify integration by reducing the amount of code required to get it all done.

Find out more about application integration with Windows Server System and .NET: Simply get the Connected Systems Resource Kit at microsoft.com/connectedsystems

WHEN THINGS GET UNPLEASANT, JUST RELAX AND THINK OF EASIER APPLICATION INTEGRATION.

SEPTEMBER 2005

## MULTIPROCESSORS

#### **The Future of Microprocessors** 26

Kunle Olukotun and Lance Hammond, Stanford University The transition to chip multiprocessors is inevitable. Are you prepared to leverage their power?

**Extreme Software Scaling** 36 Richard McDougall, Sun Microsystems Scaling with multiprocessors is no longer just for boutique, high-end servers.

Software and the Concurrency Revolution 54 Herb Sutter and James Larus, Microsoft Multicore hardware architectures are blazing into the future. What's the next step for the software community?

The Price of Performance 48 Luiz André Barroso, Google The question is not, "Can you afford to switch to multicore CPUs?" but rather, "Can you afford not to?"

## Innovations by InterSystems

Rapid development with robust objects

Easy database administration

Lightning speed with a multidimensional engine

Massive scalability on minimal hardware

## **Database With Multidimensional Appeal.**

Caché is the first multidimensional database for transaction processing and real-time analytics. Its post-relational technology combines robust objects and robust SQL, thus eliminating object-relational mapping. It delivers massive scalability on minimal hardware, requires little administration, and incorporates a rapid application development environment.

These innovations mean faster time-to-market, lower cost of operations, and higher application performance. We back these claims with this money-back guarantee: *Buy Caché for new application development, and for up to one year you can return the license for a full refund if you are unhappy for any reason.*\* Caché is available for Unix, Linux, Windows, Mac OS X, and OpenVMS – and it's deployed on more than 100,000 systems ranging from two to over 50,000 users. We are InterSystems, a global software company with a track record of innovation for more than 25 years.

Try an innovative database for free: Download a fully functional, non-expiring copy of Caché, or request it on CD, at www.InterSystems.com/Cachel5S

# CONTENTS

#### INTERVIEW

A CONVERSATION WITH ROGER SESSIONS AND TERRY COATTA 16 Queue board member Terry Coatta and "Fuzzy Boundaries" author Roger Sessions spar on the differences between objects, components, and Web services.

#### DEPARTMENTS

**NEWS 2.0 8** Taking a second look at the news so that you don't have to.

WHAT'S ON YOUR HARD DRIVE? **10** Visitors to our Web site are invited to tell us about the tools they love—and the tools they hate.

KODE VICIOUS 12 KV the Konqueror George V. Neville-Neil, Consultant

**CURMUDGEON 64** Multicore CPUs for the Masses Mache Creeger, Emergent Technology Associates Know where you are, Know where you're going,

Know where you've been

## with DevTest.

# DevTest

DevTest manages your test coverage smarter giving you a complete view of what you've tested and what you still need to test without having to break out the spreadsheets.

- · Create and manage test definitions that can be shared across environments and teams

- Establish testing targets for an entire release and then let DevTest compare your estimates to the actual results

- Schedule and assign tasks via the DevTest planning wizard

- Execute tasks, search for existing defects and submit new defects in DevTrack without having to leave DevTest

- · Associate test tasks with defects or change requests and track each test task's history

- · Analyze test results with built-in presentation quality reports

**Publisher and Editor** Charlene O'Hanlon cohanlon@acmqueue.com

#### **Editorial Staff**

Executive Editor Jim Maurer jmaurer@acmqueue.com

Associate Managing Editor John Stanik jstanik@acmqueue.com

Copy Editor Susan Holly

Art Director Sharon Reuter

**Production Manager** Lynn D'Addesio-Kraus

**Copyright** Deborah Cotton

#### **Editorial Advisory Board** Eric Allman

Charles Beeler Steve Bourne David J. Brown Terry Coatta Mark Compton Stu Feldman Stu Feldman Ben Fried Jim Gray Randy Harr Wendy Kellogg Marshall Kirk McKusick George Neville-Neil

#### Sales Staff

National Sales Director Ginny Pohlman 415-383-0203 gpohlman@acmqueue.com

Regional Eastern Manager Walter Andrzejewski 207-763-4772 walter@acmqueue.com

Regional Midwestern/ Southern Manager Sal Alioto 843-236-8823 salalioto@acmqueue.com

**Contact Points** Queue editorial queue-ed@acm.org

Queue advertising queue-ads@acm.org

Copyright permissions permissions@acm.org

Queue subscriptions orders@acm.org

Change of address acmcoa@acm.org

ACM Queue (ISSN 1542-7730) is published ten times per year by the ACM, 1515 Broadway, New York, NY, 10036-5701. POSTMASTER: Please send address changes to ACM Queue, 1515 Broadway, New York, NY 10036-5701 USA Printed in the U.S.A.

The opinions expressed by ACM Queue authors are their own, and are not necessarily those of ACM or ACM Queue.

Subscription information available online at www.acmqueue.com. BPA Worldwide Membership applied for October 2004

#### ACM Headquarters

Executive Director and CEO: John White Director, ACM U.S. Public Policy Office: Jeff Grove

Deputy Executive Director and COO: Patricia Ryan Director, Office of Information Systems: Wayne Graves Director, Financial Operations Planning: Russell Harris Director, Office of Membership: Lillian Israel

Director, Office of Publications: Mark Mandelbaum Deputy Director, Electronic Publishing: Bernard Rous Deputy Director, Magazine Development: Diane Crawford Publisher, ACM Books and Journals: Jono Hardjowirogo

Director, Office of SIG Services: Donna Baglio Assistant Director, Office of SIG Services: Erica Johnson

#### Executive Committee

President: Dave Patterson Vice-President: Stuart Feldman Secretary/Treasurer: Laura Hill Past President: Maria Klawe Chair, SIG Board: Robert A. Walker

For information from Headquarters: (212) 869-7440

ACM U.S. Public Policy Office: Cameron Wilson, Director 1100 17th Street, NW, Suite 507, Washington, DC 20036 USA +1-202-659-9711–office, +1-202-667-1066–fax, wilson\_c@acm.org

ACM Copyright Notice: Copyright © 2005 by Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies

are not made or distributed for profit or commercial advantage and that copies bear this notice and full citation on the first page. Copyright for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or fee. Request permission to republish from: Publications Dept. ACM, Inc. Fax +1 (212) 869-0481 or e-mail commissions@acm.org>

For other copying of articles that carry a code at the bottom of the first or last page or screen display, copying is permitted provided that the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, 508-750-8500, 508-750-4470 (fax). Would you believe that each component within this application is a FarPoint Spread?

> FarPoint Spread bound only by the limits of your creativity!

"Spread made it possible to deliver an intuitive application that allows management to forecast sales trends in a fraction of the time it normally would have taken to complete. Keep up the great work!"

Larry Smith Sr. Analyst/Programmer Gerber Products Company -Novartis Consumer Health N.A.

# Spread

Handling data involves more than simply typing numbers in a spreadsheet. That's why today's application developers use FarPoint Spread, a powerful component that gives you control over the complexity in .NET or COM applications for advanced user interaction and data manipulation. FarPoint is no longer simply refining spreadsheet development with this component, but redefining component architecture to deliver a powerful programming experience in a small package. With cell-level control, databinding capabilities, over

300 formula functions, and drawing shapes, Spread helps you do more than simply create spreadsheet applications. With its underlying object-oriented model, you can extend the powerful API and customize the appearance and interaction of the interface for a range of uses. From user-defined formula functions, to the hierarchical data support that permits binding to relational data, to the default cell type that handles user entry based on logic you define, you can depend on FarPoint Spread to satisfy your most demanding requirements.

## refining spreadsheet development... redefining component architecture

With a component like this, application development can be creative and fun, saving you time and effort while still giving you the functionality you need. And all of that power doesn't come at the expense of ease of use; Spread's visual designers expose much of the feature set at design-time.

Download a trial version today from www.fpoint.com and see for yourself how fun application development can be when you develop with Spread! For more information:

#### www.fpoint.com

Telephone: 919-460-4551 1-800-645-5913 "Spread has allowed us to develop a key enterprise wide business application in only 11 months. We used Spread for the navigation form and found it to be an effective way to present a 3 level hierarchy to a user."

Pete Cormier /ice President & Manager IT - ALM Services, Inc

# FarPoint

#### **Open Source/2**

IBM recently announced that it would discontinue support for its once-flagship operating system, OS/2, beginning in late 2006. Developed in the 1980s during an early alliance with Microsoft, OS/2 eventually became OS/2 Warp and had some success during the '90s, particularly in the server market. But its desktop counterpart failed to take off, and IBM eventually ceded victory to Microsoft. IBM is now urging OS/2 users to switch to Linux, which it supports. Switch to Linux? If only it were that easy. Though gone from the spotlight, OS/2 continues to run on servers around the globe, especially on those linked to ATMs. Accordingly, there remains an active community of OS/2 users, many of whom believe that OS/2 is superior to more popular alternatives in some areas (e.g., security, file system). Emblematic of this support is a petition recently signed by nearly 10,000 OS/2 users, urging IBM to make OS/2 open source.

The problem? In addition to the fact that IBM initially co-developed OS/2 with Microsoft, the operating system contains thousands of lines of code owned by third parties, so unraveling the intellectual property rights would be daunting. But loyal OS/2 users feel that, if nothing else, releasing even portions of the code would yield a useful educational resource. Whether that means learning what *to* do or what *not* to do when building an operating system is open for debate.

WANT MORE?

http://news.zdnet.co.uk/0,39020330,39209811,00.htm

#### Anti-spam Activism ... or Vigilantism?

By now it's clear that current legislation enacted to crack down on spam is ineffective by itself. We also need sound *technological* solutions to the spam problem. Much work is being done on this front. Spam-filtering tools have become ubiquitous, and promising new innovations such as SMTP Path Analysis, which uses IP information in the message header to determine the legitimacy of e-mail messages, are expanding our arsenal in the anti-spam war.

But for those who believe in taking more drastic measures, there is Blue Frog. Currently a free anti-spam solution offered by Blue Security, Blue Frog works by inviting users to add their e-mail addresses to a "do not spam" list. For each person added to the list, several fake

#### Taking a second look AT THE NEWS SO YOU DON'T HAVE TO

e-mail addresses are created, resulting in a "honey pot" that lures spammers. Spammers who send messages to those addresses are first warned to cease doing

so. If the warnings are ignored, the software triggers each user on the list to send a complaint to the URL contained in the spam. Thousands of simultaneous complaints will cripple the spammer's Web server. Honest community activism? Illegal denial of service? We'll let you decide. Slippery terrain, indeed.

WANT MORE?

http://www.linuxinsider.com/story/44867.html

#### Ride, Robot, Ride

Don't say you didn't see it coming. The latest generation of robotic technology has finally arrived: robotic camel jockeys. Oh, you're not from the United Arab Emirates? Well, let us fill you in. Camel racing, an ancient and, according to one UAE official, "indispensable" spectator sport (i.e., lots of wagering), has long been met with derision by human rights activists who criticize the sport for allowing young children to participate. They further allege that the child camel jockeys, sometimes as young as 4 years old, have been kidnapped and deliberately starved to make them as lean and mean as possible.

An answer to the critics came from a Swiss company contracted to build humanoid robots that are set to take the place of their imperiled child predecessors. The robots "sit" near the rear of the camel (post-hump) and balance with short, mechanical legs. They hold the reins with mechanical arms and hands. What might disappoint robotics enthusiasts is that these robot jockeys are not entirely autonomous; they are operated from the sidelines via remote control. This is just the beginning, though, and who knows whether more autonomous models eventually will make their way onto the sandy tracks.

No comment yet from the U.S. horse racing community, whose jockeys have been similarly criticized for having to endure grueling privations to make weight. Churchill Downs, look out! WANT MORE?

http://www.newscientist.com/article.ns?id=dn7705 Q

## Community & Quality & Excellence

NETWORK SECURITY: A Practical Approach by Jan L. Harrington

JOE CELKO'S SQL FOR SMARTIES: Advanced SQL Programming, 3rd Edition by Joe Celko

GRID COMPUTING: The Savvy Manager's Guide by Pawel Plaszczak and Richard Wellner, Jr.

MOVING OBJECTS DATABASES by Ralf Hartmut Güting and Markus Schneider

FUZZY MODELING AND GENETIC ALGORITHMS FOR DATA MINING AND EXPLORATION

by Earl Cox

DATA MODELING ESSENTIALS, THIRD EDITION by Graeme Simsion and Graham Witt

INNOVATION HAPPENS ELSEWHERE: Open Source as Business Strategy by Ron Goldman and Richard P. Gabriel

INSTANT MESSAGING SECURITY by John W. Rittinghouse and James F. Ransome

HIGHER ORDER PERL: Transforming Programs with Programs by Mark Jason Dominus

WHY PROGRAMS FAIL: A Guide to Systematic Debugging by Andreas Zeller

DEPLOYING LINUX ON THE DESKTOP by Edward L. Haletky

ORACLE DATABASE PROGRAMMING USING JAVA AND WEB SERVICES by Kuassi Mensah

ORDER FROM MORGAN KAUFMANN AND RECEIVE A 15% DISCOUNT WITH FREE SHIPPING! Refer to offer code: 82366

Mail: Elsevier, Order Fulfillment Department, 11830 Westline Drive, St. Louis, MO 63146

Phone: (800) 545-2522 / (314) 453-7010 [Intl.]

Fax: (800) 535-9935 / (314) 453-7095 [Intl.]

Web: www.mkp.com

Email: usbkinfo@elsevier.com

Volume Discounts: naspecialsales@elsevier.com

## What's on Your Hard Drive?

WOYHD is a forum for expressing your opinions on the tools you love and loathe. Tools, as we've made clear, can be anything from programming languages to IDEs to database products. This month we've taken liberties with the definition to include the Linux music software praised below. Listening to music can help us get through those long hours spent unraveling lines of spaghetti code (someone else's, of course). It can also make some people completely unproductive, but cannot the same be said of many other, more obvious "tools"? Don't get us wrong, though—never, under any circumstances, will Minesweeper be considered a tool!

#### Who: Chris Bellini

What industry: Manufacturing Job title: Software developer Flavor: Develops on Windows for Windows

use Python. Also, with free tools such as wxPython and py2exe, a Python script can easily become a fullblown distributable application with a robust UI.

**Tool I hate!** Microsoft Visual Studio .NET. It's a love/hate relationship. On the one hand, it's my bread and butter and I've learned to use many of its features. On the other hand, it has become a bloated resource hog that makes things sluggish while a large

hog that makes things sluggish while a large app, such as CAD/CAM, is running simultaneously.

Who: Guilherme Mauro Germoglio BarbosaWhat industry: EducationJob title: Software developer

Flavor: Develops on Linux for Linux

**Tool I love!** XMMS. I simply cannot focus on my work without any music. Programming is a bit of a lonely task, and listening to music helps combat

this loneliness. 24/7 listening to music = 24/7 programming!

**Tool I hate!** CTTE. This tool is a bit buggy—only five minutes of use produced six exceptions. I hope they improve it. Maybe it will be very useful in the future.

But there's another problem: programming is fun—crafting artifacts that no one really cares about (such as those created by CTTE) is not.

#### Who: John Styles

What industry: Technology vendor Job title: Chief architect Flavor: Develops on Windows for Windows

**Tool I love!** Awk. Within its chosen problem domain, nothing can beat Awk's elegance and simplicity. It is easy to deploy, and its syntax is simpler and more rational than certain other scripting

languages I could mention. I often try other tools but come back to the one that always does the job. **Tool I hate!** OLE DB. If OLE DB were just another bizarre, overly complex, overly abstract, poorly documented API, then I could just happily ignore it. Unfortunately, it is the native data access API for Microsoft SQL Server, so it cannot be avoided. If only there were a decent simple C language API for it, such as Oracle's OCI.

What industry: Not-for-profit Job title: Software engineer Flavor: Develops on Windows for Unix

**Tool I love!** Eclipse. Eclipse allows me to be much more productive by assisting with syntax and generating many standard, repetitive code blocks. The refactoring tools make otherwise unthinkable-to-tackle

tasks (such as renaming/repackaging a frequently used class) almost trivial.

**Tool I hate!** PVCS Version Manager. The X interface is slow, clunky, and unstable. Open projects some-

times disappear, many error messages inaccurately represent the cause of the problem...and did I mention that it's slow? It represents the antithesis of the productivity gains I get by using Eclipse.

## GET YOUR STAFF TO WRITE BETTER CODE, FASTER.

IF THAT MAKES YOU GIGGLE WITH EXCITEMENT, YOU AIN'T SEEN NOTHIN' YET.

BIGGER BRAINS = BIGGER BOTTOM LINE. TURN YOUR TEAM INTO WINTELLECTUALS TODAY. FOR SUPERIOR .NET CONSULTING, TRAINING, DEBUGGING, CALL 877.968.5528 OR VISIT WINTELLECT.COM

## KV the Konqueror

t's been a couple of months, and Kode Vicious has finally returned from his summer vacation. We asked him about his travels and the only response we got was this: "The South Pole during winter ain't all it's cracked up to be!" Fortunately, he made it back in one piece and is embracing the (Northern hemisphere's) late summer balminess with a fresh installment of koding kwestions. This month, KV follows up on a security question from a previous column and then revisits one of koding's most divisive issues: language choice. Welcome back!

#### Dear KV,

Suppose I'm a customer of Sincere-and-Authentic's ("Kode Vicious Battles On," April 2005:15-17), and suppose the sysadmin at my ISP is an unscrupulous, albeit music-loving, geek. He figured out that I have an account with Sincere-and-Authentic. He put in a filter in the access router to log all packets belonging to a session between me and S&A. He would later mine the logs and retrieve the music—without paying for it.

I know this is a far-fetched scenario, but if S&A wants his business secured as watertight as possible, shouldn't he be contemplating addressing it, too? Yes, of course, S&A will have to weigh the risk against the cost of mitigating it, and he may well decide to live with the risk. But I think your correspondent's suggestion is at least worthy of a summary debate—not something that should draw disgusted looks!

There is, in fact, another advantage to encrypting the payload, assuming that IPsec (Internet Protocol security) isn't being used: decryption will require special clients, and that will protect S&A that much more against the theft of merchandise.

Balancing is the Best Defense

Got a question for Kode Vicious? E-mail him at kv@acmqueue.com—if you dare! And if your letter appears in print, he may even send you a Queue coffee mug, if he's in the mood. And oh yeah, we edit letters for content, style, and for your own good! A koder with attitude, kv answers your questions. Miss manners he ain't.

#### Dear Balancing,

Thank you for reading my column in the April 2005 issue of *Queue*. It's nice to know that someone is

paying attention. Of course, if you had been paying closer attention, you would have noticed that S&A said, "In the design meeting about this I suggested we just encrypt all the connections from the users to the Web service because that would provide the most protection for them and us." That phrase, "just encrypt all the connections," is where the problem lies.

Your scenario is not so far-fetched, but S&A's suggestion of encrypting all the connections would not address the problem. Once users have gotten the music without their evil ISPs sniffing it, they would still be able to redistribute the music themselves. Or, the evil network admin would sign up for the service and simply split the cost with, say, 10 of his music-loving friends, thereby getting the goods at a hefty discount. What S&A really needs is what is now called digital rights management. It's called this because for some reason we let the lawyers and the marketing people into the industry instead of doing with them what was suggested in Shakespeare's *Henry VI*.

What S&A failed to realize was that the biggest risk of revenue loss was not in the network, where only a small percentage of people can play tricks as your ISP network administrator can, but at the distribution and reception points of the music. Someone who works for you walking off with your valuable information is far more likely than someone trying to sniff packets from the network. Since computers can make perfect copies of data (after all, that's how we designed these things in the first place), it is the data itself that must be protected, from one end of the system to the other, in order to keep from losing revenue.

All too often, people do not consider the end-to-end design of their systems and instead try to fix just one part. KV

#### Dear KV,

Since there was some debate in my company over the following issue, I'm curious to see what you believe: put-

## Perforce. The fast SCM system.

For developers who don't like to wait.

Tired of using a software configuration management system that stops you from checking in your files? Perforce SCM is different: fast and powerful, elegant and clean. Perforce works at your speed.

[Fast]

[Scalable]

[Distributed]

Perforce's lock on performance rests firmly on three pillars of design. A carefully keyed relational database ensures a rapid response time for small operations plus high throughput when the requests get big millions of files big. An efficient streaming network protocol minimizes the effects of latency and maximizes the benefits of bandwidth. And an intelligent, server-centric data model keeps both the database and network performing at top speed.

It's your call. Do you want to work, or do you want to wait?

Download a free copy of Perforce, no questions asked, from www.perforce.com. Free technical support is available throughout your evaluation.

All trademarks used herein are either the trademarks or registered trademarks of their respective owners.

## kode vicious

ting aside performance issues (which I think are relatively minor on modern PCs), when would you recommend using C++ for development, and when would you recommend C? Do you think it is always better to use C++?

My feeling is that unless your application is inherently object oriented (e.g., user interfaces), C++ will tend to make the implementation worse instead of making it better (e.g., constructors and operators doing funny unexpected things; C++ experts trying to "use their expertise" and writing C++ code that is very efficient but extremely hard to read and not portable; huge portability—and performance—issues when using templates; incomprehensible compiler/linker error messages; etc., etc.). I also think that although people can write bad C code (gotos out of macros was a nice one), typically people can write *awful* C++ code. Where do you stand on this dispute? Wondering How Much + There is in ++

#### Dear Wondering,

Choosing a language is something I've addressed before in other letters, but the C vs. C++ debate has raged as long as the two languages have been in existence, and, really, it's getting a bit tiring. I mean, we all know that assembler is the language that all red-blooded programmers use! Oh, no, wait, that's not it.

I'm glad you ask this question, though, because it gives me license to rant about it—and to dispel a few myths.

The first, and most obvious, myth in your letter is that user interfaces are inherently object oriented. Although many introductory textbooks on object-oriented programming have user interfaces as their examples, this has a lot more to do with the fact that humans like pretty pictures. It is far easier to make a point graphically than with text. I have worked on object-oriented device drivers, which are about as far as you'll ever get from a user interface.

Another myth that your letter could promulgate is that C is not an object-oriented language. A good example of object-oriented software in C is the vnode filesystem interface in BSD Unix and other operating systems. So, if you want to write a piece of object-oriented software, you can certainly do it in C or C++, or assembler for that matter.

One final myth, which was actually dispelled by Donn Seeley in "How Not To Write Fortran in Any Language" (*ACM Queue*, December/January 2004-2005:58-65), is that C++ leads to less understandable code than C. Over the past 20 years I have seen C code that was spaghetti and C++ code that was a joy to work on, and vice versa.

So, after all that myth bashing, what are we left with?

- What language is most of the team experienced in? If you're working with a team and six out of eight of them are well versed in C but only two know C++, then you're putting your project, and job, at risk in picking C++. Perhaps the two C++ koders can teach the C folks enough C++ to be effective but it's unlikely. To estimate the amount of work necessary for a task, you have to understand your tools. If you don't normally use a nail gun, then you're likely to take someone's toe off with it. Losing toes is bad, as you need them for balance.

- Does the application require any of the features of the language you're using? C and C++ are a lot alike as languages (i.e., in syntax), but they have different libraries of functions and different ways of working that may or may not be relevant to your application. Often realtime constraints require the use of C because of the control it can provide over the data types. If type safety is of paramount importance, then C++ is a better choice because that is a native part of the language that is not present in C.

- Does the application require services from other applications or libraries that are hard to use or debug from one or the other language? Creating shim layers between your code and the libraries you depend on is just another way of adding useless, and probably buggy, code to your system. Shim layers should be avoided like in-laws. They're OK to talk about, and you might consider keeping them around for a week, but after that, out they go as so much excess, noisy baggage.

There are lots of other reasons to choose one language over another, but I suspect that the three listed here should be enough for you and your team to come to some agreement. You'll notice that none of them has to do with how easy it is to understand templates or how hard it is to debug with exceptions.

ΚV

**KODE VICIOUS**, known to mere mortals as George V. Neville-Neil, works on networking and operating system code for fun and profit. He also teaches courses on various subjects related to programming. His areas of interest are code spelunking, operating systems, and rewriting your bad code (OK, maybe not that last one). He earned his bachelor's degree in computer science at Northeastern University in Boston, Massachusetts, and is a member of ACM, the Usenix Association, and IEEE. He is an avid bicyclist and traveler who has made San Francisco his home since 1990. © 2005 ACM 1542-7730/05/0900 \$5.00

# igrep.com

## Developer Search Engine?

COOL.

Powered by Developer Shed, Inc. (www.DeveloperShed.com)

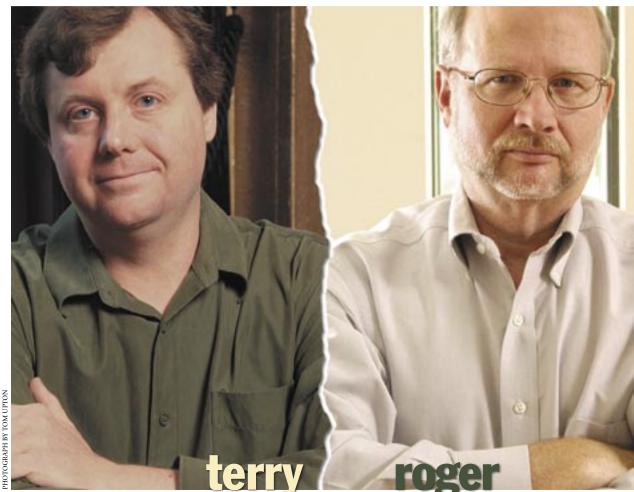

## A Conversation with Roger Sessions and Terry Coatta

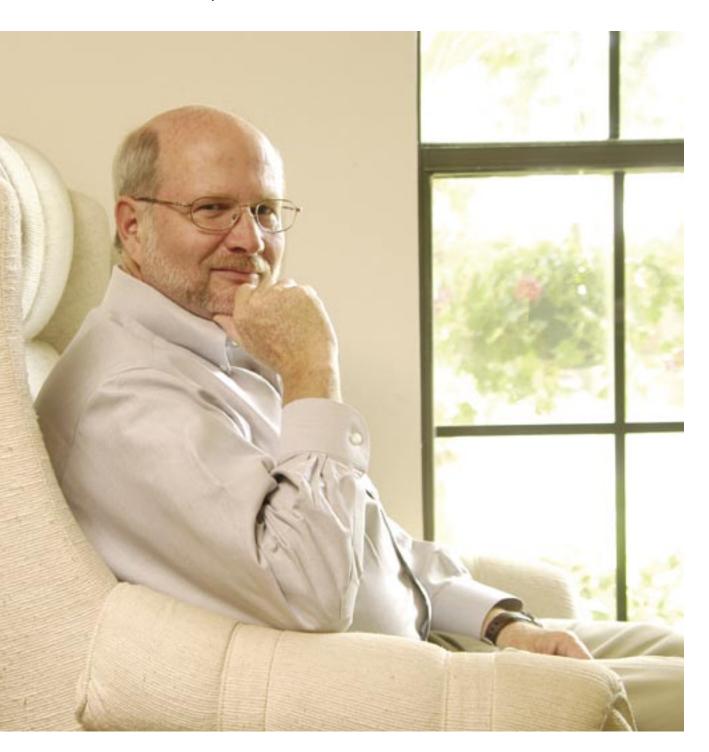

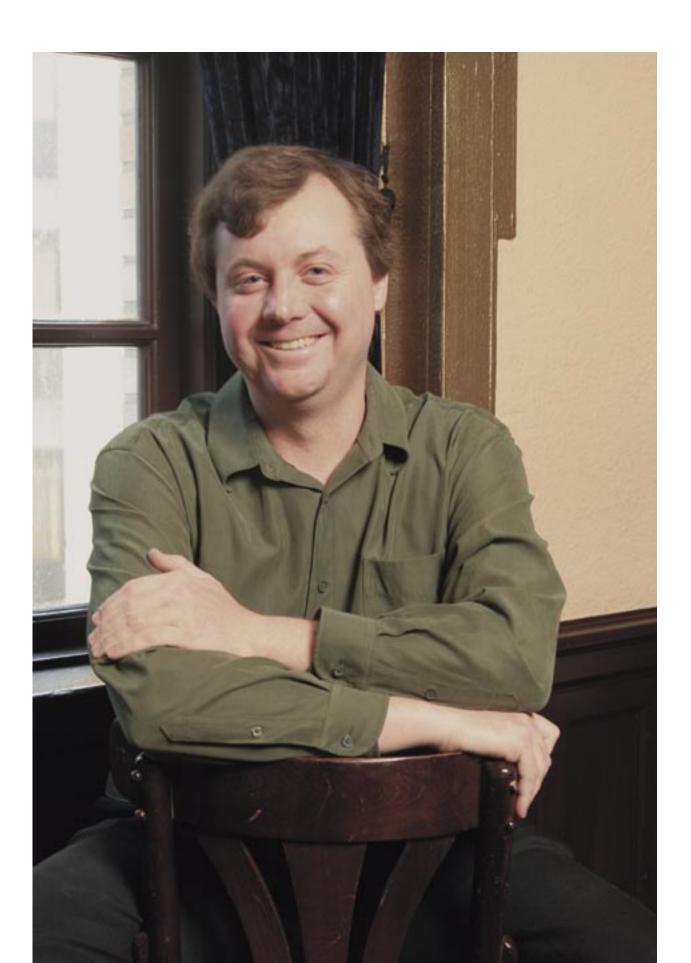

n the December/January 2004-2005 issue of *Queue*, Roger Sessions set off some fireworks with his article about objects, components, and Web services and which should be used when ("Fuzzy Boundaries," 40-47). Sessions is on the board of directors of the International Association of Software Architects, the author of six books, writes the Architect Technology Advisory, and is CEO of ObjectWatch. He has a very object-oriented viewpoint, not necessarily shared by *Queue* editorial board member Terry Coatta, who disagreed with much of what Sessions had to say in his article. Coatta is an active developer who has worked extensively with component frame-

#### The difference

BETWEEN OBJECTS AND COMPONENTS? THAT'S DEBATABLE.

works. He is vice president of products and strategy at Silicon Chalk, a startup software company in Vancouver, British Colum-

bia. Silicon Chalk makes extensive use of Microsoft COM for building its application. Coatta previously worked at Open Text, where he architected CORBA-based infrastructures to support the company's enterprise products.

We decided to let these two battle it out in a forum that might prove useful to all of our readers. We enlisted another *Queue* editorial board member, Eric Allman, CTO

**Application Development Lifecycle**

A special advertising supplement with this issue of Queue

### interview

of Sendmail Inc., to moderate what we expected to be quite a provocative discussion. Our expectations were dead on.

**ERIC ALLMAN** I've talked to people who work on objectoriented stuff, who have read your "Fuzzy Boundaries" article, Roger, and every single one of them starts off by disagreeing that the difference between objects, components, and Web services is location-based.

Many of them speak of object-oriented RPCs (remote procedure calls), which aren't quite components. They are components that live together in a process and so forth. Since that was the fundamental point of your article, could you comment?

**ROGER SESSIONS** Unfortunately, none of these terms is very well defined. We're all using the terms as they make sense to us. Some of our disagreement may be simply semantic.

The component industry started with CORBA. The developers of CORBA were trying to solve one problem: distribution. They weren't trying to get objects to work together within the same process. Yes, you *could* have CORBA objects live together on the same machine, even in the same process, but that was not the main problem that CORBA cared about solving.

As far as Web services go, we could say that, yes, Web services *could* be in the same process or on the same machine. They *could* be in the same environment. But what was the essential problem Web services were trying to solve? It is about heterogeneous environments. It is about getting a .NET system to work with a WebSphere system, for example, not getting a .NET system to work with another .NET system.

**TERRY COATTA** It strikes me that it's hard to distinguish Web services from CORBA from EJB using that kind of rationale, because all three systems have open or at least standardized and available protocols. I can certainly make my WebSphere interoperate with an appropriate CORBA implementation that has the mappings for doing EJB. I can cross technology boundaries with all kinds of different standards.

**RS** If you're using the J2EE standards such as RMI (remote method invocation) over IIOP (Internet Inter-ORB Protocol), you are primarily going to be doing that within a single vendor's system, such as a WebSphere system. If you're going from a WebSphere system to a WebLogic system, your best shot at interoperability is through Web services. Why? Because you're crossing a technology boundary.

**TC** You're claiming that RMI over IIOP doesn't actually work?

**RS** It doesn't work for interoperability across technology boundaries.

**TC** There seem to be people out there getting it to work. Certainly, back in the days when I worked with CORBA there was no problem having different vendors' ORBs (object request brokers) interoperate with one another.

We used three or four of them at Open Text and had no difficulty at all with those environments interoperating with one another.

**RS** As long as you're going CORBA to CORBA, it works fine. But not when you are trying to get a CORBA system to work with a non-CORBA system.

**TC** But going from WebSphere to one of the other EJB vendors (e.g., WebLogic) in the CORBA space, there were probably five or six different major ORB vendors floating around, not to mention a couple of open source efforts, and all of those interoperated really well with one another.

## interview

**RS** CORBA to CORBA. They're all running on the same basic core of CORBA technology. The difference between that and Web services is that for Web services, unlike CORBA, there is no assumption whatsoever about what the underlying technology is.

**TC** That's not true. There's an assumption that one is using a certain set of protocols; otherwise, it doesn't work, and I mean CORBA was the same thing-a standard set of protocols. Nobody said that you had to actually implement the server-side aspect of the CORBA stuff to interoperate over the Internet. Everybody did because that's the way they defined the standards.

**RS** You could say the same thing about DCOM or RMI. While all of them support communications protocols, they, like CORBA, are about much more than communications protocols. They are about a platform. CORBA was 95 percent API, 5 percent interoperability. Web services is zero API and 100 percent interoperability.

**TC** That part I agree with, absolutely. That was probably the downfall of CORBA.

**RS** It's exactly the downfall of CORBA, and it will also be the downfall of J2EE. They didn't learn from that mistake. EA Isn't Web services just essentially another standard for how to interact? The world has settled on CORBA protocols, not CORBA implementations. Wouldn't it have had exactly the same effect and maybe even better had the world agreed to use only the CORBA protocols? RS It's quite possible, but the world didn't. CORBA lacked

focus. The Web services effort has a lot of focus beyond interoperability.

The big difference between Web services and CORBA is that the Web services people said right from the beginning: there is no API. The only thing that we standardize is how messages go from one system to another and the coordination around that. CORBA was 95 percent about how the client binds into the system. That was its downfall.

**TC** Of course, from the perspective of a programmer, that's not necessarily a downfall, but a shortcoming. CORBA provided very nice interceptor architecture, a basic mechanism for dispatch, which everybody in Web services land has to rebuild from scratch. You can see that coming out now in the various Web services standards.

We were able to build an OTS (object transaction service) implementation on top of CORBA because of the appropriate interceptor mechanisms, support for global thread IDs, etc., etc. That work is taking a huge amount of time in Web services land, of course, because nobody has the infrastructure for it.

**RS** I've dedicated quite a few years of my life to CORBA,

and there were some very good ideas in it. Unfortunately, there was so much baggage that those good ideas were never allowed to flourish.

Hopefully we've learned from those mistakes. The only successful part of CORBA-of that massive effort, of those millions and millions and millions of dollars that were spent—was the tiny sliver of it that had to do with interoperability.

**TC** It wasn't just the interoperability. That was a big part of it, but the notion of a standard mechanism for interception and dispatch on the actual implementation side was also hugely successful because it allowed one to deploy things like OTS in a reasonable way without everybody having to basically rediscover from the ground up how to do that kind of stuff.

RS The reality is that CORBA is mostly about APIs, none of which anybody uses.

TC I agree. I was involved in the CORBA world, too, and of all of the interface specifications and the verticals, very little of them amounted to anything. But I think that although it's true historically to say one of the driving things behind CORBA was this desire to make things talk across the network to one another in interoperable fashion, the reality of it is that when people started using CORBA, they discovered the power that the standardized infrastructure offered. The basic server-side architecture, with standards for the dispatch mechanism, the interceptor mechanism, object lifecycle, and object identification, is an extremely powerful tool in the hands of developers actually delivering working systems.

**RS** Lots of things worked well in CORBA, as long as both sides agree that they're in a CORBA world.

The Web services world is certainly borrowing ideas from CORBA, as CORBA borrowed ideas from earlier technologies. What they're trying to do in Web services is borrow the few ideas in CORBA that actually panned out. EA I get the distinct impression, Roger, that your attitude is CORBA failed, and Web services has succeeded. Yet CORBA is used for lots of very real things.

CNN, for example, uses CORBA. Most phone systems use CORBA. And the poster-child example of Web services has been Google. It looks to me like CORBA is more of a success than Web services.

**RS** I totally disagree with that. I would say that relatively **RS** I totally disagree with that. I would say that relatively few CORBA applications have panned out. Anybody who is investing any money in a CORBA architecture is making a big mistake. None of the major players that was instrumental in bringing CORBA about is investing in its future. IBM is investing nothing into CORBA. Sun is investing nothing

## interview

into CORBA. Microsoft never cared about CORBA. So who is investing in it? Some marginal player someplace.

When you mention Google, you're talking about a very specific, and limited, application. When you look at Web services, you really need to categorize it into one of two types of applications: inter-enterprise or intra-enterprise. Google is an example of inter-enterprise.

My position has always been that inter-enterprise is a marginal area of Web services. It's the one that Microsoft and IBM peddle when they're talking to everybody about this. But the much more important area for Web services—the one that's being used many, many places—is getting different technology systems to interoperate

within the same enterprise. **EA** Roger made the rather telling statement that Microsoft never looked at CORBA. Could I make a legitimate argument that CORBA failed and Web services "succeeded"-and I'm not admitting that yet-because of the Microsoft hegemony over the world? What I'm suggesting is, had Microsoft supported CORBA, would we not be talking about Web services at all?

**RS** No, because Microsoft is not what killed CORBA. J2EE killed CORBA. If you want to blame somebody for killing CORBA, blame IBM and Sun, because all at the major enterprise players, which are, in my view, BEA, IBM, and Microsoft, they are all doing the best job they can to make it as transparent as possible to use Web services.

They did a similar thing with components. They tried to make it very easy to use them, and the problem was that people really never understood what the fundamental differences were between these technologies: objects, components, and Web services.

In some sense, the transparent ability to make something a Web service is not really a good thing, because making an effective Web service requires a much more in-depth understanding of what it means to be a Web

the major players that were originally looking at CORBA as their savior technology abandoned it and moved on to J2EE.

**TC** I actually agree, totally, with Roger on this. But it seems to me that one of the reasons we have a huge wealth of Web services stuff cropping up is because our friends at Microsoft are making it completely trivial to build Web services, in the sense that you simply build .NET implementations and then say, "Hey, I'd like to have the Web interfaces available for these."

Do you think that's true? Are the tools that are making Web services essentially transparent to the developer responsible for part of why they are so popular and why we're seeing a lot of these services inside the enterprises? **RS** There is some truth to that. Certainly, if you look service. It's the same with components. These tools don't give you that. They give you the ability to slap a SOAP interface on top of some code, and that's it.

EA How do you think this is going to affect the evolution of Web services? Given that people are going to use these tools, is this going to result in a huge period of extremely poor architectures because people have just slopped Web services on top of existing architectural solutions?

RS Yes, that's my expectation. We have great tools today for building Web services and virtually no understanding of why, when, and where we should build Web services.

EA I'm curious about your view of the developer's world when building up a system. Clearly you believe that one has to see the boundaries between what you refer to as objects and components and Web services. But do those

differences actually translate in your mind to very specific different implementation technologies? Are objects truly different from components, or is it just a design distinction about the role that something plays in the system? **RS** I see it as more a design distinction. Just to give you a simple example: state management. If you have an object, it's perfectly OK to keep state in the object long-term. As long as the object lives, it can have state in it. In a component, you can't do that. You've got to get the state out of there or your component will not scale. None of the tools tells you that. You have to know that, and you have to design the system accordingly.

Just because you can use objects to implement your

ary. But location and environmental boundaries have many implications in terms of security, transactions, and other design issues.

**EA** There's a very, very strong impression that came out of this article, and that is if I'm going to use components, I would never ever consider using components in something in the same process. But I've talked to a number of people now who have said, "Nonsense, we do that all the time, and it's an important point of our flexibility." **RS** Then they're really using the wrong technology for what they're doing. They should just be using object technology for that.

**TC** No, that's false. One of the elements that defines a

components doesn't mean that objects and components are semantically equivalent. State management is one example, but there are many others. These are design issues, not technology issues.

**EA** Now you've just introduced the semantic element. There are lots of semantics that objects have—polymorphism, encapsulation, inheritance—which you can sort of build into Web services, perhaps just as I can write objectoriented C, but it's not the same thing.

**RS** It's not even clear that that's a good idea. In my mind, to have inheritance on top of a Web service is probably a bad idea.

In the "Fuzzy Boundaries" article I said that the defining characteristics that differentiate objects, components, and Web services are location and environmental boundcomponent architecture is the point of interception. This is incredibly useful even if I have things talking within the same process, because it gives me the opportunity to, for example, track invocation patterns without actually having to disturb my architecture at all.

We actually do this for the product that we're building at Silicon Chalk. We transparently introduce a layer of debugging proxies and get all kinds of tracing information that vastly improves our ability to debug the system. We couldn't do that if we were building it out of C++

without having some base class nightmare to deal with.

So the fact that component technology provides a point of interception actually turns out to be an incredibly valuable tool to the developer.

**RS** There are object systems that provide that as well. You're picking on the shortcomings of a particular language and using that to condemn all object-oriented systems. That's not fair. If you need interception, if that's a useful tool, then you choose an object technology that provides interception.

**TC** I don't have those choices as a developer out in the real world. Sometimes you have to work in a particular language or system. That's the land that I live in, and that's the reality for most developers as well. Component systems offer me the power that I need to build my

### interview

product and deliver it to my customers. Now it's true, if I had been programming in Smalltalk, I could go in there and fiddle with the dispatch mechanism. But I don't have that option.

**RS** That's unfortunate. You chose the wrong language. **TC** I chose the only language that made any sense, given the other realities of the world that I deal with. It's nice to talk about distinctions between objects and components as if one could make a completely free choice about how to implement things, but the real world doesn't work that way. As a person who is responsible for actually getting a product out the door and satisfying customers, you can't choose arbitrary technologies because they happen to satisfy purist notions of what is appropriate.

**RS** If you're saying that you are using one particular aspect of one particular component technology to make up for a regrettable constraint on one particular programming language, then that's OK. Do what you need to do. But just because you are using interception doesn't make it a defining difference between components and objects. That's just a particular artifact of the constraints that you happen to be working under.

**EA** OK, gentlemen, let's shift gears a little. In the course of this discussion we've hit upon various standardization efforts that have come out or are evolving. For example, a

architecting tomorrow's computing

lot of stuff is happening with WS security and WS transactions, WSDL (Web Services Description Language), and UDDI (Universal Description, Discovery, and Integration). I'm curious to get Roger's point of view on which of these things are good, and where we should be doing things differently. There are lots of standards out there, and, frankly, they're at least as hard, if not harder, to understand than some of the CORBA specifications were.

**RS** I agree that the Web services standards are harder to understand than most of the CORBA specifications, but there's one fundamental difference between these specifications and the CORBA ones. The CORBA specifications had to be understood by developers. The Web services standards don't. Nobody needs to understand the Web services standards except for Microsoft and IBM because these standards are about how Microsoft and IBM are going to talk together, not about how the developer is going to do anything.

**EA** So, nobody is ever going to interact except Microsoft and IBM?

**RS** The people who are building the platforms are the ones who care about these standards. These standards have no relevance to Joe or Jane Developer, none whatsoever.

**TC** Do you mean that Joe or Jane Developer is never

## Coming in the October issue

## **Semi-Structured Data**

Are ontologies the answer?

How XML can help

Lessons learned from the Web

acm

going to make use of anything that uses UDDI? **RS** They're going to use things that make use of UDDI, but UDDI is going to be at a much lower level than anything they will see.

**TC** You are saying that they'll never see UDDI?

**RS** They will see their particular vendors' tools for using UDDI. But they're not going to see UDDI itself. It's like a Web developer worrying about TCP/IP. Yes, they're going to use it, but they're not going to see it.

**TC** So, again, looking at this from a developer's point of view, I'm going to build a service-oriented architecture and basically you're saying I don't need to know any-thing about Web services standards, but I need to know about Web services as an abstract idea in order to get my architecture correct.

**RS** You need to understand architecturally what you need to do to build effective Web services, but as far as how the Web services standards move information around, that's not your problem.

**TC** What about issues of performance?

dtSearch

**RS** You'll need to know what your vendor supports. These standards are not about development. They are about interoperability among different vendor platforms.

Look at the standards. Give me one example of a standard that would bubble through to a developer? One API that has been defined in all the Web services that would bubble back to a developer? There aren't any! **TC** It sounds like what you're saying is that the tools that automatically supply Web services interfaces are, in fact, absolutely necessary because they're that insulation between the developers and the underlying protocols. At the same time, they're the downfall that's making it possible to generate poorly architected systems. Two-edged sword?

**RS** Even if you didn't have those tools, it would still be perfectly possible to implement poor systems. In fact, it's probably even easier because you'd have a lot more things you could mess up.

Perhaps you could argue that without these tools, you would have to know so much about Web services that you would be bound to pick up some design smarts somewhere along the path. I think the answer to this dilemma is not to get rid of the tools, but to educate people, through magazines such as *Queue*, that show them the right way to build these things. Q

#### LOVE IT, HATE IT? LET US KNOW

feedback@acmqueue.com or www.acmqueue.com/forums

© 2005 ACM 1542-7730/05/0900 \$5.00

## **NEW Version 7 Terabyte Indexer**

#### The Smart Choice for Text Retrieval® since 1991

- over two dozen indexed, unindexed, fielded & full-text search options

- highlights hits in HTML, XML and PDF while displaying embedded links, formatting and images

- converts other file types (word processor, database, spreadsheet, email, ZIP, Unicode, etc.) to HTML for display with highlighted hits

#### **Reviews of dtSearch**

- "The most powerful document search tool on the market" Wired Magazine

- "dtSearch ... leads the market" Network Computing

- "Blindingly fast" Computer Forensics: Incident Response Essentials

- $\blacklozenge$  "A powerful arsenal of search tools" The New York Times

- "Super fast, super-reliable" The Wall Street Journal

- "Covers all data sources ... powerful Web-based engines" eWEEK

- ◆ "Searches at blazing speeds" Computer Reseller News Test Center

See www.dtsearch.com for hundreds more reviews & case studies

#### 1-800-IT-FINDS • www.dtsearch.com

Desktop with Spider (\$199) Network with Spider (trom \$800) Web with Spider (trom \$999) Publish for CD/DVDs (trom \$2,500) Engine for Win & .NET Engine for Linux

Instantly Search

Terabytes of Text

# The Future of Microprocessors

KUNLE OLUKOTUN AND LANCE HAMMOND, STANFORD UNIVERSITY

Chip multiprocessors' promise of huge performance gains is now a reality.

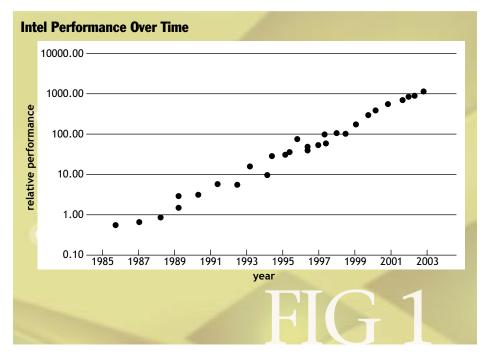

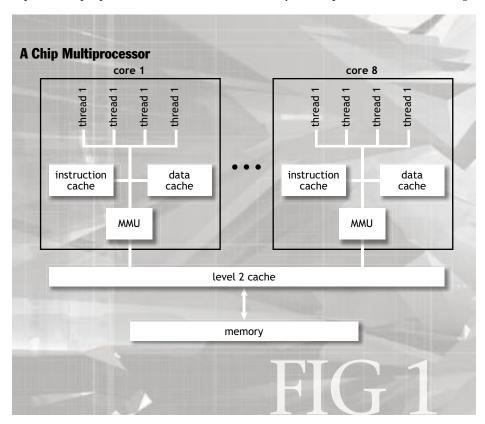

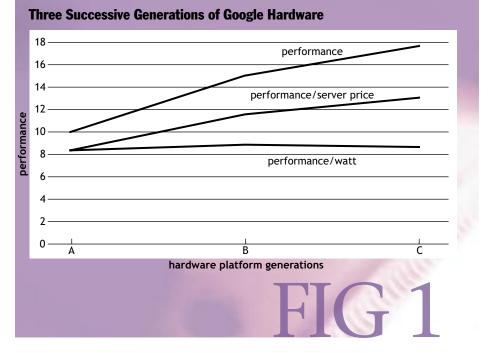

he performance of microprocessors that power modern computers has continued to increase exponentially over the years for two main reasons. First, the transistors that are the heart of the circuits in all processors and memory chips have simply become faster over time on a course described by Moore's law,<sup>1</sup> and this directly affects the performance of processors built with those transistors. Moreover, actual processor performance has increased *faster* than Moore's law would predict,<sup>2</sup> because processor designers have been able to harness the increasing numbers of transistors available on modern chips to extract more *parallelism* from

software. This is depicted in figure 1 for Intel's processors.

An interesting aspect of this continual quest for more parallelism is that it has been pursued in a way that has been virtually invisible to software programmers. Since they were invented in the 1970s, microprocessors have continued to implement the conventional von Neumann computational model, with very few exceptions or modifications. To a programmer, each computer consists of a single processor executing a stream of sequential instructions and connected to a monolithic "memory" that holds all of the program's data. Because the economic benefits of backward compatibility with earlier generations of processors are so strong, hardware designers have essentially been limited to enhancements that have maintained this abstraction for decades. On the memory side, this has resulted in processors with larger cache memories, to keep frequently accessed portions of the conceptual "memory" in small, fast memories that are physically closer to the processor, and large register files to hold more active data values in an

# The Future of **Microprocessors**

extremely small, fast, and compiler-managed region of "memory."

Within processors, this has resulted in a variety of modifications designed to achieve one of two goals: increasing the number of instructions from the processor's instruction sequence that can be issued on every cycle, or increasing the clock frequency of the processor faster than Moore's law would normally allow. Pipelining of individual instruction execution into a sequence of stages has allowed designers to increase clock rates as instructions have been sliced into larger numbers of increasingly small steps, which are designed to reduce the amount of logic that needs to switch during every clock cycle. Instructions that once took a few cycles to execute in the 1980s now often take 20 or more in today's leading-edge processors, allowing a nearly proportional increase in the possible clock rate.

Meanwhile, superscalar processors were developed to execute multiple instructions from a single, conventional

order. Of course, this illusion is not absolute. Performance can often be improved if programmers or compilers adjust their instruction scheduling and data layout to map more efficiently to the underlying pipelined or parallel architecture and cache memories, but the important point is that old or untuned code will still execute correctly on the architecture, albeit at less-than-peak speeds.

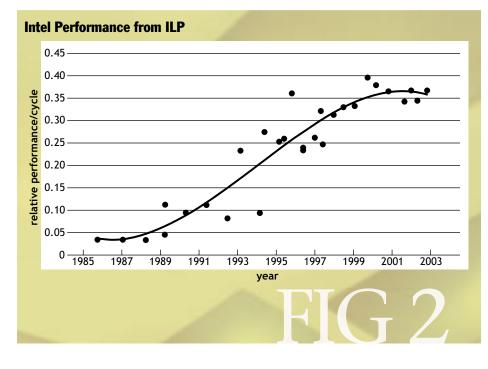

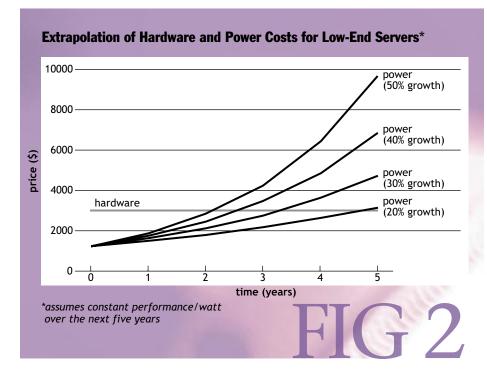

Unfortunately, it is becoming increasingly difficult for processor designers to continue using these techniques to enhance the speed of modern processors. Typical instruction streams have only a limited amount of usable parallelism among instructions,<sup>3</sup> so superscalar processors that can issue more than about four instructions per cycle achieve very little additional benefit on most applications. Figure 2 shows how effective real Intel processors have been at extracting instruction parallelism over time. There is a flat region before instruction-level parallelism was pursued intensely, then a steep rise as parallelism was utilized usefully, followed by a tapering off in recent years as the available parallelism has become fully exploited.

Complicating matters further, building superscalar processor cores that can exploit more than a few instructions per cycle becomes very expensive, because the complexity of all the additional logic required to find parallel instructions dynamically is approximately proportional to the square of the number of instructions that can be issued simultaneously. Similarly, pipelining past about 10-20 stages is difficult because each pipeline stage becomes too short to perform even a minimal amount of

instruction stream on each cycle. These function by dynamically examining sets of instructions from the instruction stream to find ones capable of parallel execution on each cycle, and then executing them, often out of order with respect to the original program.

Both techniques have flourished because they allow instructions to execute more quickly while maintaining the key illusion for programmers that all instructions are actually being executed sequentially and in order, instead of overlapped and out of

rants: feedback@acmqueue.com

logic, such as adding two integers together, beyond which the design of the pipeline is significantly more complex. In addition, the circuitry overhead from adding pipeline registers and bypass path multiplexers to the existing logic combines with performance losses from events that cause pipeline state to be flushed, primarily branches. This overwhelms any potential performance gain from deeper pipelining after about 30 stages.

Further advances in both superscalar issue and pipelining are also limited by the fact that they require everlarger numbers of transistors to be integrated into the high-speed central logic within each processor core—so many, in fact, that few companies can afford to hire enough engineers to design and verify these processor cores in reasonable amounts of time. These trends have slowed the advance in processor performance somewhat and have forced many smaller vendors to forsake the high-end processor business, as they could no longer afford to compete effectively.

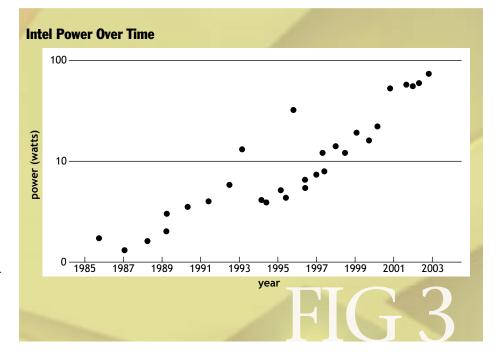

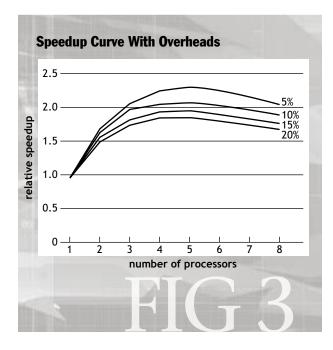

Today, however, all progress in conventional processor core development has essentially stopped because of a simple physical limit: power. As processors were pipelined and made increasingly superscalar over the course of the past two decades, typical high-end microprocessor power went from less than a watt to over 100 watts. Even though each silicon process generation promised a reduction in power, as the ever-smaller transistors required less power to switch, this was true in practice only when existing designs were simply "shrunk" to use the new process technology. Processor designers, however, kept using more transistors in their cores to add pipelining and superscalar issue, and switching them at higher and higher frequencies. The overall effect was that exponentially more power was required by each subsequent processor generation (as illustrated in figure 3).

Unfortunately, cooling technology does not scale exponentially nearly as easily. As a result, processors went from needing no heat sinks in the 1980s, to moderate-size heat sinks in the 1990s, to today's monstrous heat sinks, often with one or more dedicated fans to increase airflow over the processor. If these trends were to continue, the next generation of microprocessors would require very exotic cooling solutions, such as dedicated water cooling, that are economically impractical in all but the most expensive systems.

The combination of limited instruction parallelism suitable for superscalar issue, practical limits to pipelining, and a "power ceiling" limited by practical cooling limitations has limited future speed increases within conventional processor cores to the basic Moore's law improvement rate of the underlying transistors. This limitation is already causing major processor manufacturers such as Intel and AMD to adjust their marketing focus away from simple core clock rate.

Although larger cache memories will continue to improve performance somewhat, by speeding access to the single "memory" in the conventional model, the simple fact is that without more radical changes in pro-

cessor design, microprocessor performance increases will slow dramatically in the future. Processor designers must find new ways to *effectively* utilize the increasing transistor budgets in high-end silicon chips to improve performance in ways that minimize both additional power usage and design complexity. The market for microprocessors has become stratified into areas with different performance requirements, so it is useful to examine the problem from the point of view of these different performance requirements.

# The Future of Microprocessors

#### THROUGHPUT PERFORMANCE IMPROVEMENT

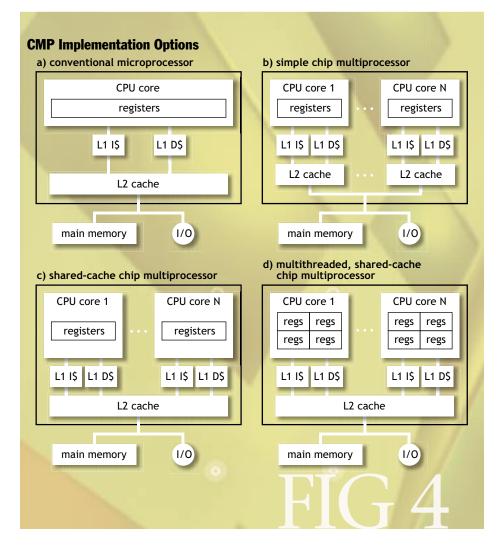

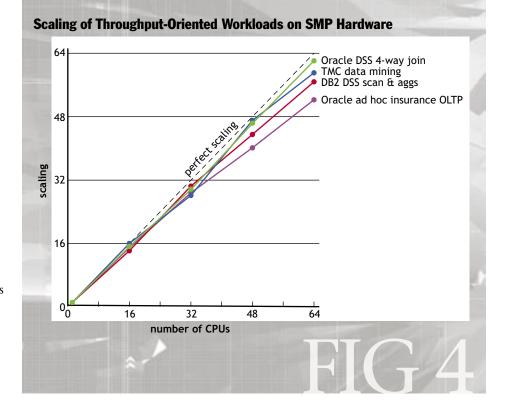

With the rise of the Internet, the need for servers capable of handling a multitude of independent requests arriving rapidly over the network has increased dramatically. Since individual network requests are typically completely independent tasks, whether those requests are for Web pages, database access, or file service, they are typically spread across many separate computers built using highperformance conventional microprocessors (figure 4a), a technique that has been used at places like Google for years to match the overall computation throughput to the input request rate.<sup>4</sup>

As the number of requests increased over time, more servers were added to the collection. It has also been possible to replace some or all of the separate servers with multiprocessors. Most existing multiprocessors consist of two or more separate processors connected using a common bus, switch hub, or network to shared memory and I/O devices. The overall system can usually be physisolutions, such as blade servers and switching to multiprocessors that can share components. Some power reduction has also occurred through the sharing of more power-hungry components in these systems. These shortterm solutions are reaching their practical limits, however, as systems are reaching the maximum component density that can still be effectively air-cooled. As a result, the next stage of development for these systems involves a new step: the CMP (chip multiprocessor).<sup>5</sup>

The first CMPs targeted toward the server market implement two or more conventional superscalar processors together on a single die.<sup>6,7,8,9</sup> The primary motivation for this is reduced volume-multiple processors can now fit in the space where formerly only one could, so overall performance per unit volume can be increased. Some savings in power also occurs because all of the processors on a single die can share a single connection to the rest of the system, reducing the amount of high-speed communication infrastructure required, in addition to the sharing possible with a conventional multiprocessor. Some CMPs, such as the first ones announced from AMD and Intel, share only the system interface between processor cores (illustrated in figure 4b), but others share one or more levels of on-chip cache (figure 4c), which allows interprocessor communication between the CMP cores without off-chip accesses.

Further savings in power can be achieved by taking advantage of the fact that while server workloads require high throughput, the *latency* of each request is generally

cally smaller and use less power than an equivalent set of uniprocessor systems because physically large components such as memory, hard drives, and power supplies can be shared by some or all of the processors.

Pressure has increased over time to achieve more performance per unit volume of data-center space and per watt, since data centers have finite room for servers and their electric bills can be staggering. In response, the server manufacturers have tried to save space by adopting denser server packaging

rants: feedback@acmqueue.com

not as critical.<sup>10</sup> Most users will not be bothered if their Web pages take a fraction of a second longer to load, but they will complain if the Web site drops page requests because it does not have enough throughput capacity. A CMP-based system can be designed to take advantage of this situation.

When a two-way CMP replaces a uniprocessor, it is possible to achieve essentially the same or better throughput on server-oriented workloads with just *half* of the original clock speed. Each request may take up to twice as long to process because of the reduced clock rate. With many of these applications, however, the slowdown will be much less, because request processing time is more often limited by memory or disk performance than by processor performance. Since two requests can now be processed simultaneously, however, the overall throughput will now be the same or better, unless there is serious contention for the same memory or disk resources. Overall, even though performance is the same or only a little better, this adjustment is still advantageous at the system level. The lower clock rate allows us to design the system with a significantly lower power supply voltage, often a nearly linear reduction. Since power is proportional to the *square* of the voltage, however, the power required to obtain the original performance is much lower—usually about half (half of the voltage squared = a quarter of the power, per processor, so the power required for both processors together is about half), although the potential savings could be limited by static power dissipation and any minimum voltage levels required by the underlying transistors.

For throughput-oriented workloads, even more power/ performance and performance/chip area can be achieved by taking the "latency is unimportant" idea to its extreme and building the CMP with many small cores instead of a few large ones. Because typical server workloads have very

low amounts of instruction-level parallelism and many memory stalls, most of the hardware associated with superscalar instruction issue is essentially wasted for these applications. A typical server will have tens or hundreds of requests in flight at once, however, so there is enough work available to keep many processors busy simultaneously.

Therefore, replacing each large, superscalar processor in a CMP with several small ones, as has been demonstrated successfully with the Sun Niagara,11 is a winning policy. Each small processor will process its request more slowly than a larger, superscalar processor, but this latency slowdown is more than compensated for by the fact that the same chip area can be occupied by a much larger number of processors-about four times as many, in the case

# The Future of **Microprocessors**

of Niagara, which has eight single-issue SPARC processor cores in a technology that can hold only a pair of super-scalar UltraSPARC cores.

Taking this idea one step further, still more latency can be traded for higher throughput with the inclusion of multithreading logic within each of the cores.<sup>12,13,14</sup> Because each core tends to spend a fair amount of time waiting for memory requests to be satisfied, it makes sense to assign each core several threads by including multiple register files, one per thread, within each core (figure 4d). While some of the threads are waiting for memory to respond, the processor may still execute instructions from the others.

Larger numbers of threads can also allow each processor to send more requests off to memory in parallel, increasing the utilization of the highly pipelined memory systems on today's processors. Overall, threads will typically have a slightly longer latency, because there are times when all are active and competing for the use of the processor core. The gain from performing computation during memory stalls and the ability to launch numerous memory accesses simultaneously more than compensates for this longer latency on systems such as Niagara, which has four threads per processor or 32 for the entire chip, and Pentium chips with Intel's Hyperthreading, which allows two threads to share a Pentium 4 core.

#### LATENCY PERFORMANCE IMPROVEMENT

The performance of many important applications is measured in terms of the execution latency of individual tasks instead of high overall throughput of many essentially unrelated tasks. Most desktop processor applications still fall in this category, as users are generally more concerned with their computers responding to their commands as quickly as possible than they are with their computers' ability to handle many commands simultaneously, although this situation is changing slowly over time as more applications are written to include many "background" tasks. Users of many other computation-bound applications, such as most simulations and compilations, are typically also more interested in how long the programs take to execute than in executing many in parallel.

Multiprocessors can speed up these types of applications, but it requires effort on the part of programmers to break up each long-latency thread of execution into a large number of smaller threads that can be executed on many processors in parallel, since automatic parallelization technology has typically functioned only on Fortran programs describing dense-matrix numerical computations. Historically, communication between processors was generally slow in relation to the speed of individual processors, so it was critical for programmers to ensure that threads running on separate processors required only minimal communication with each other.

Because communication reduction is often difficult, only a small minority of users bothered to invest the time and effort required to parallelize their programs in a way that could achieve speedup, so these techniques were taught only in advanced, graduate-level computer science courses. Instead, in most cases programmers found that it was just easier to wait for the next generation of uniprocessors to appear and speed up their applications for "free" instead of investing the effort required to parallelize their programs. As a result, multiprocessors had a hard time competing against uniprocessors except in very large systems, where the target performance simply exceeded the power of the fastest uniprocessors available.

With the exhaustion of essentially all performance gains that can be achieved for "free" with technologies such as superscalar dispatch and pipelining, we are now entering an era where programmers *must* switch to more parallel programming models in order to exploit multiprocessors effectively, if they desire improved single-program performance. This is because there are only three real "dimensions" to processor performance increases beyond Moore's law: clock frequency, superscalar instruction issue, and multiprocessing. We have pushed the first two to their logical limits and must now embrace multiprocessing, even if it means that programmers will be forced to change to a parallel programming model to achieve the highest possible performance.

Conveniently, the transition from multiple-chip systems to chip multiprocessors greatly simplifies the problems traditionally associated with parallel programming. Previously it was necessary to minimize communication between independent threads to an extremely low level, because each communication could require hundreds or even thousands of processor cycles. Within any CMP with a shared on-chip cache memory, however, each communication event typically takes just a handful of processor cycles. With latencies like these, communication delays have a much smaller impact on overall system performance. Programmers must still divide their work into parallel threads, but do not need to worry nearly as much about ensuring that these threads are highly independent, since communication is relatively cheap. This is not a complete panacea, however, because programmers must still structure their inter-thread synchronization correctly, or the program may generate incorrect results or deadlock, but at least the performance impact of communication delays is minimized.

Parallel threads can also be much smaller and still be effective-threads that are only hundreds or a few thousand cycles long can often be used to extract parallelism with these systems, instead of the millions of cycles long threads typically necessary with conventional parallel machines. Researchers have shown that parallelization of applications can be made even easier with several schemes involving the addition of transactional hardware to a CMP.<sup>15,16,17,18,19</sup> These systems add buffering logic that lets threads attempt to execute in parallel, and then dynamically determines whether they are actually parallel at runtime. If no inter-thread dependencies are detected at runtime, then the threads complete normally. If dependencies exist, then the buffers of some threads are cleared and those threads are restarted, dynamically serializing the threads in the process.

Such hardware, which is only practical on tightly coupled parallel machines such as CMPs, eliminates the need for programmers to determine whether threads are parallel as they parallelize their programs—they need only choose *potentially* parallel threads. Overall, the shift from conventional processors to CMPs should be less traumatic for programmers than the shift from conventional processors to multichip multiprocessors, because of the short CMP communication latencies and enhancements such as transactional memory, which should be commercially available within the next few years. As a result, this paradigm shift should be within the range of what is feasible for "typical" programmers, instead of being limited to graduate-level computer science topics.

#### HARDWARE ADVANTAGES

In addition to the software advantages now and in the future, CMPs have major advantages over conventional uniprocessors for hardware designers. CMPs require only a fairly modest engineering effort for each generation of processors. Each member of a family of processors just requires the stamping down of additional copies of the core processor and then making some modifications to relatively slow logic connecting the processors together to accommodate the additional processors in each generation—and *not* a complete redesign of the high-speed processor core logic. Moreover, the system board design typically needs only minor tweaks from generation to generation, since externally a CMP looks essentially the same from generation to generation, even as the number of processors within it increases.

The only real difference is that the board will need to deal with higher I/O bandwidth requirements as the CMPs scale. Over several silicon process generations, the savings in engineering costs can be significant, because it is relatively easy to stamp down a few more cores each time. Also, the same engineering effort can be amortized across a large family of related processors. Simply varying the numbers *and* clock frequencies of processors can allow essentially the same hardware to function at many different price/performance points.

#### AN INEVITABLE TRANSITION