#### ON HETEROGENEOUS COMPUTE AND MEMORY SYSTEMS

by

Jason Lowe-Power

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN-MADISON

2017

Date of final oral examination: 05/31/2017

The dissertation is approved by the following members of the Final Oral Committee:

Mark D. Hill

Dan Negrut

Jignesh M. Patel

Karthikeyan Sankaralingam

David A. Wood

# ACKNOWLEDGMENTS

I would like to acknowledge all of the people who helped me along the way to completing this dissertation. First, I would like to thank my advisors, Mark Hill and David Wood. Often, when students have multiple advisors they find there is high "synchronization overhead" between the advisors. However, Mark and David complement each other well. Mark is a high-level thinker, focusing on the structure of the argument and distilling ideas to their essentials; David loves diving into the details of microarchitectural mechanisms. Although ever busy, at least one of Mark or David were available to meet with me, and they always took the time to help when I needed it. Together, Mark and David taught me how to be a researcher, and they have given me a great foundation to build my career.

I thank my committee members. Jignesh Patel for his collaborations, and for the fact that each time I walked out of his office after talking to him, I felt a unique excitement about my research. Karu Sakaralingam for many spirited discussions. Our differing viewpoints always give me something to think about. And Dan Negrut for stepping out of his comfort zone to learn about computer architecture and for teaching me about ways to use hardware for truly useful computations.

I also want to thank a number of my close friends and colleagues who have helped me along the way. Marc Orr began grad school with me, and was an incredibly supportive friend and collaborator throughout our time at Wisconsin. Without Marc suggesting that

we apply for the Summer RA program after our first year, I doubt I would be writing this thesis. Lena Olson was very supportive and always up for a distracting conversation when research wasn't going the way I wanted it to. Somehow, out of all of these distracting conversations, a fruitful collaboration was born. Lena showed me how working with collaborators can have a big impact. Similarly, I also gained a lot from my collaboration with Hongil Yoon. Hongil was a great collaborator, always pushing back when I was wrong.

I would also like to thank the Multifacet group members and other computer architecture students at Wisconsin not already mentioned for their support, mentorship, and encouragement over the years. Specifically my office mates at various times, Somayeh Sardashti and Swapnil Haria provided me with a sounding board for ideas and needed distractions.

Finally, I would like to thank my family for their ever-present encouragement. To my parents, Rena and Greg Power, thank you for sparking my interest in research at a young age and your continued to encouragement and support. To my sister, Marissa Power, thank you for supporting me over the years. And, of course, I deeply thank my partner, Tiffany Lowe-Power. Without your encouragement I would not have been as successful throughout grad school (and life).

# **CONTENTS**

| Co  | nten    | ts                                             | iv  |

|-----|---------|------------------------------------------------|-----|

| Lis | st of T | Tables                                         | iii |

| Lis | st of l | Figures                                        | х   |

| Ał  | ostrac  | :t                                             | xii |

| 1   | Intro   | oduction                                       | 1   |

|     | 1.1     | Trends in computing                            | 1   |

|     | 1.2     | Contributions                                  | 2   |

|     | 1.3     | Thesis organization                            | 6   |

| 2   | GPU     | J Background                                   | 7   |

|     | 2.1     | GPU architecture                               | 7   |

|     | 2.2     | GPGPU systems                                  | 10  |

|     | 2.3     | GPGPU programming models                       | 11  |

| 3   | Sim     | ulation Methodology                            | 14  |

|     | 3.1     | gem5-gpu: A heterogeneous CPU-GPU simulator    | 14  |

|     | 3.2     | Sampling methodology for native-size workloads | 22  |

| 4 | Tigh | ntly-integrated GPGPU Address Translation                              | 26   |

|---|------|------------------------------------------------------------------------|------|

|   | 4.1  | Introduction                                                           | 26   |

|   | 4.2  | Background                                                             | 29   |

|   | 4.3  | Simulation methodology and workloads                                   | 32   |

|   | 4.4  | Designing a GPU MMU through analysis                                   | 33   |

|   | 4.5  | Correctness issues                                                     | 43   |

|   | 4.6  | Alternative designs                                                    | 48   |

|   | 4.7  | Related work                                                           | 52   |

|   | 4.8  | Conclusions                                                            | 54   |

|   | 4.9  | Artifacts                                                              | 54   |

| 5 | Hig  | h Performance Analytic Databases on Tightly-integrated GPGPU Archi     | tec- |

|   | ture | s                                                                      | 56   |

|   | 5.1  | Introduction                                                           | 56   |

|   | 5.2  | Implementation                                                         | 59   |

|   | 5.3  | Methodology                                                            | 65   |

|   | 5.4  | Results                                                                | 66   |

|   | 5.5  | Related work                                                           | 73   |

|   | 5.6  | Conclusions                                                            | 75   |

| 6 | Imp  | lications of 3D Die-Stacked Memory for Bandwidth-Constrained Workloads | s 77 |

|   | 6.1  | Introduction                                                           | 77   |

|   | 6.2  | Case study with database scan                                          | 82   |

|   | 6.3  | Potential big data machine designs                                     | 84   |

|   | 6.4  | Methodology: Simple analytical model                                   | 87   |

|   | 6.5  | Results                                                                | 89   |

|   | 6.6  | Discussion                                                             | 98   |

|   | 6.7  | Conclusions                                                            | 101  |

|     | 6.8   | Artifacts                                                         | 101 |

|-----|-------|-------------------------------------------------------------------|-----|

| 7   | Ada   | ptive Victim DRAM Cache: Optimizing Bandwidth for HPC Workloads 1 | 103 |

|     | 7.1   | Introduction                                                      | 103 |

|     | 7.2   | DRAM cache design and access amplification                        | 108 |

|     | 7.3   | Using the access amplification model                              | 112 |

|     | 7.4   | Adaptive victim cache                                             | 114 |

|     | 7.5   | Evaluation                                                        | 127 |

|     | 7.6   | Related work                                                      | 139 |

|     | 7.7   | Conclusions                                                       | 141 |

|     | 7.8   | Artifacts                                                         | 141 |

| 8   | Con   | clusions and Future Work                                          | 142 |

| Bil | bliog | raphy                                                             | 147 |

# LIST OF TABLES

| 4.1 | Details of simulation parameters                    |

|-----|-----------------------------------------------------|

| 4.2 | Configurations under study                          |

| 5.1 | Details of hardware architectures evaluated         |

| 6.1 | Inputs for the analytical model                     |

| 6.2 | Cluster requirements                                |

| 7.1 | Details of the KNL-like DRAM cache operation        |

| 7.2 | Access amplification for each design                |

| 7.3 | Details of bandwidth optimized DRAM cache functions |

| 7.4 | Explanation of rows in Table 7.3                    |

| 7.5 | NPB workload characteristics                        |

| 7.6 | Simulated system details                            |

# List of Figures

| 2.1  | Contemporary discrete GPGPU architecture                               | 9  |

|------|------------------------------------------------------------------------|----|

| 2.2  | Overview of a modern heterogeneous system                              | 10 |

| 3.1  | Overview of <i>gem5-gpu</i> architecture with an example configuration | 18 |

| 4.1  | Example GPGPU application                                              | 31 |

| 4.2  | Memory operations                                                      | 35 |

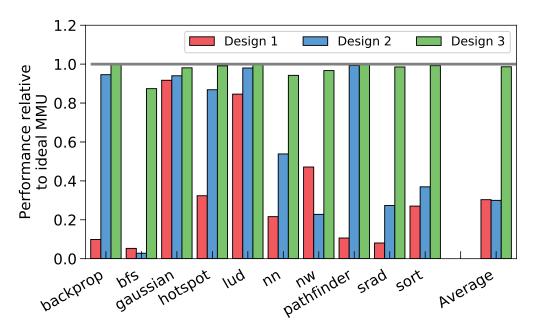

| 4.3  | Performance of GPU MMU                                                 | 36 |

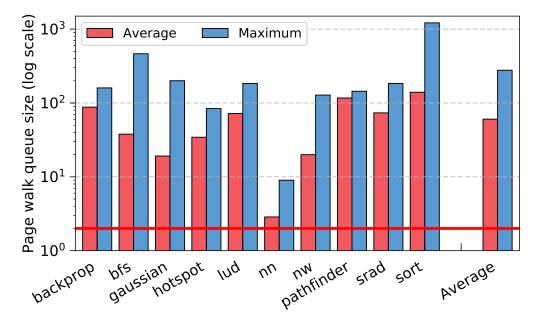

| 4.4  | Page walk queue size                                                   | 36 |

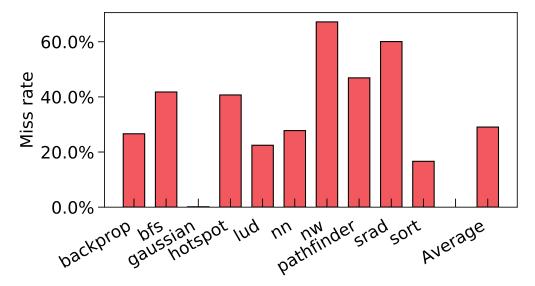

| 4.5  | GPU L1 TLB miss rate                                                   | 39 |

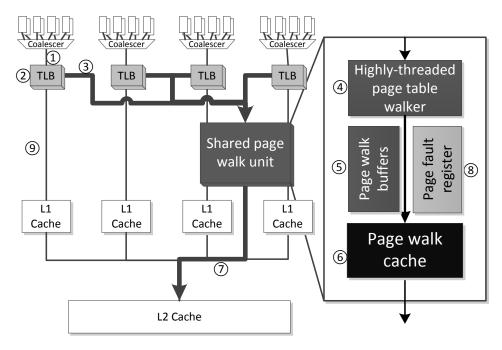

| 4.6  | Overview of the GPU MMU designs                                        | 41 |

| 4.7  | Details of the highly-threaded page table walker                       | 42 |

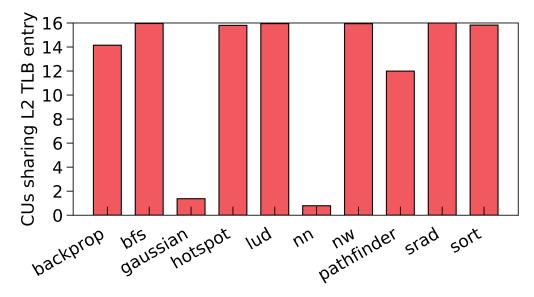

| 4.8  | Sharing pattern for L2 TLB                                             | 47 |

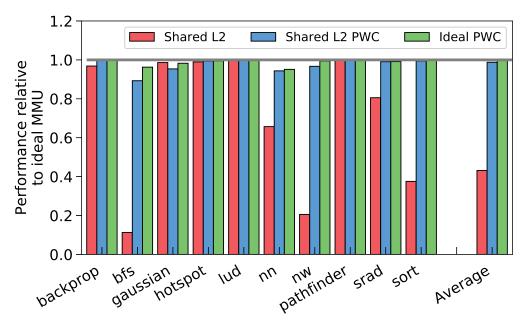

| 4.9  | Performance of alternative designs                                     | 47 |

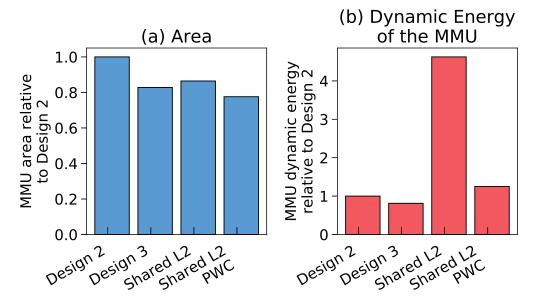

| 4.10 | Energy and area of MMU configurations                                  | 51 |

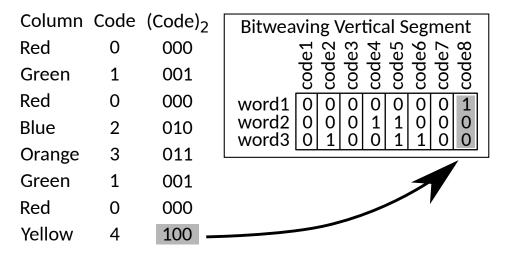

| 5.1  | Overview of BitWeaving's memory layout                                 | 59 |

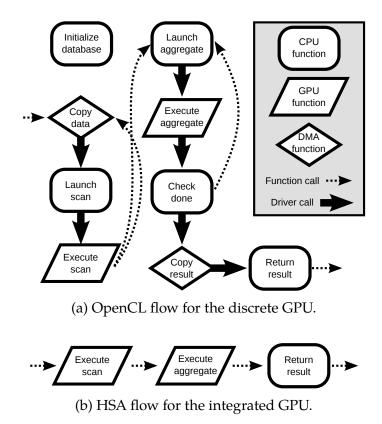

| 5.2  | Flowchart showing the CPU-GPU interaction                              | 60 |

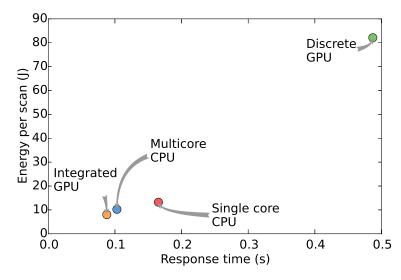

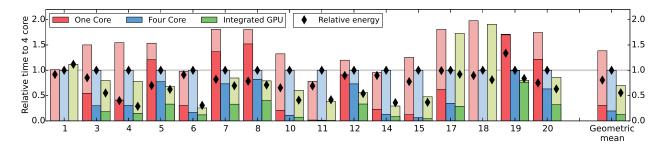

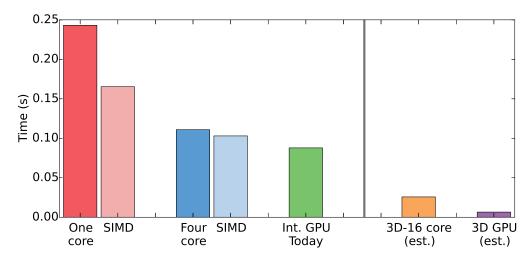

| 5.3  | Performance and energy of scan microbenchmark                          | 66 |

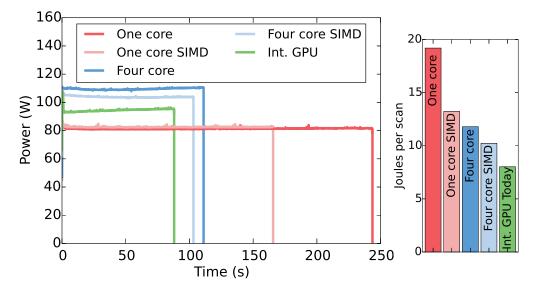

| 5.4  | Power for 1000 scans and energy per scan                               | 67 |

| 5.5  | Performance and energy for TPC-H                            |

|------|-------------------------------------------------------------|

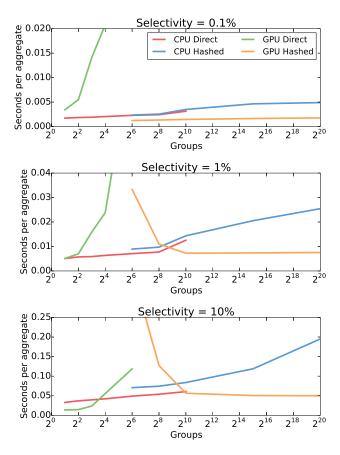

| 5.6  | Performance of aggregates                                   |

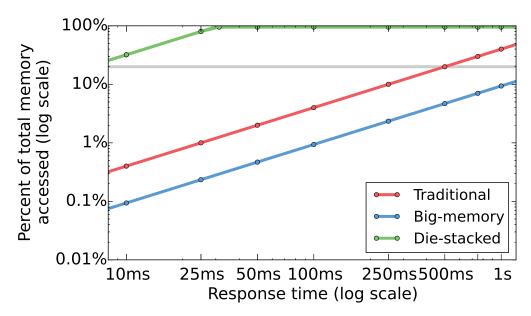

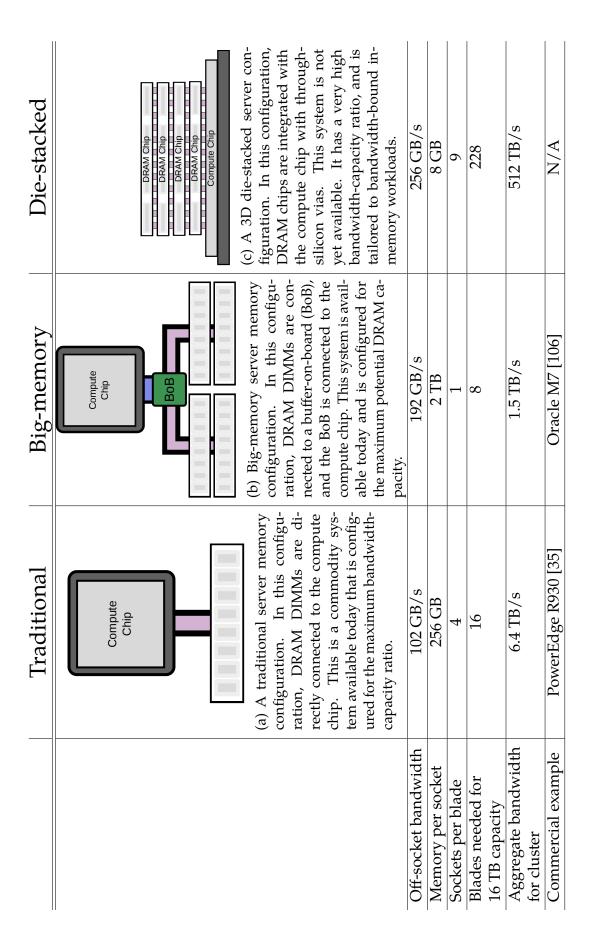

| 6.1  | Memory bandwidth-capacity tradeoff                          |

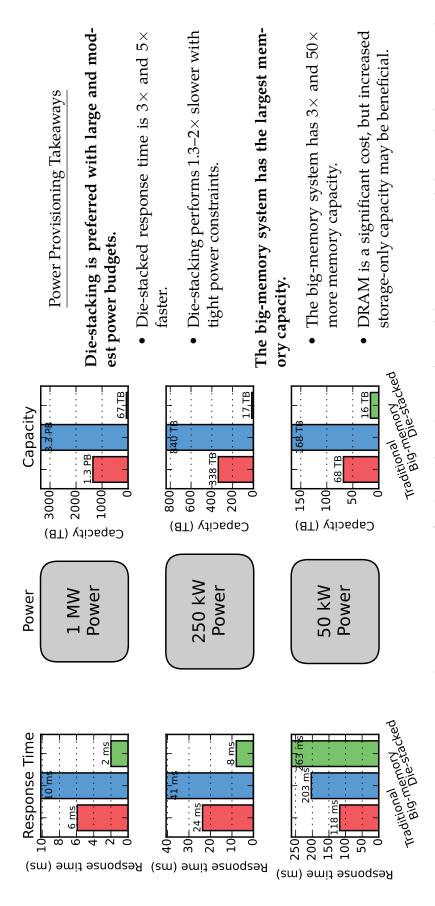

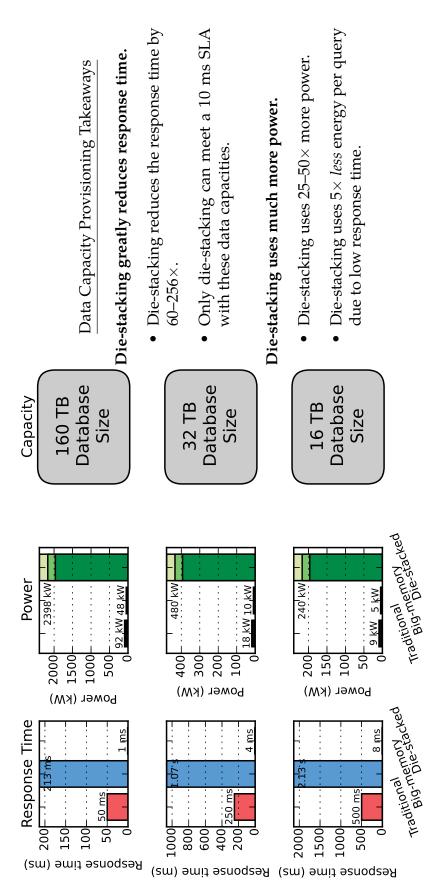

| 6.2  | System diagrams                                             |

| 6.3  | Performance of scan                                         |

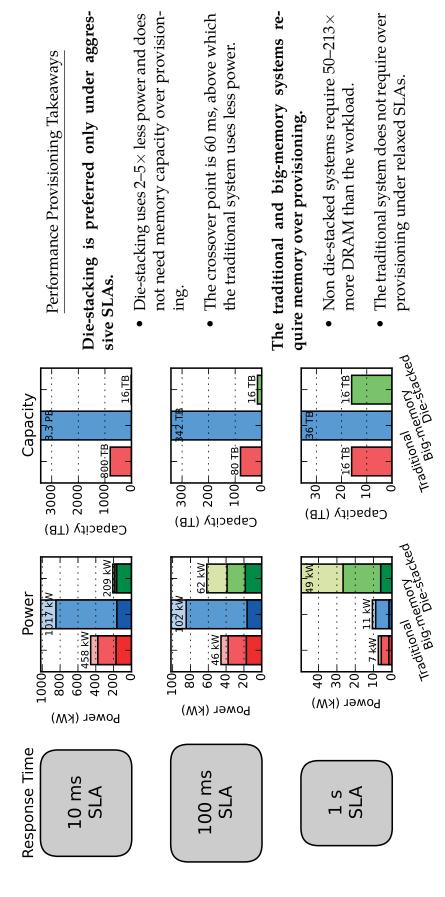

| 6.4  | Constant performance                                        |

| 6.5  | Constant power                                              |

| 6.6  | Constant capacity                                           |

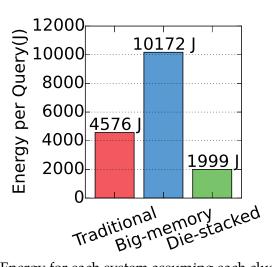

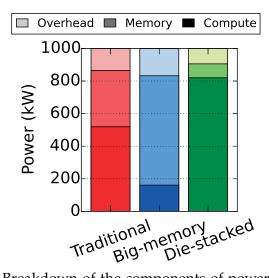

| 6.7  | Energy and power for each system                            |

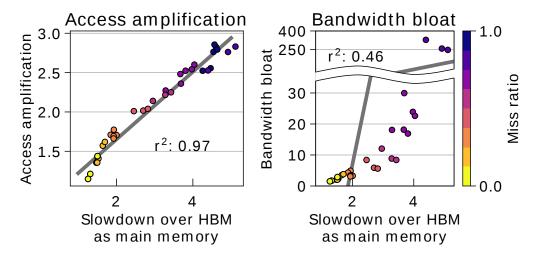

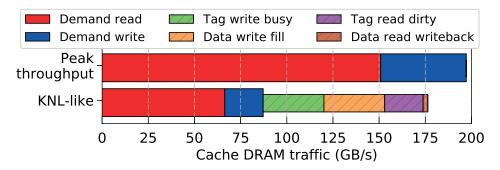

| 7.1  | Comparison of access amplification to bandwidth bloat       |

| 7.2  | Breakdown of DRAM cache traffic                             |

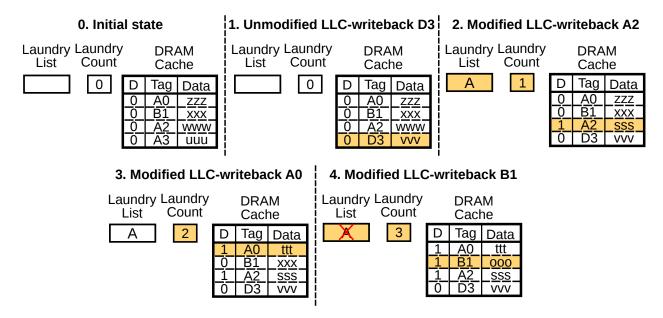

| 7.3  | Example laundry count and laundry list usage                |

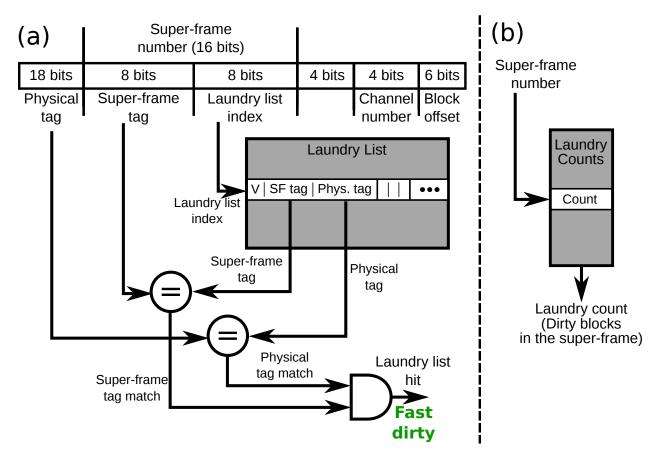

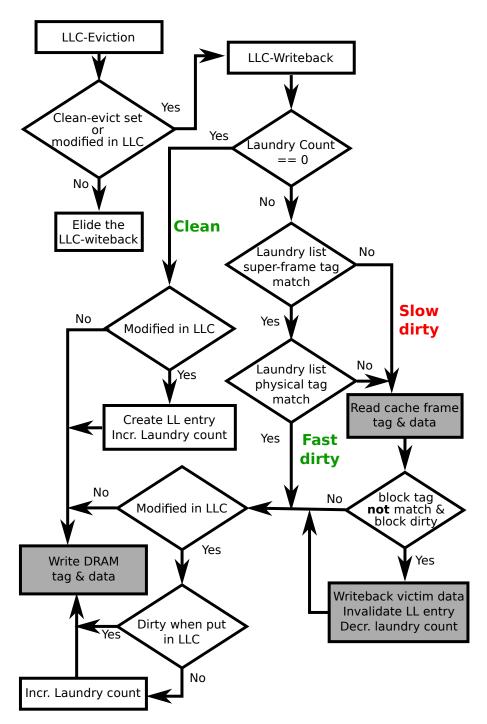

| 7.4  | Operation of the laundry list and laundry counts structures |

| 7.5  | Details of adaptive victim cache operation                  |

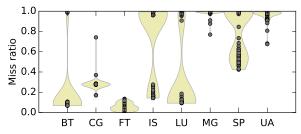

| 7.7  | Access amplification for the NPB                            |

| 7.8  | Performance of NPB                                          |

| 7.9  | Performance of different tag array sizes                    |

| 7.10 | Laundry list writes breakdown                               |

| 7.11 | Performance of DiRT                                         |

| 7.12 | Super-frames that have a single super-block cached          |

# Abstract

Computer systems are at a crossroads. Instead of counting on low-level device improvements from the semiconductor industry, processors are increasingly heterogeneous, using specialized accelerators to increase performance and energy efficiency. Simultaneously, big-data is enabling new applications that consume terabytes of data in real-time, and the Internet of things is driving new data growth by enabling developers to consume data from millions of devices and users. The increasing hardware heterogeneity driven by these technology trends puts significant burdens on the application programmers. For instance, with current interfaces, developers must manually manage all aspects of accelerator computation including explicitly moving data even when the physical memory is shared between devices.

In this thesis, we increase the logical integration of physically integrated on-chip accelerators by extending conventional CPU properties to accelerators. We specifically target on-die graphics processing units (GPUs) which are found on most products from AMD, Intel, and mobile systems and are increasingly used for general-purpose computation. Logical integration between the CPU and GPU simplifies programming these heterogeneous devices. We leverage the logically integrated systems enabled by this research to improve the performance of big-data applications. We show that using integrated GPUs for analytic database workloads can increase performance and decrease energy consumption.

We also evaluate the efficacy of designing systems with heterogeneous memory in addition to heterogeneous computational units. We show that including high-bandwidth 3D-stacked DRAM can significantly improve the performance and reduce the energy consumed for analytic database workloads and other bandwidth-constrained workloads. Finally, we propose a new metric, access amplification, to help system designers reason about the best policies for using heterogeneous memory as a hardware-managed cache. Using access amplification, we design an adaptive victim cache policy which increases the performance of a DRAM cache compared to current designs.

#

# Introduction

# 1.1 Trends in computing

There are two conflicting trends in computing today. First, due to the slowdown of Moore's Law and the end of Dennard scaling, general purpose-processors' steady improvements are waning. We can no longer expect general applications to significantly improve performance every processor generation. Using ITRS projections, Esmaeilzadeh et al. found that by 2024 we can only expect a  $7.9\times$  average speedup compared to today's processors from traditional architectural optimizations, more than  $24\times$  less than if performance had continued to follow Moore's law [36]. This result is mainly due to chip power constraints; thus, continuing to increasing compute capability requires more efficient architectural designs.

Second, new data is generated at an alarming rate: as much as 2.6 exabytes are created each day [89]. For instance, with the growth of internet-connected devices, there is an explosion of data from sensors on these devices. The ability to analyze this data is important to many different industries from automotive to health care [105]. Users want to run complex queries on this abundance of data, sometimes with real-time response latency constraints. These trends of increasing data, increasing computational complexity, and increasing performance constraints put a great strain on our computational systems,

especially under a fixed power budget.

Systems are becoming more heterogeneous to rectify these trends. Heterogeneity improves the performance and decreases the energy consumed for applications by *specializing* the hardware for a single application or a class of applications. While fully general-purpose processors' improvements are slowing, there is a large space for the specialized processor ecosystem to grow and become more efficient.

One current economically viable example of specialization is graphics processing units, or GPUs. Heterogeneous systems with GPUs began by including GPUs as an I/O device to drive the graphics display, but these devices have recently become more tightly integrated. Today, 99% of Intel's and 67% of AMD's desktop CPUs ship with an on-die GPU [109], and server chips with integrated GPUs have been announced [4].

Heterogeneity is not limited to computational specialization. Recently, systems have integrated multiple different memory technologies such as DRAM DIMMs and 3D-stacked memory [140]. This allows these systems to have memory optimized for capacity (DRAM DIMMs) and memory optimized for performance (high-bandwidth 3D-die stacked memory). With emerging memory technology [8, 59, 80], memory heterogeneity is likely to become more common.

### 1.2 Contributions

This thesis makes four contributions to optimizing and using heterogeneous systems.

#### Contribution 1: Simplifying integrated GPGPU programming

The increasing hardware heterogeneity driven by the technology trends discussed above puts significant burdens on the application programmers. With current interfaces, developers must manually manage all aspects of accelerator computation. For instance,

programmers must explicitly move data from CPU to GPU memory, even if the physical memory is shared because each device has a logically separate address space.

Coherent data access and a consistent address space simplify the programmer's interface to tightly-integrated accelerators. Parallel hardware has been ubiquitous for at least the last 15 years, and while programming parallel machines is still difficult, it is simplified by two important properties: coherent data access so when developers access a memory location it will hold the most up-to-date data and a consistent address space so programmers can use the same data structures on any processor in the system. The cache coherence hardware and the virtual memory management unit provide these properties on current CPU systems. Without coherent data access and a consistent address space, programmers manually transform and move data between the CPU and other accelerators. Our previous work provides cache coherence to integrated CPU-GPU systems [114].

In Chapter 4 we show how to provide CPU-style address translation to integrated GPUs. Conventional CPU address translation mechanisms applied directly to the GPU result in a 4× performance degradation due to queuing delays at the centralized address translation hardware. However, we show how to gain the performance back by parallelizing address translation and judiciously using CPU-centric memory management unit optimizations. These techniques logically unify the physically integrated GPU and pave the way for programmers to use the integrated GPU as just another CPU core.

This chapter was originally published as "Supporting x86-64 Address Translation for 100s of GPU Lanes" in *The 20th IEEE International Symposium On High Performance Computer Architecture (HPCA)*, 2014 [116].

#### Contribution 2: Case study using tightly-integrate GPGPUs

The logical integration of GPUs with the rest of the system enables new application domains to take advantage of the GPU. Previous work has shown GPUs can provide up to  $100 \times$  performance improvement, but these results are limited to relatively small problems (e.g.,

a working set of less than 8 GB). Chapter 4 and Heterogeneous System Coherence [114] enables the GPU to access the hundreds of gigabytes of system memory and significantly reduces the overheads of conventional GPU programming expanding the scope of applications that can leverage this accelerator.

In this thesis, we specifically apply these techniques to analytic databases as a case study. Analytic queries are growing in complexity, and their response time requirements are shrinking. Service providers want to analyze terabytes of data in milliseconds to provide their users with pertinent information (e.g., serving ads, suggesting purchases, and search results). To provide low latency, much of the data is stored in memory, not on disk.

Previous research had shown the significant potential of discrete GPUs; however, due to data movement costs, this potential had not been realized. In Chapter 5, we develop new algorithms to take advantage of physically and logically integrated GPUs. These new scan and aggregate algorithms are  $3\times$  faster than traditional GPU algorithms and use 30% less energy than a CPU-only system.

This chapter was published as "Toward GPUs being mainstream in analytic processing: An initial argument using simple scan-aggregate queries" in *The Proceedings of the 11th International Workshop on Data Management on New Hardware (DaMoN'15)*, 2015 [118].

#### Contribution 3: Exploring 3D-stacked DRAM for

#### bandwidth-constrained workloads

Exploiting high bandwidth to memory is one of GPUs' biggest benefits over CPU architecture. Thus, tightly-integrating GPUs onto the same die as the CPU significantly increases the bandwidth demand of the chip making more applications memory-bandwidth constrained.

3D die stacking can help mitigate this bandwidth wall [20]. With 3D die stacking, multiple silicon dies are stacked on top of one another. 3D die-stacking enables very high-bandwidth memory systems, up to 1 TB/s in some projections [2], and decreases the

energy for communication by a factor of  $3 \times [20]$ .

In Chapter 6, we show integrating 3D die-stacked DRAM into analytic database appliances coupled with the algorithms from Chapter 5 can improve performance by  $15\times$ . Further, we conduct a limit study showing these 3D die stacked systems provide the best power-performance tradeoff when the latency of big-data analytic workloads is paramount  $(2-5\times$  less power to meet a 10 ms response latency guarantee).

This chapter was published as "When to use 3D Die-Stacked Memory for Bandwidth-Constrained Big Data Workloads" in *The Seventh Workshop on Big Data Benchmarks, Performance Optimization, and Emerging Hardware (BPOE 7)*, 2016 [88], and integrates a case study from the publication "Implications of Emerging 3D GPU Architecture on the Scan Primitive" in *ACM SIGMOD Record* 2015 [117].

# Contribution 4: Decreasing bandwidth overheads in a heterogeneous memory system

While integrating high-bandwidth 3D die-stacked memory (HBM) can provide significant performance improvements by mitigating the off-chip bandwidth bottleneck, its capacity is limited. Therefore, systems with 3D die stacked memory will likely additionally have conventional off-chip DRAM DIMMs for their increased capacity. In a heterogeneous memory system, using HBM as a DRAM cache of off-chip RAM provides transparency to programmers. However, we show in Chapter 7 that treating HBM as a cache wastes its bandwidth because of *access amplification*. Access amplification quantifies the non-demand accesses that waste the HBM bandwidth. We show there are on average two accesses per DRAM cache request when evaluating a current production DRAM cache [140].

We propose an adaptive victim DRAM cache design that avoids access amplification by adaptively shifting between a writethrough and a write-back caching policy. Our adaptive victim cache strives to read metadata only while reading data and to write metadata only while writing data. This design performs robustly better than a current DRAM cache

design under a wide range of memory access patterns including high miss rates and high write traffic.

This chapter is currently under review for publication.

#### Other contributions: Simulation infrastructure

Another contribution of this thesis is new simulation infrastructure which enabled the above contributions. We developed gem5-gpu [115], described in Section 3.1, to simulate heterogeneous CPU-GPU platforms that did not physically exist at the time. Additionally, in Chapter 7, we focus on large high-performance computing workloads that are infeasible to simulate using conventional techniques. Therefore, we developed a sampling methodology combining previous work into a more easily usable system. We describe this methodology in detail in Section 3.2.

The work on gem5-gpu was publish as "gem5-gpu: A Heterogeneous CPU-GPU Simulator" in *IEEE Computer Architecture Letters*, 2015 [115].

# 1.3 Thesis organization

This thesis is organized as follows. Chapter 2 discuses GPU architecture and GPU programming models used in Chapters 4 and 5. Chapter 3 describes the simulation methodology used in Chapters 4 and 7. Chapter 4 presents the design and evaluation of a memory management unit for integrated GPUs. Chapter 5 develops and evaluates new algorithms for database scan and aggregate for tightly-integrated GPUs. Chapter 6 explores system design for bandwidth-constrained workloads evaluating the tradeoffs between 3D stacked DRAM and conventional DRAM DIMMs. Chapter 7 evaluates DRAM cache designs and proposes a new DRAM cache policy to decrease bandwidth waste. Finally, Chapter 8 summarizes our work and outlines future research directions.

# \_\_2\_

# GPU BACKGROUND

In this thesis, we augment the GPU architecture in Chapter 4 and leverage the GPU microarchitecture in Chapters 5 and 6. This chapter provides details on the GPU's microarchitecture and programming models used in this thesis.

#### 2.1 GPU architecture

Graphic processing units (GPUs) were originally created to accelerate rendering graphics to the screen; however, in recent years they have become general purpose compute platforms [107]. These general-purpose GPUs (GPGPUs) have a number of characteristics that differ from conventional CPUs:

- GPGPUs are optimized for instruction throughput, not instruction latency.

- GPGPUs can exhibit much higher memory-level parallelism than CPUs.

- GPGPUs have high-bandwidth and low-capacity on-chip caches.

- GPGPUs devote a higher percentage of area to compute functional units than CPUs.

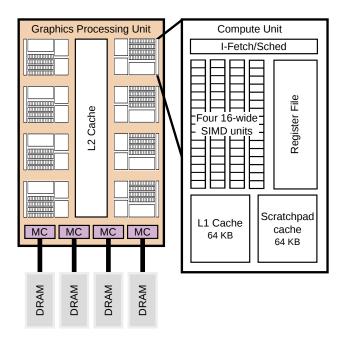

Modern GPUs are high-throughput devices. A GPU is made up of a set of *compute units* (CUs, SMs in NVIDIA terminology). Each CU contains many processing elements, organized into four 16-wide *SIMD units* in AMD graphics core next (GCN) architecture [7] Each CU has a scheduler that schedules instructions onto the SIMD units. Each SIMD unit of the CU has a set of *SIMD lanes* which execute the same instruction each cycle in lock step (similar to SIMD execution units in CPUs) [78]. NVIDIA GPU architectures are similar with 16–192 SPs which execute in lock step [98]. Figure 2.1 shows an overview of GPU hardware.

GPUs provide the potential for much higher parallelism than CPUs. With well structured code, all of the SIMD lanes on the GPU can simultaneously execute instructions. Similar to some CPU architectures, GPUs leverage multithreading to increase memory-level parallelism. However, where CPU cores typically support two–eight hardware contexts, GPU CUs can support 40 or more hardware contexts. Also, by leveraging multithreading, the GPU can take advantage of high memory-level parallelism. High memory-level parallelism allows the GPU to effectively utilize high memory bandwidth and tolerate high memory latencies.

To support this high memory-level parallelism, the memory system and caches of GPUs are optimized for throughput, not latency. GPU architectures provide a much larger register file than CPUs to support the many execution contexts. GPUs typically have a 16–64 KB L1 cache per CU and a shared 1–2 MB L2 cache [7]. The general-purpose caches of GPUs are much smaller than the caches on multicore CPUs, especially when considering the capacity per-thread. Large caches are less useful for highly data-parallel applications because they often exhibit poor temporal locality.

In addition to these features, each CU of the GPU also contains two special memory system optimizations. First, between the SIMD lanes and the L1 data cache is a *coalescing unit* that takes the memory addresses generated by each of the SIMD lanes and attempts to coalesce them into the minimum number of memory references (e.g., if all 64 address

Figure 2.1: Contemporary discrete GPGPU architecture. CU microarchitecture is the same for the integrated GPU.

are consecutive and aligned the coalescer will generate four 64-byte requests instead of 64 4-byte requests). Application performance depends on good coalescing behavior, especially for memory-bound workloads.

The second GPU-specific memory optimization is the addition of a directly addressed scratchpad cache (called local memory or group memory by AMD and shared memory by NVIDIA). This small (~64 KB) cache is explicitly controlled by the programmer. Requests to the scratchpad cache do not need to access cache tags since the scratchpad is directly addressed. Memory requests to the scratchpad do not pass through the coalescer and do not access the low-bandwidth cache tags, and, therefore, the scratchpad cache is higher bandwidth than the data cache for requests that cannot be coalesced. It is common to load data into the scratchpad cache that has a poor data access pattern to avoid the high cost of uncoalesced accesses to the main memory system.

Finally, GPU architecture can be more energy efficient than CPU architecture for certain workloads (e.g. database scans). Since many SIMD lanes share a single front-end

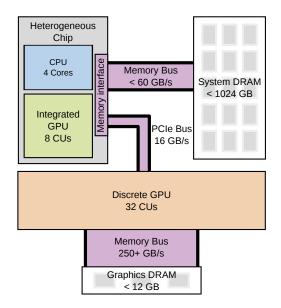

Figure 2.2: Overview of a modern heterogeneous system. Drawn comparatively to scale.

(instruction fetch, decode, etc.), this per-instruction energy overhead is amortized. On CPU architectures, the execution front-end and data movement consumes  $20\text{--}40\times$  more energy than the actual instruction [73]. Additionally, the intra-CU parallelism is explicit for GPUs through the programming model, while CPUs require high energy hardware (like the re-order buffer and parallel instruction issue) to implicitly generate instruction-level parallelism, which wastes energy for data-parallel workloads.

## 2.2 GPGPU systems

Figure 2.2 shows a system-level view of GPGPU hardware. The discrete GPU is separated from the CPU, usually by the PCI Express (PCIe) bus, and can be optionally included in the heterogeneous system. Discrete GPUs have their own physical memory, and to use the discrete GPU all data must be copied from CPU memory to device memory via the PCIe interconnect. However, the discrete GPU is capable of the highest performance between these three architectures, with more compute resources (e.g. functional units) than the CPU and much higher memory bandwidth. Unfortunately, the discrete GPU is inappropriate

for many workloads due its limited memory capacity. To use the discrete GPU with data sets larger than about 12 GB (the largest memory available for discrete GPUs today), data must be copied at execution time over the low-bandwidth PCIe bus.

Another downside of discrete GPUs are their high power consumption. Discrete GPUs often run at higher power than CPUs for two reasons. First, they have many more compute resources simultaneously active. Second, the power drawn by discrete GPUs includes the GDDR5 memory, which is both higher bandwidth than CPU DDR3 and DDR4 memory, but also higher power due to its higher bandwidth.

The integrated GPU is co-located on the same silicon chip as the CPU cores. The integrated GPU shares hardware with the CPU, including the off-chip DRAM, memory interface, and sometimes the last-level cache. The integrated GPU often has more compute resources than the multicore CPU since GPUs have smaller caches, which frees up silicon area for more functional units.

Current systems show the key differences between CPUs and GPUs well. GPUs have an order of magnitude more execution units (e.g. an AMD A10-7850 has 4 CPU cores each with 5 execution units, and an AMD HD7970 discrete GPU has 32 compute units each with 64 execution units [6]), and GPUs provide much higher memory bandwidth (e.g. an AMD A10-7850 CPU has a memory bandwidth up to 34 GB/s [5], and an AMD HD7970 GPU has a memory bandwidth of 264 GB/s [6]). Additionally, the CPU has 8–16+ MB of on-chip SRAM caches, whereas the GPU only has 2–4 MB.

# 2.3 GPGPU programming models

New GPGPU APIs (application programming interfaces) simplify programming and increase performance of GPGPU computing. Until recently, GPGPU APIs were designed for discrete GPUs. Communication between the CPU and GPU was high-overhead, and all data was explicitly declared and copied before it was used on the GPU. However, while

GPGPUs are becoming more physically integrated with CPUs, they are also becoming more logically integrated. For instance the runtime we use in Chapter 5, heterogeneous system architecture (HSA), provides a coherent and unified view of memory [127]. Other runtimes are similar (e.g., C++ AMP [94] and CUDA unified memory [101]).

HSA support is in its infancy today and is currently only supported by platforms from AMD. However, many members of the HSA foundation (http://www.hsafoundation.com/)—which includes AMD, ARM, Imagination, Qualcomm, Samsung, and others—have announced support for providing GPUs with a coherent and unified view of memory. In addition to a unified view of memory, HSA also provides a low-latency user-level API for using the GPU.

Programming the discrete GPU can be high overhead, both in terms of performance and programmability. Most discrete GPU applications follow the same general outline. First, the data must be allocated and initialized within the CPU memory space. Then, memory must be allocated on the GPU. Since the GPU has its own memory, all data that is accessed on the GPU must be copied from the CPU memory to the GPU memory. After the data has been copied to the GPU, the kernel—the code to execute on the GPU—is launched. After the kernel completes, the output data must be copied back to the CPU to continue processing the data. Each of these steps is an OpenCL API call and must interact with the operating system display driver. This interaction introduces significant performance overheads.

However, programming the integrated GPU is greatly simplified. Due to HSA, after the memory is allocated and initialized in the CPU memory space, the GPU kernel is launched as if it is a CPU function. The pointers created for the CPU can be reference from the GPU. Thus, after the kernel completes there is no need to copy data back to the CPU memory space. This unified view of memory also enables the GPU to access complicated pointer-based data structures, like hashtables. Section 5.2 discusses how this support facilitates implementing group-by operations on the integrated GPU. Figure 4.1 in Chapter 4 shows

a detailed comparison between the legacy interface, NVIDIA's unified memory, and the HSA API.

##

# SIMULATION METHODOLOGY

In this chapter, we discuss the simulation infrastructure developed to support the research objectives in this thesis. First, we detail gem5-gpu, a heterogeneous simulator built to model tightly physically and logically integrated GPUs and used in Chapter 4 to evaluate new memory management unit hardware for integrated GPUs. Then, we overview the infrastructure developed to simulate large memory bandwidth constrained high performance computing workloads used in Chapter 7 to evaluate DRAM cache policies.

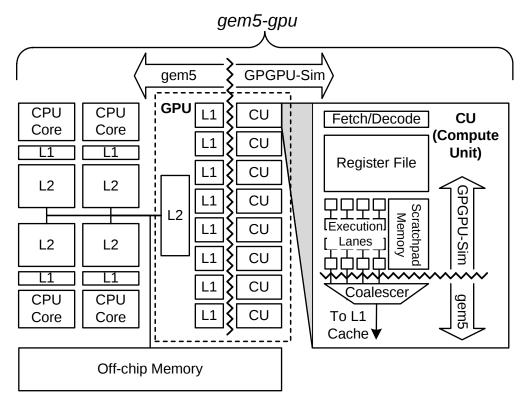

# 3.1 gem5-gpu: A heterogeneous CPU-GPU simulator

To evaluate the heterogeneous CPU-GPU system in this chapter, we developed a new simulator, gem5-gpu. We leverage two mature simulators, gem5 [19] and GPGPU-Sim [10]. gem5 is a multicore full-system simulator with multiple CPU, ISA, and memory system models. Object oriented design, flexible configuration support, and its maturity make gem5 a popular tool for investigating general purpose CPUs and multicore platforms. GPGPU-Sim is a detailed general-purpose GPU (GPGPU) simulator [10]. GPGPU-Sim models GPGPU compute units (CUs)—called streaming multiprocessors by NVIDIA—and

the GPU memory system.

To explore the heterogeneous system design space, we introduce the *gem5-gpu* simulator which combines the CU model from GPGPU-Sim and the CPU and memory system models from gem5. *gem5-gpu* builds on ideas used in related CPU-GPU simulators but makes different design choices.

*gem5-gpu* is the only simulator with all of the following advantages:

- Detailed cache coherence model,

- Full-system simulation,

- Checkpointing,

- Tightly integrated with the latest gem5 simulator, and

- Increased extensibility of GPGPU programming model and entire system architecture.

By integrating GPGPU-Sim's CU model into gem5, *gem5-gpu* can capture interactions between a CPU and a GPU in a heterogeneous processor. In particular, GPGPU-Sim CU memory accesses flow through gem5's Ruby memory system, which enables a wide array of heterogeneous cache hierarchies and coherence protocols. *gem5-gpu* also provides a tunable DMA engine to model data transfers in configurations with separate CPU and GPU physical address spaces. Through these features *gem5-gpu* can simulate both existing and future heterogeneous processors.

*gem5-gpu* is open source and available at gem5-gpu.cs.wisc.edu.

## The giant's shoulders

*gem5-gpu* builds upon prior simulation infrastructure, gem5 and GPGPU-Sim, briefly described below.

#### gem5

The gem5 simulation infrastructure (gem5.org) is a community-focused, modular, system modeling tool, developed by numerous universities and industry research labs [19]. gem5 includes multiple CPU, memory system, and ISA models. It provides two execution modes, (1) system call emulation, which can run user-level binaries using emulated system calls, and (2) full-system, which models all necessary devices to boot and run unmodified operating systems. Finally, gem5 also supports checkpointing the state of the system, which allows simulations to jump to the region of interest.

Two specific features of gem5 make it particularly well-suited for developing a heterogeneous CPU-GPU simulator. First, gem5 provides several mechanisms for modular integration of new architectural components. When new components need to communicate through the memory system, they can leverage gem5's flexible port interface for sending and receiving messages. Additionally, the gem5 EXTRAS interface can be used to specify external code that is compiled into the gem5 binary. This interface makes it simple to add and remove complex components from gem5's infrastructure.

Second, gem5 includes the detailed cache and memory simulator, Ruby. Ruby is a flexible infrastructure built on the domain specific language, SLICC, which is used to specify cache coherence protocols. Using Ruby, a developer can expressively define cache hierarchies and coherence protocols, including those expected in emerging heterogeneous processors.

#### **GPGPU-Sim**

GPGPU-Sim is a detailed GPGPU simulator (gpgpu-sim.org) backed by a strong publication record [10]. It models the compute architecture of NVIDIA Fermi graphics cards [100]. GPGPU-Sim executes applications compiled to PTX (NVIDIA's intermediate instruction set) or disassembled native GPU machine code. GPGPU-Sim models the functional and timing portions of the compute pipeline including the thread scheduling logic, highly-banked

register file, special function units, and memory system. GPGPU-Sim includes models for all types of GPU memory as well as caches and DRAM.

GPGPU applications can access a multitude of memory types. *Global memory* is the main data store where most data resides, similar to the heap in CPU applications. It is accessed with virtual addresses and is cached on chip. Other GPU-specific memory types include *constant*, used to handle GPU read-only data; *scratchpad*, a software-managed, explicitly addressed and low-latency in-core cache; *local*, mostly used for spilling registers; *parameter*, used to store compute kernel parameters; *instruction*, used to store the kernel's instructions; and *texture*, a graphics-specific, explicitly addressed cache.

GPGPU-Sim consumes mostly unmodified GPGPU source code that is linked to GPGPU-Sim's custom GPGPU runtime library. The modified runtime library intercepts all GPGPU-specific function calls and emulates their effects. When a compute kernel is launched, the GPGPU-Sim runtime library initializes the simulator and executes the kernel in timing simulation. The main simulation loop continues executing until the kernel has completed before returning control from the runtime library call. GPGPU-Sim is a functional-first simulator; it first functionally executes all instructions, then feeds them into the timing simulator.

GPGPU-Sim has some limitations when modeling heterogeneous systems:

- No host CPU timing model

- No timing model for host-device copies

- Rigid cache model

- No way to model host-device interactions

Because of these limitations, researchers interested in exploring a hybrid CPU-GPU chip as a heterogeneous compute platform cannot rely on GPGPU-Sim alone.

Figure 3.1: Overview of *gem5-gpu* architecture with an example configuration.

#### gem5-gpu Architecture

Figure 3.1 shows one example architecture *gem5-gpu* can simulate: a four core CPU and an eight CU GPU integrated on the same chip. The number of CPUs, CUs, and topology connecting them is fully configurable. Two on-chip topologies that *gem5-gpu* provides out of the box are a shared and a split memory hierarchy (i.e., integrated and discrete GPUs, respectively).

Many CUs make up the GPU, each of which has fetch/decode logic, a large register file, and many (usually 32 or 64) execution lanes. When accessing global memory, each lane sends its address to the coalescer, which merges memory accesses to the same cache block. The GPU may also contain a cache hierarchy that stores data from recent global memory accesses.

#### gem5 ←→ GPGPU-Sim interface

One of our goals is to have a clean interface between gem5 and GPGPU-Sim. Although there are many possible options, we chose the memory interface, as shown in Figure 3.1. *gem5-gpu* requires one small change to gem5: adding a single pseudo-instruction to gem5 to facilitate calls into the simulator for DMA engine and GPU functionality. *gem5-gpu* also provides two categories of GPGPU objects to gem5: wrappers for GPGPU-sim objects and new GPGPU objects. Some new GPGPU objects are a GPU load-store unit, a GPU TLB, and the DMA engine, which models DMA transfers between the CPU and the GPU.

Three major changes to GPGPU-Sim were necessary to integrate it into *gem5-gpu*. First, *gem5-gpu* routes general-purpose memory instructions—accesses to the global address space—from GPGPU-Sim to Ruby through gem5's port interface. Second, since GPGPU-Sim decouples functional execution and timing state, while gem5 is execute-at-execute, we updated GPGPU-Sim to postpone functional execution of memory instructions until they reach the execute stage of the timing pipeline. Third, to combine the cycle-driven nature of GPGPU-Sim with gem5, which is event-driven, gem5's events are used to execute each GPGPU-Sim clock cycle. This decouples the CPU from GPU, allowing it to block or continue concurrently with the GPU after a kernel launch.

#### Memory system modeling

*gem5-gpu* uses Ruby to model both the function and timing of most CU memory accesses. The load-store pipeline is modeled in gem5, including the coalescing, virtual address translation, and cache arbitration logic. By using the port interface in gem5, *gem5-gpu* has the flexibility to vary the number of execution lanes, number of CUs, cache hierarchy, etc. and incorporate other GPU models in the future.

Currently, GPGPU-Sim issues only general-purpose memory instructions to gem5, including accesses to global and constant memory. We leverage GPGPU-Sim to model memory operations to scratchpad and parameter memory. Texture and local memory are

not currently supported although they only require straight-forward simulator augmentation.

*gem5-gpu* supports a shared virtual address space between the CPU and GPU (i.e., the GPU using the CPU page table for virtual to physical translations). Alternatively, through a configuration option, *gem5-gpu* models separate GPU and CPU physical address spaces.

#### Detailed cache coherence models

gem5-gpu leverages gem5's cache coherence modeling language, SLICC. When configuring gem5-gpu, any cache coherence protocol can be used, including the multitude that are currently distributed with gem5. However, these included protocols assume a homogeneous cache topology.

To augment these for heterogeneous computing, <code>gem5-gpu</code> adds a family of heterogeneous cache coherence protocols: <code>MOESI\_hsc</code> (heterogeneous system coherence with MOESI states). <code>MOESI\_hsc</code> uses a MOESI protocol for all of the CPU caches included in the system. For the GPU caches, we add an L2 cache controller that provides coherence between the GPU and CPU L2 caches. <code>MOESI\_hsc</code> models the GPU L1 cache similar to current GPU cache architectures: write-through and only valid and invalid states. Additionally, the GPU L1 cache may contain stale data that is flushed at synchronization points and kernel boundaries.

*gem5-gpu* also includes a split version of *MOESI\_hsc* that models architectures with separate CPU and GPU physical address spaces. When this model is used, communication between the CPU and GPU requires explicit memory copies through the DMA engine.

In addition to providing detailed cache coherence models, *gem5-gpu* can use any of the network topologies provided by gem5 (e.g., mesh, torus, crossbar). *gem5-gpu*'s default configuration uses the cluster topology to divide the CPU and GPU into two clusters. Accesses from each cluster goes through a common interconnect to the directory and memory controllers.

#### Application programming interface

To avoid the complexity of implementing or interfacing existing GPGPU drivers and runtimes, *gem5-gpu* provides a slim runtime and driver emulation. Similar to GPGPU-Sim, *gem5-gpu* runs unmodified GPGPU applications by linking against the *gem5-gpu* GPGPU runtime library. When a user application calls a GPGPU runtime function, gem5 pseudoinstructions execute to make up-calls into the simulator. This organization is flexible and extensible, making it convenient to add and test new features and integrate new GPU models.

#### Comparison to other simulators

In contrast to most other heterogeneous simulators, gem5-gpu captures interactions with execution-driven simulation rather than well-partitioned trace-driven simulation, e.g., MacSim [77]. It uses a more-detailed—therefore slower—GPU component than MV5 [91] and does not rely on the deprecated m5 simulator. It supports more flexible memory hierarchy and coherence protocols than Multi2Sim [148] or FusionSim [157] at a possible increase in simulation time.

Since the work was completed, AMD has released a GPU model as part of gem5 [14]. This model integrates into the Ruby memory system similarly to gem5-gpu. The main difference is that AMD's GPU model uses HSAIL, not PTX as the intermediate assembly language and OpenCL, not CUDA, as the main programming model.

#### Heterogeneous workloads

In Chapter 4, we evaluated the Rodinia workloads [27]. We modified these workloads to support the programming model enabled by implementing cache coherence and a shared virtual address space. We call our new workloads the "rodinia-nocopy" since we removed all of the copy statements from the workloads.

For most workloads, simply removing the copy from the host to device and using the host pointers was sufficient to implement the no copy version of the benchmark. However, in some cases, the memory copy transformed the data from one layout to another. In these cases, we had to further modify the workload to use the transformed data layout on the CPU as well as the GPU. We did not change the GPU kernels to have a constant comparison point with the legacy versions of the benchmarks.

Since the work in this chapter was completed, there have been many new GPU benchmarks released. Of note is Pannotia [26], whose workloads are much more irregular than Rodinia. Most of the Pannotia workloads are graph-based. Additionally, the Chai [45] workloads target "truly heterogeneous" benchmarks which use the CPU and GPU simultaneously. Both Pannotia and Chai have been ported to gem5-gpu with "nocopy" versions of the benchmarks.

# 3.2 Sampling methodology for native-size workloads

Simulation is an important tool for computer architecture research. It allows designers and researchers to evaluate future hypothetical systems without physically building them, which can be expensive. Additionally, it is much more flexible than physical hardware, allowing researchers to more easily explore many design parameters. However, simulation has drawbacks. One drawback is its very slow execution time.

Some important workloads, like the HPC workloads evaluated in Chapter 7, have large working set sizes and long execution times. Straightforwardly simulating these workloads is infeasible. For instance when running gem5 [19] in full-system mode with 32 cores the execution time is between  $300,000 \times$  and  $500,000 \times$  slower than native execution. To simulate one minute of native time it takes about a year of simulation time, and many workloads execute for hours!

There is a rich history of sampling methodologies for computer architecture simula-

tion [136, 155]. However, these previous techniques rely on fast-forwarding via high-level simulation, which still results in large slowdowns (e.g.,  $1000 \times$  or more).

Therefore, we leverage recent work which uses virtualization hardware to fast-forward at near native speeds [133]. Sandberg et al. use the KVM vitualization solution built into modern Linux kernels and essentially implement another CPU model in gem5.

Our contribution beyond the state of the art discussed above is packaging these features into a set of usable scripts. An important feature of this methodology is its scalability. For instance, to simulates 100 sample points, this methodology allows the use of ten machines in parallel each producing data for ten sample points.

# Description of sampling methodology

There are three phases in our sampling methodology: program analysis, random sampling, data analysis. Algorithm 1 shows an overview of our sampling algorithm.

#### **Program analysis**

First, we run the application in gem5 with the KVM CPU for its entire runtime from the beginning to the end of the region of interest. Currently, the only information we use from this phase is the total number of instructions executed during the region of interest. Section 8 discusses some ideas of how to extend this analysis to provide richer information to guide the sampling described below.

#### Random sampling

Currently, we use simple random sampling to choose when to run detailed simulation. Taking the instruction count from the program analysis phase, we choose n random instructions uniformly from the total number of instructions to perform detailed simulation (line 2). The simulation results beginning at a particular instruction is an *observation*. Once we have a list of instructions for which we will begin a simulation point, we start executing

#### Algorithm 1 Sampling algorithm

**Require:** n: number of observation points

**Require:** instructions: total number of instructions points = [] // Instructions to begin simulation

for i := 1 to n do

2:  $points \leftarrow random(0, n)$

Sort points

4: **for** each point in points **do**

Run application under KVM until point instructions executed

6: Fork new process

Warm up the system for warmup time

8: Run detailed simulation for detailed time

**Dump statistics**

10: End new process

the application from the beginning under KVM. We stop the application at each of the instruction numbers in points (line 5) to perform an observation.

Then, we essentially "pause" the application running on the KVM CPU. In the meantime, we fork a new process on the host machine to simulate beginning at the observation point instruction. In this new process, we perform warmup and detailed simulation with gem5. In Chapter 7, we use a warmup for 10 ms and perform detailed simulation for 2 ms of guest time (about 10,000,000–30,000,000 instructions of detailed simulation). After the simulation, we dump all of the statistics, exit the subprocess, and continue running the KVM CPU until the next observation point.

These observation locations are non-deterministic. Due to operating system effects such as thread scheduling and I/O each time the application is executed the total number of instructions varies. Additionally, KVM does not exit at precisely the requested number of instructions. This non-determinism may cause bias in our sample statistics; we have not analyzed this methodology for bias.

#### Data analysis

The goal when measuring application performance is to predict the total runtime of the application, or the amount of time the applications uses to complete its *work*. We choose to measure either the floating point operations per second (FLOPs) or user-mode instructions for integer-only applications. We use the number of these instructions executed as a proxy for the the *work* the application accomplishes during a single observation. Thus, we assume a higher FLOP rate implies the application will complete in less time (e.g., have higher performance).

When comparing performance of different simulation configurations, we use the mean of the FLOPs or user-mode operations from our sample of application execution. In Chapter 7 we additionally present a 95% confidence interval for this sample mean calculated using the Student's t-distribution.

#### **Summary**

With this sampling methodology, we can evaluate natively-sized workloads. We do not require workload modification to make simulation feasible. By using unmodified workloads, we ensure we are capturing their true behavior which gives us more confidence in our conclusions. There are many ways to make this methodology even more robust and to extend it to other workloads outside of scientific computing. Section 8 describes some ideas for extending this methodology.

# --4

# TIGHTLY-INTEGRATED GPGPU ADDRESS TRANSLATION

#### 4.1 Introduction

Although physical integration of CPUs and GPUs is becoming widespread, the GPGPU compute platform is still widely separated from conventional CPUs in terms of its programming model. CPUs have long used virtual memory to simplify data sharing between threads, but GPUs still lag behind.

A shared virtual address space allows "pointer-is-a-pointer" semantics [126] which enable any pointer to be dereferenced on the CPU and the GPU (i.e., each data element only has a single name). This model simplifies sharing data between the CPU and GPU by removing the need for explicit copies, as well as allowing the CPU and GPU to share access to rich pointer-based data structures.

Unfortunately, there is no free lunch. Translating from virtual to physical addresses comes with overheads. Translation look-aside buffers (TLBs) consume a significant amount of power due to their high associativity [67, 68, 138], and TLB misses can significantly decrease performance [13, 18, 70, 90]. Additionally, correctly designing the memory manage-

ment unit (MMU) is tricky due to rare events such as page faults and TLB shootdown [150].

Current GPUs have limited support for virtualized addresses [34, 81, 146]. However, this support is poorly documented publicly and has not been thoroughly evaluated in the literature. Additionally, industry has implemented limited forms of shared virtual address space. NVIDIA proposed Unified Virtual Addressing (UVA) and OpenCL has similar mechanisms. However, UVA requires special allocation and pinned memory pages [101] which can have significant performance impact [95].

The HSA foundation announced heterogeneous Uniform Memory Accesses (hUMA) which will implement a shared virtual address space in future heterogeneous processors [128], but details of this support are not available in public literature.

Engineering a GPU MMU appears challenging, as GPU architectures deviate significantly from traditional multicore CPUs. Current integrated GPUs have hundreds of individual execution lanes, and this number is growing. For instance the AMD A10 APU, with 400 lanes, can in principle require up to 400 unique translations in a single cycle! In addition, the GPU is highly multithreaded which leads to many memory requests in flight at the same time.

To drive GPU MMU design, we present an analysis of the memory access behavior of current GPGPU applications. Our workloads are taken from the Rodinia benchmark suite [27] and a database sort workload. We present three key findings and a potential MMU design motivated by each finding:

- 1. The coalescing hardware and scratchpad memory effectively filter the TLB request rate. Therefore, the L1 TLB should be placed after the coalescing hardware to leverage the traffic reduction.

- 2. Concurrent TLB misses are common on GPUs with an average of 60 to a maximum of over 1000 concurrent page walks! This fact motivates a highly-threaded page table walker to deliver the required throughput.

3. GPU TLBs have a very high miss rate with an average of 29%. Thus, reducing TLB miss penalty is crucial to reducing the pressure on the page table walker, and thus, we employ a page walk cache.

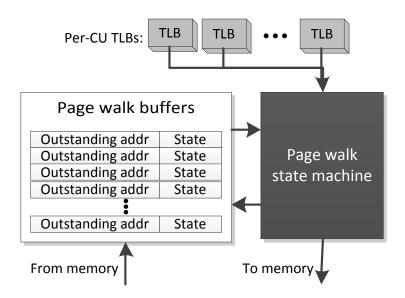

Through this data-driven approach we develop a proof-of-concept GPU MMU design that is fully compatible with CPU page tables (x86-64 in this work). Figure 4.6 shows an overview of the GPU MMU evaluated in this chapter. This design uses a TLB per GPU compute unit (CU) and a shared page walk unit to avoid excessive per-CU hardware. The shared page walk unit contains a highly-threaded page table walker and a page walk cache.

The simplicity of this MMU design shows that address translation can be implemented on the GPU without exotic hardware. We find that using this GPU MMU design incurs modest performance degradation (an average of less than 2% compared to an ideal MMU with an infinite sized TLB and minimal latency page walks) while simplifying the burden on the programmer.

In addition to our proof-of-concept design, we present a set of alternative designs that we also considered, but did not choose due to poor performance or increased complexity. These designs include adding a shared L2 TLB, including a TLB prefetcher, and alternative page walk cache designs. We also analyzed the impact of large pages on the GPU TLB. We find that large pages do in fact decrease the TLB miss rate. However, in order to provide compatibility with CPU page tables, and ease the burden of the programmer, we cannot rely solely on large pages for GPU MMU performance.

The contributions of this work are:

- An analysis of the GPU MMU usage characteristics for GPU applications,

- A proof-of-concept GPU MMU design which is compatible with x86-64 page tables,

and

- An evaluation of our GPU MMU design that shows a GPU MMU can be implemented without significant performance degradation.

# 4.2 Background

General background on GPU architecture is covered in Chapter 2. In this section, we focus on the GPU programming model details that relate to shared virtual memory and background on CPU MMU designs.

## GPU programming model

Current GPGPU programming models consider the GPU as a separate entity with its own memory, virtual address space, scheduler, etc. Programming for the GPU currently requires careful management of data between CPU and GPU memory spaces.

Figure 4.1 shows an example CUDA application. Figure 4.1a shows a simple kernel that copies from one vector (in) to another (out). Figure 4.1b shows the code required to use the vectorCopy kernel using the current separate address space paradigm. In addition to allocating the required memory on the host CPU and initializing the data, memory also is explicitly allocated on, and copied to, the GPU before running the kernel. After the kernel completes, the CPU copies the data back so the application can use the result of the GPU computation.

There are many drawbacks to this programming model. Although array-based data structures are straightforward to move from the CPU to the GPU memory space, pointer-based data structures, like linked-lists and trees, present complications. Also, separate virtual address spaces cause data to be replicated. Even on shared physical memory devices, like AMD Fusion, explicit memory allocation and data replication is still widespread due to separate virtual address spaces. Additionally, due to replication, only a subset of the total memory in a system is accessible to GPU programs. Finally, explicit separate allocation and data movement makes GPU applications difficult to program and understand as each logical variable has multiple names (d\_in, h\_in and d\_out, h\_out in the example).

Beginning with the Fermi architecture, NVIDIA introduced "unified virtual addressing"

```

__device__ void vectorCopy(int *in, int *out) {

out[threadId.idx] = in[threadId.idx];

}

(a) Simple vector copy kernel

void main() {

int *d_in, *d_out;

int *h_in, *h_out;

// allocate input array on host

h_{in} = new int[1024];

h_{in} = \dots // Initial host array

// allocate output array on host

h_out = new int[1024];

// allocate input array on device

d_in = cudaMalloc(sizeof(int)*1024);

// allocate output array on device

d_out = cudaMalloc(sizeof(int)*1024);

// copy input array from host to device

cudaMemcpy(d_in, h_in, sizeof(int)*1024, HtD);

vectorCopy <<<1,1024>>>(d_in, d_out);

// copy the output array from device to host

cudaMemcpy(h_out, d_out, sizeof(int)*1024, DtH);

// continue host computation with result

... h_out

//Free memory

cudaFree(d_in); cudaFree(d_out);

delete[] h_in; delete[] h_out;

}

(b) Separate memory space implementation

int main() {

int *h_in, h_out;

// allocate input/output array on host

h_in = cudaHostMalloc(sizeof(int)*1024);

h_in = ... // Initial host array

h_out = cudaHostMalloc(sizeof(int)*1024);

vectorCopy <<<1,1024>>> (h_in, h_out);

// continue host computation with result

... h out

//Free memory

cudaHostFree(h_in); cudaFree(h_out);

}

```

(c) "Unified virtual address" implementation

```

int main() {

int *h_in, h_out;

// allocate input/output array on host

h_in = new int[1024];

h_in = ... // Initial host array

h_out = new int[1024];

vectorCopy <<<1,1024>>> (h_in, h_out);

// continue host computation with result

... h_out

delete[] h_in; delete[] h_out;

}

```

(d) Shared virtual address space implementation

Figure 4.1: Example GPGPU application

(UVA) [101] (OpenCL has a similar feature as well). Figure 4.1c shows the implementation of vectorCopy with UVA. The vector-copy kernel is unchanged from the separate address space kernel. In the UVA example, instead of allocating two copies of the input and output vectors, only a single allocation is necessary. However, this allocation requires a special API which creates difficulties in using pointer-based data structures. Separate allocation makes composability of GPU kernels in library code difficult as well, because the allocation is a CUDA runtime library call, not a normal C or C++ allocation (e.g. new/malloc/mmap). Memory allocated via cudaMallocHost can be implemented in two different ways. Either the memory is pinned in the main memory of the host, which can lead to poor performance [100], or the data is implicitly copied to a separate virtual address space which has the previously discussed drawbacks.

Figure 4.1d shows the implementation with a shared virtual address space (the programming model used in this chapter). In this implementation, the application programmer is free to use standard memory allocation functions. Also, there is no extra memory allocated, reducing the memory pressure. Finally, by leveraging the CPU operating system for memory allocation and management, the programming model allows the GPU to take page faults and access memory mapped files. HSA hUMA takes a similar approach [128].

## CPU MMU design

The memory management unit (MMU) on CPUs translates virtual addresses to physical address as well as checks page protection. In this chapter we focus on the x86-64 ISA; however, our results generalize to any multi-level hardware-walked page table structure. The CPU MMU for the x86-64 ISA consists of three major components: 1) logic to check protection and segmentation on each access, 2) a translation look-aside buffer to cache virtual to physical translations and protection information to decrease translation latency, and 3) logic to walk the page table in the case of a TLB miss. In this work, we use the term MMU to refer to the unit that contains the TLB and other supporting structures. Many modern CPU MMU designs contain other structures to increase TLB hit rates and decrease TLB miss latency.

The x86-64 page table is a 4-level tree structure. By default, the TLB holds page table entries, which reside in the leaves of the tree. Therefore, on a TLB miss, up to four memory accesses are required. The page table walker (PTW) traverses the tree from the root which is found in the CR3 register. The PTW issues memory requests to the page walk cache that caches data from the page table. Requests that hit in the page walk cache decrease the TLB miss penalty. Memory requests that miss in the page walk cache are issued to the memory system similar to CPU memory requests and can be cached in the data caches.

The x86-64 ISA has extensions for 2 MB and 1 GB pages in addition to the default 4 KB page size. However, few applications currently take advantage of this huge page support. Additionally, it is important for an MMU to support 4 KB pages for general compatibility with all applications.

# 4.3 Simulation methodology and workloads

We used a cycle-level heterogeneous simulator, gem5-gpu [115] (Section 3.1), to simulate the heterogeneous system. Results are presented for 4 KB pages. Large page support is

| CPU               | 1 core, 2 GHz, 64 KB L1, 2 MB L2             |

|-------------------|----------------------------------------------|

| GPU               | 16 CUs, 1.4 GHz, 32 lanes                    |

| L1 cache (per-CU) | 64 KB, 4-way set associative, 15 ns latency  |

| Scratchpad memory | 16 KB, 15 ns latency                         |

| GPU L2 cache      | 1 MB, 16-way set associative, 130 ns latency |

| DRAM              | 2 GB, DDR3 timing, 8 channel, 667 MHz        |

Table 4.1: Details of simulation parameters

discussed in Section 4.6. Table 4.1 shows the configuration parameters used in obtaining our results. Section 3.1 contains the details of gem5-gpu.

We use a subset of the Rodinia benchmark suite [27] for our workloads. We do not use some Rodinia benchmarks as the input sizes are too large to simulate. The Rodinia benchmarks are GPU-only workloads, and we use these workloads as a proxy for the GPU portion of future heterogeneous workloads (details on changes made to the Rodinia workloads in Section 3.1). We add one workload, sort, to this set. Sort is a database sorting kernel that sorts a set of records with 10 byte keys and 90 byte payloads. All workloads are modified to remove the memory copies, and all allocations are with general allocators (new/malloc/mmap). Although we are running in a simulation environment and using reduced input sized, many of our working sets are much larger than the TLB reach; thus, we expect our general findings to hold as working set size increases.

As a baseline, we use an ideal, impossible to implement MMU. We model an ideal MMU with infinite sized per-CU TLBs and minimal latency (1 cycle cache hits) for page walks. This is the minimum translation overhead in our simulation infrastructure.

# 4.4 Designing a GPU MMU through analysis

We meet the challenges of designing a GPU MMU by using data to evolve through three architectures to our proof-of-concept recommendation (Design 3). Design 3 enables full compatibility with x86-64 page tables with less than 2% performance overhead, on average. Table 4.2 details the designs in this section as well as the additional designs from Section 4.6.

|                 | Per-CU L1          | Highly-threaded   | Page walk  | Shared L2   |

|-----------------|--------------------|-------------------|------------|-------------|

|                 | TLB entries        | page table walker | cache size | TLB entries |

| Ideal MMU       | Infinite           | Infinite          | Infinite   | None        |

| Section 4.4     |                    |                   |            |             |

| Design 0        | N/A: Per-lane MMUs |                   | None       | None        |

| Design 1        | 128                | Per-CU walkers    | None       | None        |

| Design 2        | 128                | Yes (32-way)      | None       | None        |

| Design 3        | 64                 | Yes (32-way)      | 8 KB       | None        |

| Section 4.6     |                    |                   |            |             |

| Shared L2       | 64                 | Yes (32-way)      | None       | 1024        |

| Shared L2 & PWC | 32                 | Yes (32-way)      | 8 KB       | 512         |

| Ideal PWC       | 64                 | Yes (32-way)      | Infinite   | None        |

| Latency         | 1 cycle            | 20 cycles         | 8 cycles   | 20 cycles   |

Table 4.2: Configurations under study. Structures are sized so each configuration uses 16 KB of storage.

We start with a CPU-like MMU (Design 0) and then modify it as the GPU data demands. Design 0 follows CPU core design with a private MMU at each lane (or "core" in NVIDIA terminology). Design 0 has the same problems as a CPU MMU—high power, on the critical path, etc.—but they are multiplied by the 100s of GPU lanes. For these reasons, we do not quantitatively evaluate Design 0.

# Motivating Design 1: Post-coalescer MMU

Here we show that moving the GPU MMU from before to after the coalescer (Design  $0 \rightarrow$  Design 1) reduces address translation traffic by 85%.

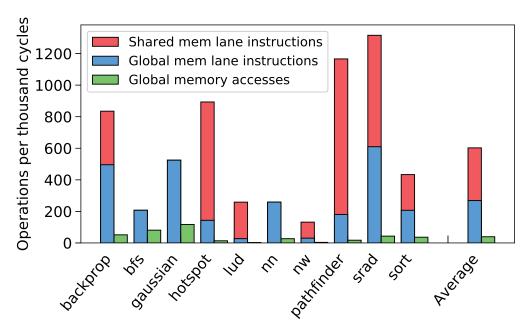

GPU memory referencing behavior differs from that of CPUs. For various benchmarks, Figure 4.2 presents operations per thousand cycles for scratchpad memory lane instructions (left bar, top, blue), pre-coalescer global memory lane instructions (left bar, bottom, green), and post-coalescer global memory accesses (right bar, brown). The "average" bars represent the statistic if each workload was run sequentially, one after the other.

Figure 4.2 shows that, for every thousand cycles, the benchmarks average:

• 602 total memory lane instructions,

Figure 4.2: All memory operations, global memory operations, and global memory accesses per thousand instructions.

- 268 of which are global memory lane instructions (with the other 334 to scratchpad memory), and

- Coalescing reduces global memory lane instructions to only 39 global memory accesses.

In total, the rate of memory operations is reduced from 602 to 39 per thousand cycles for an 85% reduction.

Although the coalescing hardware is effective, the benchmarks do show significant memory divergence. Perfect coalescing on 32 lanes per CU would reduce 268 global memory lane instructions (per thousand cycles) by  $32 \times$  to 9, which is much less than the 39 observed.

To benefit from this bandwidth filtering, *Design 1* includes a private per-CU L1 TLB after scratchpad memory access and after the coalescing hardware. Thus, the MMU is only accessed on global memory accesses. Figure 4.6 shows Design 1 in light gray and Table 4.2 details the configuration parameters.

Figure 4.3: Performance of each design relative to an ideal MMU. See Table 4.2 for details of configurations.

Figure 4.4: Average and max size of the page walk queue for each per-CU MMU in Design 1. Log scale, bold line at 2.

# Motivating Design 2: Highly-threaded page table walker

Here we show that Design 1 fails to perform well (average performance is 30% of an ideal MMU), isolate the problem to bursts of TLBs misses (60 concurrent), and advocate for a highly-threaded PTW (Design 2).

Now that we have mitigated the bandwidth issues, we might expect Design 1 to perform well; it does not. For each benchmark and the average, Figure 4.3 shows the performance of Design 1 (leftmost, red) compared to an ideal MMU with an impossibly low latency and infinite sized TLBs. Performance is good when it is close to the ideal MMU's 1.0. (Designs 2 (blue) and 3 (green) will be discussed later.)

Figure 4.3 results show that Design 1 (blue) performs:

- Poorly on average (30% of ideal's),

- Sometimes very poorly (about 10% of ideal for backprop, bfs, and pathfinder), and

- Occasionally adequately (gaussian and lud).

These performance variations occur for various reasons. For example, bfs is memory bound—having few instructions per memory operation—making it particularly sensitive to global memory latency. On the other hand, gaussian and lud perform well, in part because the working set sizes are relatively small.

Investigating Design 1's poor performance lead to an obvious culprit: bursts of TLB misses. For each benchmark and the average, Figure 4.4 shows the average (left, red) and maximum across CUs (right, blue) occupancy of the page walk queue when each page walk begins. Note that the y-axis is logarithmic.

Figure 4.4 shows that when each page walk is issued:

- An average of 60 page table walks are active at that CU, and

- The worst workload averages 140 concurrent page table walks.

Moreover, additional data show that, for these workloads, over 90% of page walks are issued within 500 cycles of the previous page walk, which is significantly less than the average page walk latency in this design. Also, almost all workloads use many more than 100 concurrent page walks at the maximum. Therefore, these workloads will experience high queuing delays with a conventional blocking page table walker. This also shows that

the GPU MMU requires changes from the CPU-like single-threaded pagetable walker of Design 1.

This high page walk traffic is primarily because GPU applications can be very bandwidth intensive. GPU hardware is built to run instructions in lock step, and because of this characteristic, many GPU threads simultaneously execute a memory instruction. This, coupled with the fact each CU supports many simultaneous warp instructions, means GPU TLB miss traffic will be high.

Therefore, *Design 2* includes a shared multi-threaded page table walker with 32 threads. Figure 4.6 shows how Design 2 builds on Design 1 in dark gray and Table 4.2 details the configuration parameters. The page walk unit is shared between all CUs on the GPU to eliminate duplicate hardware at each CU and reduce the hardware overhead. On a TLB miss in the per-CU L1 TLBs, the shared page walk unit is accessed and executes a page walk.

Recent work by Yoon et al. has further studied the page table walk bandwidth bottleneck in heterogeneous systems [156]. In this thesis, we do not constrain the bandwidth at the shared page walk unit. This has a small performance impact on the Rodinia workloads analyzed in this thesis. However, Yoon et al. show this is a poor assumption when running graph-based and irregular workloads [156].

## Motivating Design 3: Add a page walk cache

Here we show that Design 2 performs much better than Design 1 for most workloads but still falls short of an ideal MMU (30% of ideal on average). For this reason, we introduce Design 3 that adds a shared page walk cache to perform within 2% of ideal.

The second bars in Figure 4.3 (blue) show the performance of each benchmark for Design 2. Results from this figure show that Design 2:

• Often performs much better than Design 1, but

Figure 4.5: Miss rate for a 128 entry per-CU L1 TLB averaged across all CUs.

That these benefits are inconsistent and short of ideal

We find the workloads that perform best have been tuned to tolerate long latency memory operations and the addition of the TLB miss latency is hidden by thread parallelism.

On the other hand, some workloads, e.g., bfs and nw, actually perform worse with Design 2 than Design 1. We isolated the problem to the many requests from one CU queuing in front of another CU's requests rather than being handled more round robin as in the single-threaded page-table walker of Design 1. While this specific effect might be fixed by changing PTW queuing from first-come-first-serve, we seek a more broadly effective solution.

To better understand why Design 2 falls short of ideal, we examined the TLB miss rates. Figure 4.5 shows the miss rates (per-CU, 128 entry) for each benchmark and the average.

Figure 4.5 results show that per-CU TLB miss rates:

- Average 29% across benchmarks and

- Can be as high as 67% (nw).

Needless to say, these rates are much higher than one expects for CPU TLBs. Gaussian is a low outlier, because of high computational density (compute operations per byte of

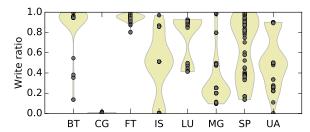

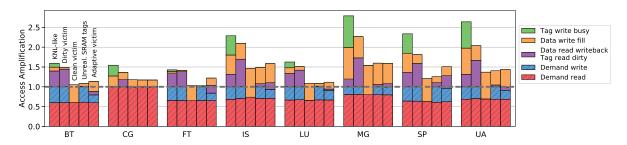

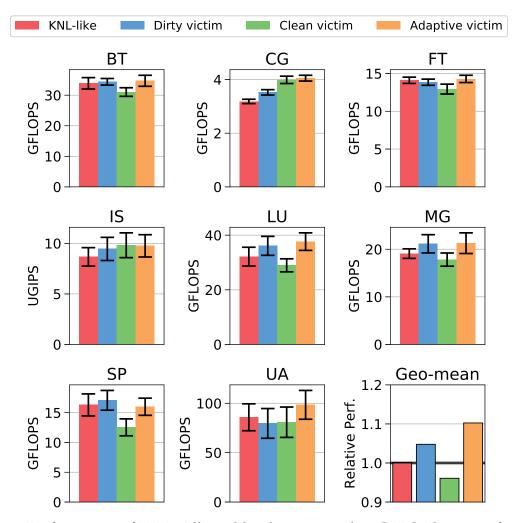

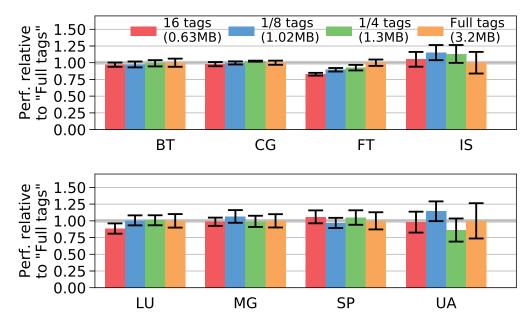

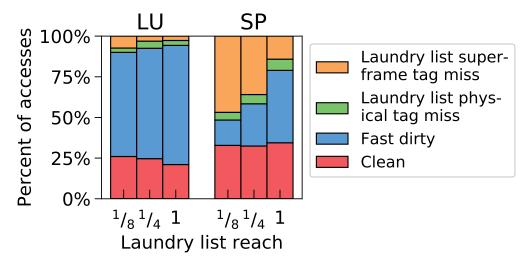

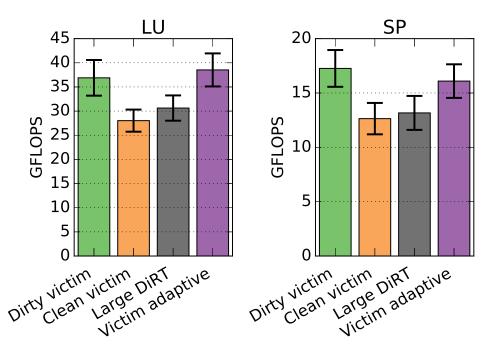

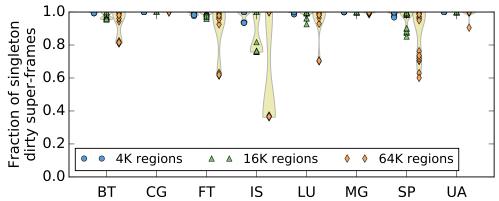

data) and small working set (so all TLB misses are compulsory misses).