# **Fault Tolerance in Tandem Computer Systems**

Joel Bartlett \* Wendy Bartlett Richard Carr Dave Garcia Jim Gray Robert Horst Robert Jardine Dan Lenoski Dix McGuire

\* Present address: Digital Equipment Corporation Western Regional Laboratory, Palo Alto, California

Technical Report 90.5 May 1990 Part Number: 40666

# TANDEM COMPUTERS

# Fault Tolerance in Tandem Computer Systems

Joel Bartlett\* Wendy Bartlett Richard Carr Dave Garcia Jim Gray Robert Horst Robert Jardine Dan Lenoski Dix McGuire

\* Present address: Digital Equipment Corporation Western Regional Laboratory, Palo Alto, California

Technical Report 90.5 May 1990 Part Number: 40666

.

.

# Fault Tolerance in Tandem Computer Systems<sup>1</sup>

Wendy Bartlett, Richard Carr, Dave Garcia, Jim Gray, Robert Horst, Robert Jardine, Dan Lenoski, Dix McGuire Tandem Computers Incorporated Cupertino, California

Joel Bartlett Digital Equipment Corporation, Western Regional Laboratory Palo Alto, California

Tandem Technical Report 90.5, Tandem Part Number 40666 March 1990

#### ABSTRACT

Tandem produces high-availability, general-purpose computers that provide fault tolerance through failfast hardware modules and fault-tolerant software<sup>2</sup>. This chapter presents a historical perspective of the Tandem systems' evolution and provides a synopsis of the company's current approach to implementing these systems. The article does not cover products announced since January 1990.

At the hardware level, a Tandem system is a loosely-coupled multiprocessor with fail-fast modules connected with dual paths. A system can include a range of processors, interconnected through a hierarchical fault-tolerant local network. A system can also include a variety of peripherals, attached with dual-ported controllers. A novel disk subsystem allows a choice between low cost-per-byte and low cost-per-access.

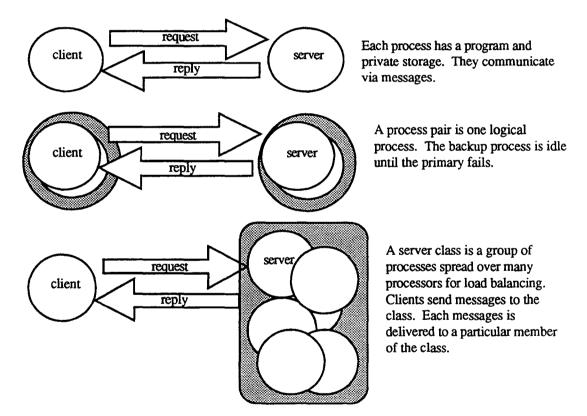

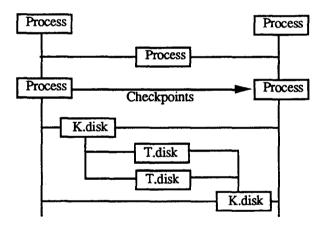

System software provides processes and messages as the basic structuring mechanism. Processes furnish software modularity and fault isolation; process pairs tolerate hardware and transient software failures. Applications are structured as requesting processes that make remote procedure calls to server processes. Process server classes utilize multiprocessors. The resulting process abstractions provide a distributed system that can take advantage of thousands of processors. High-level networking protocols such as SNA, OSI, and a proprietary network are built on top of this base.

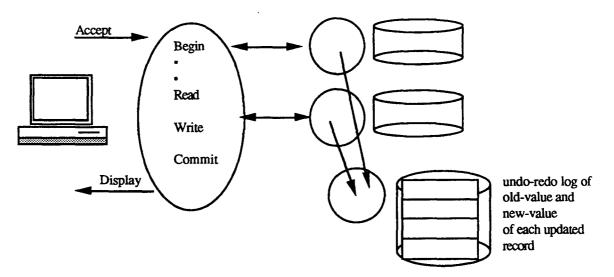

A relational database provides distributed data and distributed transactions. Databases can optionally be replicated at several sites for protection against environmental disasters. An application generator allows users to develop fault-tolerant applications as though the system were a conventional computer. The resulting system provides price/performance competitive with traditional systems.

<sup>&</sup>lt;sup>1</sup>This article is scheduled to appear as a chapter of the second edition of the book *Theory and Practice of Reliable System Design*, edited by D. Siewiorek, and published by Digital Press. It is a revision of a two-year-old version of the paper of the same title, which is now obsolete.

<sup>&</sup>lt;sup>2</sup> The following are trademarks or service marks of Tandem Computers Incorporated: CLX, CYCLONE, DYNABUS, DYNABUS+, ENCOMPASS, ENFORM, ENSCRIBE, EXPAND, FOX, GUARDIAN, GUARDIAN 90, MEASURE, NonStop, NonStop SQL, PATHMAKER, TAL, Tandem, TMDS, TXP, VIEWPOINT, VLX...

# TABLE OF CONTENTS

| INTRODUCTION                                                         | 1               |

|----------------------------------------------------------------------|-----------------|

| HARDWARE                                                             | 3               |

| HARDWARE ARCHITECTURE                                                | 3               |

| PROCESSOR MODULES                                                    | 4               |

| DYNABUS INTERPROCESSOR BUS                                           | 6               |

| FIBER-OPTIC EXTENSION (FOX) LINKS                                    |                 |

| DYNABUS+ FIBER-OPTIC DYNABUS EXTENSION                               | 8               |

| SYSTEM POWER AND PACKAGING                                           |                 |

| EVOLUTIONARY CHANGES                                                 |                 |

| PERIPHERALS                                                          |                 |

| The 6100 Communication Subsystem                                     | 11              |

| Disk Subsystem                                                       | 11              |

| Peripheral Controllers                                               | 12              |

| Peripheral Controllers                                               | 15              |

| NonStop I                                                            | 15              |

| NonStop I<br>Dual-Port Controllers                                   | 15              |

| Fault-Tolerant I/O Considerations                                    | 16              |

| NonStop II                                                           |                 |

| I/O Channel                                                          | 17              |

| Diagnostic Data Transceiver (DDT)                                    |                 |

| Virtual Memory                                                       | 18              |

| Maintenance                                                          | 10              |

| TXP PROCESSOR                                                        |                 |

|                                                                      |                 |

| Manufacturing and Testing                                            | 22              |

| Maintenance                                                          |                 |

| CLX PROCESSOR MODULE                                                 | $\frac{24}{24}$ |

| Data Integrity Through Fail-Fast Operation                           |                 |

| CYCLONE PROCESSOR MODULE                                             | 32              |

| Cyclone Technology                                                   |                 |

| Cyclone Processor Architecture                                       | 32              |

| Cyclone Fault Tolerance, Data Integrity, and Reliability Features    | 35              |

| MAINTENANCE FACILITIES AND PRACTICES                                 | 37              |

| EARLY METHODS                                                        |                 |

| OPERATIONS AND SERVICE PROCESSOR (OSP)                               | 37              |

| Tandem Maintenance and Diagnostic System (TMDS)                      | 27              |

| SOFTWARE                                                             | 40              |

| Overview                                                             |                 |

| GUARDIAN: An Integrated OLTP Operating System                        | 40              |

| Fundamental System Structure                                         | 41              |

| Fundamental System Structure<br>Initialization and Processor Loading | 42              |

| Processor Synchronization                                            | 43              |

| I'm Alive Protocol                                                   | 43              |

| Regroup Protocol                                                     |                 |

| Global Update Protocol                                               |                 |

| Time Synchronization                                                 |                 |

| GUARDIAN Kernel Services.                                            |                 |

| Processes                                                            |                 |

| Memory Management                                                    |                 |

| Interprocess Messages                                                |                 |

| Tolerating Software Faults                                           |                 |

| Process Pairs                                                        |                 |

| I/O Processes                                                        |                 |

| · · · · · · · · · · · · · · · · · · ·                                |                 |

| Disk Process                             | . 51 |

|------------------------------------------|------|

| Mirrored Disks                           | . 51 |

| Disk Cache                               | . 51 |

| Partitioning                             | . 52 |

| Locking and Transaction Protection       |      |

| File System                              |      |

| NonStop SQL                              |      |

| Transactions                             |      |

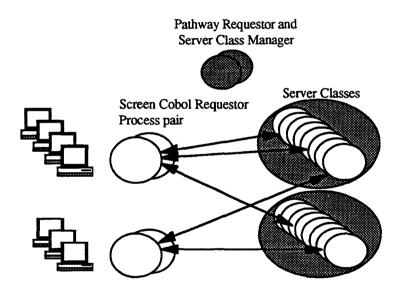

| Transaction Processing Monitor (PATHWAY) |      |

| Process Server Classes                   | . 57 |

| Networking                               |      |

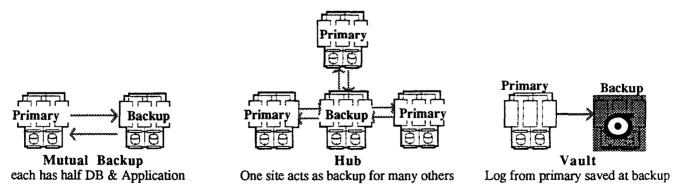

| Disaster Protection                      |      |

| Operating System Summary                 |      |

| Application Software                     |      |

| OPERATIÔNS                               |      |

| SUMMARY AND CONCLUSIONS.                 |      |

| REFERENCES                               |      |

#### **INTRODUCTION**

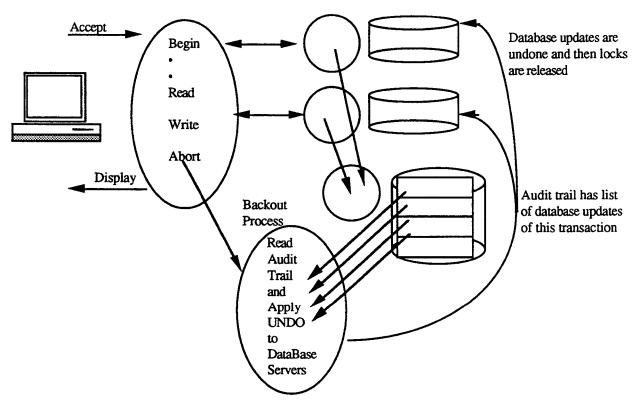

The increasing trend for businesses to go online stimulated a need for cost-effective computer systems with continuous availability [Katzman, 1977]. The strongest demand for general-purpose fault-tolerant computing was in online database transaction and terminal-oriented applications.

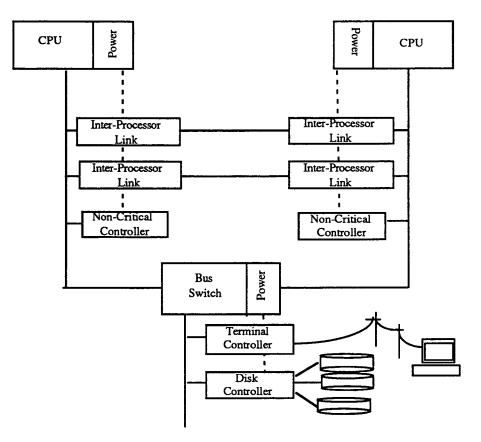

In the early 1970's, vendors and customers demanding continuous availability configured multiprocessor systems as hot-standbys (see Figure 1). This preserved previous development effort and compatibility by introducing devices, such as I/O channel switches and interprocessor communications adapters, to retrofit existing hardware. These architectures, however, still contained many single points of failure. For an example, a power supply failure in the I/O bus switch, or an integrated circuit failure in any I/O controller on the I/O bus switch channel, would cause the entire system to fail. Other architectures used a common memory for interprocessor communications, creating another single point of failure. Typically, these architectures did not even approach the problems of online maintenance, redundant cooling, or a power distribution system that tolerates brownout conditions. Furthermore, these systems lacked thorough data integrity features, leading to problems in fault containment and possible database corruption.

Figure 1. An example of Early Fault-Tolerant Architectures

As late as 1985, conventional, well-managed, transaction-processing systems failed about once every two weeks for about an hour [Mourad and Andrews, 1985 and Burman, 1985]. This failure rate translates to 99.6% availability, a level that reflects a considerable effort over many years to improve system availability. When the sources of faults were examined in detail, a surprising picture emerged: faults come from hardware, software, operations, maintenance, and the environment in about equal

measure. Hardware could operate for two months without generating problems; software was equally reliable. The result was a one month Mean Time Between Failures (MTBF). But if operator errors, errors during maintenance, and power failures, were included, the MTBF fell below two weeks.

Based on this analysis, Tandem set out to build a system whose MTBF is measured in years<sup>3</sup>--more than two orders of magnitude better than conventional designs. The key design principles of the system were, and still are, the following:

- Modularity: Both hardware and software are based on modules of fine granularity that are units of service, failure, diagnosis, repair, and growth.

- Fail-Fast Operation: Each module is self-checking; when it detects a fault, the module stops.

- Single Fault Tolerance: When a hardware or software module fails, another module immediately takes over the failed module's function--giving a mean-time-to-repair measured in milliseconds. For processors or processes, this takeover means that a second processor or process must exist. For storage modules, it means that the modules and the paths to them are duplexed.

- Online Maintenance: Hardware and software can be diagnosed and repaired while the rest of the system continues to deliver service. When the hardware, programs, or data are repaired, they are reintegrated without interrupting service.

- Simplified User Interfaces: Complex programming and operations interfaces can be a major source of system failures. Every attempt has been made to simplify or automate interfaces to the system.

This chapter presents Tandem systems, viewed from the perspective of these key design features.

<sup>&</sup>lt;sup>3</sup> The actual goal was to build a system with 100-year MTBF.

#### HARDWARE

Multiple hardware modules and multiple interconnections among those modules provide a basis for fault-tolerant operation. Two modules of a certain type are generally sufficient for hardware fault tolerance because the probability of a second independent failure during the repair interval of the first is extremely low. For instance, if a processor has a mean-time between failures of ten thousand hours (about a year) and a repair time of four hours, the MTBF of a dual-path system increases to about ten million hours (about one thousand years). If more than two processors were added, the further gains in reliability would be obscured by system failures related to software or system operations.

**Modularity:** Modularity is important to fault-tolerant systems because individual modules must be replaceable online. Keeping modules independent also makes it less likely that a failure of one module will affect the operation of another module. Increasing performance by adding modules allows customers to expand the capacity of critical systems without requiring major outages to upgrade equipment.

Fail-Fast Logic: Fail-fast logic is defined as logic that either works properly or stops. Fail-fast logic is required to prevent corruption of data in the event of a failure. Hardware checks (including parity, coding, and selfchecking), as well as firmware and software consistency checks, provide fail-fast operation.

Serviceability: As mentioned before, maintenance is a source of outages. Ideally, the hardware should have no maintenance. When maintenance is required, it should require no special skills or tools.

**Price and Price/Performance:** Commercial pressures do not permit customers to pay a high premium for fault tolerance; if necessary, they will use more ad-hoc methods for coping with unreliable, but cost-effective, computers. Fault-tolerant vendors have no special exemption from the requirement to use state-of-the-art components and architectures, which frequently compounds the complexity already required by fault tolerance.

#### HARDWARE ARCHITECTURE

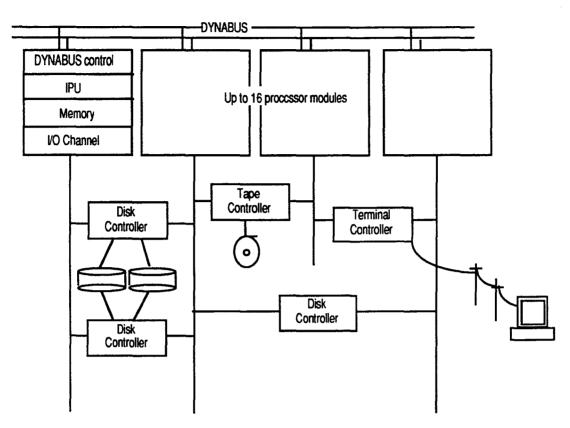

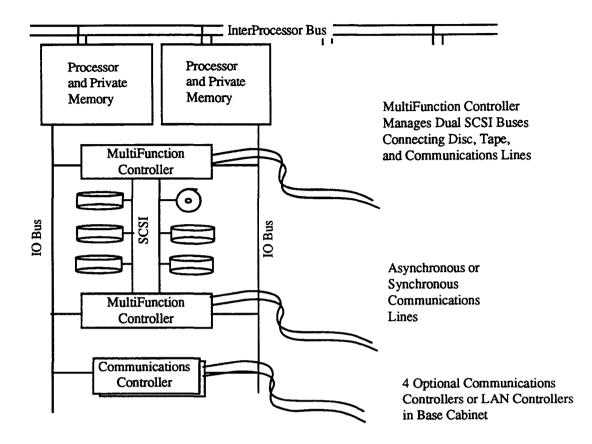

The Tandem NonStop<sup>™</sup> computer system was introduced in 1976 as the first commercial fault-tolerant computer system. Its basic architecture appears in Figure 2. The system includes from two to 16 processors connected by dual buses collectively known as the DYNABUS<sup>™</sup> interprocessor bus. Each processor has its own memory, containing its own copy of the operating system. The processors communicate with one another through messages passed through the DYNABUS mechanism. The system can continue operation despite the loss of any single component.

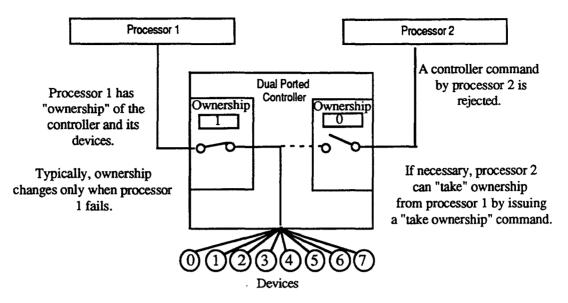

Each processor has its own Input/Output bus. Dual-ported controllers connect to I/O buses from two different processors. An ownership bit in each controller selects which of its ports is currently the primary path. When a processor or I/O bus failure occurs, all controllers that were designated as primary on that I/O bus switch to their backup paths. The controller configuration can be arranged so that in a multiprocessor system, the failure of a processor causes that processor's I/O workload to be spread out over the remaining processors.

Figure 2. Original Tandem System Architecture, 1976

All subsequent systems have been upward-compatible with this basic design.

# **PROCESSOR MODULES**

The primary components of a system are its processor modules, each of which includes an Instruction Processing Unit (IPU), memory, Input/Output channel, and DYNABUS interprocessor bus interface.

The design of the system's processor module is not much different from that of any traditional processor, with the addition of extensive error checking to provide fail-fast operation. Each processor operates independently and asynchronously from the rest of the processors. Another novel engineering requirement is that the DYNABUS interfaces must prevent a single-processor failure from disabling both buses. This requirement focuses on the proper selection of a single component type: the buffer that drives the bus. This buffer must be "well behaved" when power is removed from the processor module to prevent errors from being induced on both buses.

The power, packaging, and cabling must also be carefully considered. Parts of the system are redundantly powered through diode ORing of two different power supplies. In this way, I/O controllers and DYNABUS controllers tolerate a power supply failure. To allow online maintenance, and to allow modular growth, all boards are designed for *hot insertion*; that is, they can be inserted while the slot is powered. Battery backup power is standard in all systems. It preserves the system state for several hours in case of power failure.

The evolution of these processors is summarized in Table 1. Features common to all processors are described below. More details about the individual processors appear later in this chapter.

Each processor provides a basic set of instructions that includes operations on bits, integers, decimal numbers, floating-point numbers, and character strings; procedure calls and exits; I/O operations; and interprocessor SENDs to streamline the performance of the message-based operating system. All instructions are 16 bits long.

| Table 1. Summary of Tandem Processor Evolution |               |              |                                    |                     |                                       |                                       |                                       |  |

|------------------------------------------------|---------------|--------------|------------------------------------|---------------------|---------------------------------------|---------------------------------------|---------------------------------------|--|

| Processor                                      | NonStop I     | NonStop II   | TXP                                | VLX                 | CLX 600                               | CLX 700                               | Cyclone                               |  |

| Year                                           | 1976          | 1981         | 1983                               | 1986                | 1987                                  | 1989                                  | 1989                                  |  |

|                                                | Processor     |              |                                    |                     |                                       |                                       |                                       |  |

| MIPS/IPU                                       | 0.7           | 0.8          | 2.0                                | 3.0                 | 1.0                                   | 1.5                                   | 10.0                                  |  |

| Instructions                                   | 173           | 285          | 285                                | 285                 | 306                                   | 306                                   | 306                                   |  |

| Technology                                     | MSI           | MSI STTL     | MSI<br>Fast PAL                    | ECL<br>Gate Array   | Custom 2µ<br>CMOS                     | Custom 1.5µ<br>CMOS                   | ECL<br>Gate Array                     |  |

| Cycle Time                                     | 100ns         | 100ns        | 83ns                               | 83ns                | 133ns                                 | 91ns                                  | 45ns                                  |  |

| Microstore                                     |               | 8k x 32b     | two level:<br>8k x 40b<br>4k x 84b | 10k x 120b<br>dual  | 14k x 56b                             | 14k x 56b                             | 8k x 160b std<br>+<br>8k x 160b pairs |  |

| Cache (data and instructions)                  | •             | -            | 64KB<br>direct map                 | 64KB<br>direct map  | 64KB<br>direct map                    | 128KB<br>direct map                   | 2 x 64KB<br>direct map                |  |

| Gates (approx)                                 | 20k           | 30k          | 58k                                | 86k                 | 81k                                   | 81k                                   | 275k                                  |  |

| Proc. Boards                                   | 2             | 3            | 4                                  | 2                   | 1                                     | 1                                     | 3                                     |  |

| Procs/system                                   | 2-16          | 2-16         | 2-16                               | 2-16                | 1-6                                   | 2-8                                   | 2-16                                  |  |

|                                                |               |              | Ме                                 | mory                |                                       |                                       |                                       |  |

| Virtual                                        | 512KB         | 1GB          | 1GB                                | 1GB                 | 1GB                                   | 1GB                                   | 2GB                                   |  |

| Physical                                       | 2MB           | 16MB         | 16MB                               | 256MB               | 32MB                                  | 32MB                                  | 2GB                                   |  |

| Per Board                                      | 64KB<br>384KB | 512KB<br>2MB | 2MB<br>8MB                         | 8MB<br>16MB<br>48MB | 4MB (on<br>processor<br>board)<br>8MB | 8MB (on<br>processor<br>board)<br>8MB | 32MB<br>64MB                          |  |

| Max Boards                                     | 2             | 2            | 4                                  | 2                   | 1                                     | 1                                     | 2                                     |  |

| Cycle Time                                     | 500ns/2B      | 400ns/2B     | 666 ns/8B                          | 416ns/8B            | 933ns/8B                              | 637ns/8B                              | 495ns/16B<br>(+225ns if CAM miss)     |  |

| Input Output                                   |               |              |                                    |                     |                                       |                                       |                                       |  |

| Interprocessor<br>Bus Speed                    |               | 2 x 13MB/s   | 2 x 13MB/s                         | 2 x 20MB/s          | 2 x 20MB/s                            | 2 x 20MB/s                            | 2 x 20MB/s                            |  |

| Channel Speed                                  | 4MB/s         | 5MB/s        | 5MB/s                              | 5MB/s               | 3.0MB/s                               | 4.4MB/s                               | 2 x 5MB/s                             |  |

The Tandem NonStop I was a stack-oriented 16-bit processor with virtual memory. This instruction set has evolved to an upward-compatible 32-bit-addressing machine. Program binaries from the NonStop I will run on a Cyclone. The processor implementations have been fairly conventional, using a mix of special-purpose hardware for basic arithmetic and I/O operations, along with microcode to implement higher-level functions. Two novel features are the special hardware and micro-instructions to accelerate the sending and receipt of messages on the DYNABUS. The performance of these instructions has been a key component of the success of the message-based operating system.

Memory, as originally implemented, was designed to support a 16-bit minicomputer. In 1981, designers added a 32-bit addressing scheme that provided access to

- 4 MB of code space (for users)

- multiple 127.5 MB data spaces (for users)

- 4 MB of code space (for the system)

- 1 GB (2GB for Cyclone) of virtual data space (for the system).

The code and data spaces in both the user and the system areas are logically separate from one another.

In order to make processors fail-fast, extensive error checking is incorporated in the design. Error detection in data paths typically is done by parity checking and parity prediction, while checking of control paths is done with parity, illegal state detection, and selfchecking.

Loosely coupling the processors relaxes the constraints on the error-detection latency. A processor is required to stop itself only in time to avoid sending incorrect data over the I/O bus or DYNABUS. In some cases, to avoid lengthening the processor cycle time, error detection is pipelined and does not stop the processor until several clocks after the error occurred. Several clocks of error-detection latency is permitted in the architecture, but could not be tolerated in systems with lockstepped processors or systems where several processors share a common memory. In addition, the true fail-fast character of all processors eliminates the need for instruction retry in the event of errors.

# DYNABUS INTERPROCESSOR BUS

The DYNABUS interprocessor bus is a set of two independent interprocessor buses. All components that attach to either of the buses are kept physically distinct, so that no single component failure can contaminate both buses simultaneously. Bus access is determined by two independent interprocessor bus controllers. Each of these controllers is dual-powered in the same manner as an I/O controller.

The DYNABUS controllers are not associated with, nor physically part of, any processor. Each bus has a two-byte data path and several control lines associated with it. No failed processor can independently dominate bus utilization upon failure because, to electrically transmit onto the bus, the bus controller must agree that a given processor has the right to transmit.

The original DYNABUS connected from two to 16 processors. This bus was designed with excess capacity to allow for future improvements in processor performance without redesign of the bus. The same bus was used on the NonStop II, introduced in 1980, and the NonStop TXP, introduced in 1983. The NonStop II and NonStop TXP processors can even plug into the same backplane to operate in a single system with mixed processors. A full 16-processor TXP system does not drive the bus near saturation.

A new DYNABUS was introduced with the VLX system. It provides peak throughput of 40 MB/sec, relaxes the length constraints of the bus, and has a reduced manufacturing cost due to improvements in its clock distribution. It was again overdesigned to accommodate the higher processing rates predicted for future processors. The CLX and Cyclone systems also use this bus.

For any given interprocessor data transfer, one processor is the sender and the other is the receiver. To transfer data over the DYNABUS interprocessor bus, the sending processor executes a SEND instruction. This instruction specifies the bus to be used, the intended receiver, and the number of bytes to be sent. Up to 64KB can be sent in a single SEND instruction. The sending processor continues to execute the SEND instruction until the data transfer is completed, during which time the DYNABUS interface control logic in the receiving processor is storing the data in memory. In the receiving processor, this activity occurs concurrently with program execution. Error recovery action is taken in case the transfer is not completed within a specified timeout interval.

In the DYNABUS design, the more esoteric decisions are left to the software (for example, alternate path routing and error recovery procedures); hardware, then, implements fault detection and reporting [Bartlett, 1978].

### FIBER-OPTIC EXTENSION (FOX) LINKS

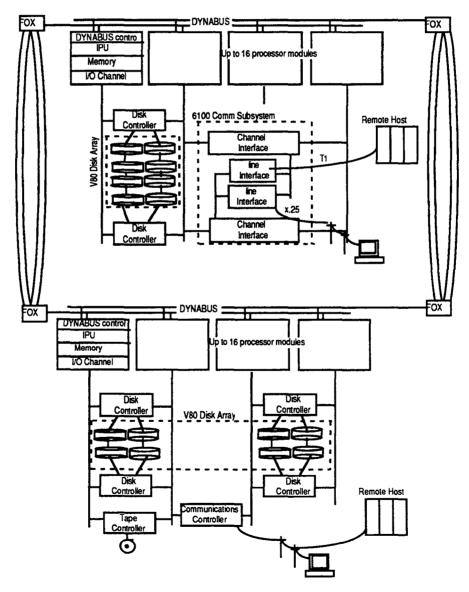

In 1983, a fiber-optic bus extension (FOX) was introduced to link systems together in a high-speed local network. FOX allows up to 14 systems of up to 16 processors each to be linked in a ring structure, for a total of 224 processors. The maximum distance between adjacent nodes was 1 Km on the original FOX and is 4 Km with FOX II, which was introduced on the VLX processor. A single FOX ring can mix NonStop II, TXP, VLX, and Cyclone processors.

The interconnection of systems by FOX links is illustrated in Figure 3. Each node in the group can accept or send data at rates of up to 4 MB/sec.

Figure 3. Tandem System Architecture of 1990

The FOX connection is based on a store-and-forward ring structure. Four fibers are connected between a system and each of its two neighbors. Each interprocessor bus is extended by a pair of fibers, which allows messages to be sent in either direction around the ring. The four paths provided between any pair of systems ensure that communication is not lost if a system is disabled (perhaps because of a power failure) or if an entire four-fiber bundle is severed.

The ring topology also has advantages over a star configuration because a ring has no central switch that could constitute a single point of failure and because cable routing is easier with a ring than with a star. In a ring structure, bandwidth increases as additional nodes are added. The total bandwidth available in a FOX network depends on the amount of passthrough traffic. In a 14-node FOX ring, if each node sends to other nodes with equal probability, the network has a usable bandwidth of 10MB/sec. With no passthrough traffic, the bandwidth increases to 24MB/second. Theoretically, an application generating 3KB of traffic per transaction, at 1,000 transactions per second, would require a FOX ring bandwidth of only 3MB/sec. In this situation, the FOX network would use less than 30% of the total available bandwidth. Transaction processing benchmarks have shown that the bandwidth of FOX is sufficient to allow linear performance growth in large multinode systems [Horst, 1985], [Englert 1989].

Fiber-optic links were chosen to solve both technical and practical problems in configuring large clusters. Fiber optics are not susceptible to electromagnetic interference, so they provide a reliable connection even in noisy environments. They also provide high-bandwidth communication over fairly large distances (4KM/hop). This lessens the congestion in the computer room and allows many computers in the same or nearby buildings to be linked. Fiber-optic cables are also flexible and of small diameter, thus easing installation.

FOX links allow computer sites to physically isolate nodes by housing them in different buildings, thereby providing a degree of fault isolation and protection against disaster. For example, a fire in the computer room in one building would not affect nodes in other buildings.

#### **DYNABUS+ FIBER-OPTIC DYNABUS EXTENSION**

With the introduction of the Cyclone system in 1989, Tandem made two additional uses of Fiber optic links; their use between peripheral controllers and Input/Output devices is described later in this chapter; their use as an interprocessor link, within a system (as compared with FOX, which is an intersystem link) is described here.

Cyclone processors are grouped into sections, each containing up to 4 processor modules. The sections may be geographically distributed up to 50 meters. Within a section, the normal (backplane) DYNABUS interface is used. Sections within a system are connected in a ring arrangement, similar to the FOX arrangement.

Individual DYNABUS+ fiber-optic links are capable of 100 Megabit/second bandpass, a good match for the 20 Megabyte/second bandpass of the DYNABUS. While increasing performance was not the major design goal of DYNABUS+, the design has resulted in additional aggregate interprocessor bus bandpass, up to 160 Megabytes/second in a system. Each section contains its own DYNABUS controllers, so message traffic local to the section can proceed concurrently with local traffic in other sections. In addition, intersection traffic can proceed concurrently on the multiple fiber-optic links.

The DYNABUS+ system is transparent to all levels of software except the maintenance subsystem (described later in this chapter). The system is self-configuring when power is first applied; Diagnostic Data Transceiver (DDT) processors within each cabinet determine the configuration and routing rules. In the event of a failure of any of the fiber-optic links or interface logic boards, the system reconfigures itself, establishes new routing paths, and notifies the maintenance subsystem.

In addition, a VLX interface to DYNABUS+ allows intermixing VLX and Cyclone processor modules within a system. This feature allows an existing VLX customer to add Cyclone processors to a system, providing a smooth upgrade path.

# SYSTEM POWER AND PACKAGING

Online maintenance is a key factor in the design of the physical packaging and the power distribution of Tandem systems. Traditional designs assumed that maintenance could be done with the equipment offline and powered off.

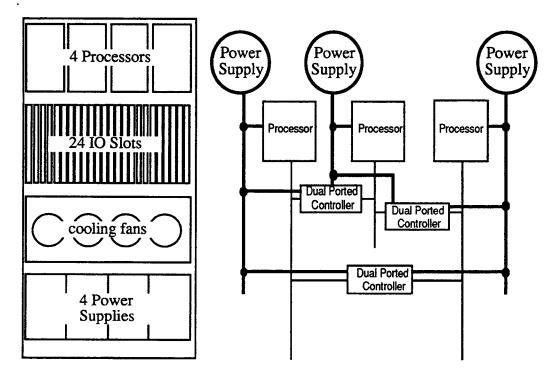

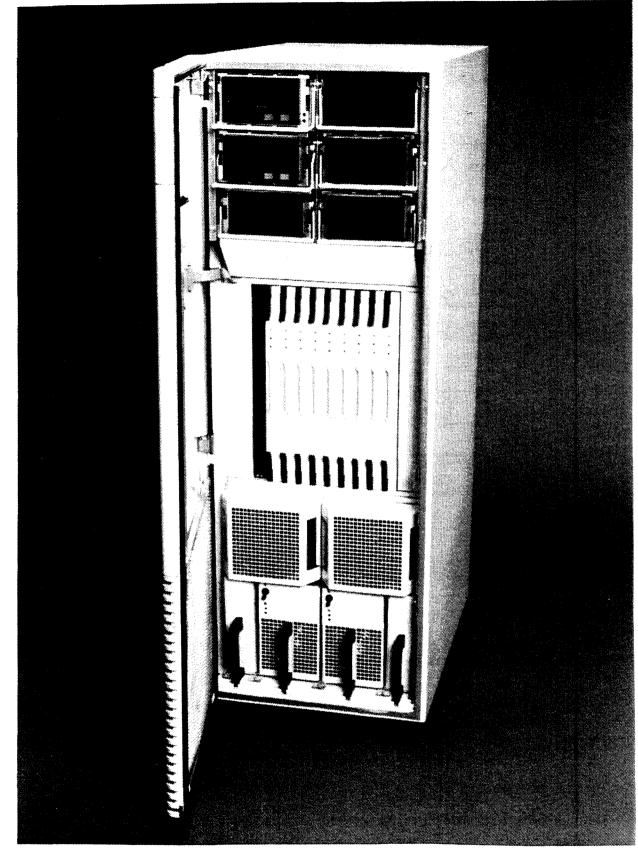

The VLX system cabinet, shown in Figure 4, is divided into four sections: the upper card cage, the lower card cage, the cooling section, and the power supply section. The upper card cage contains up to four processors, each with its own I/O channel and private memory. The lower card cage contains up to 24 I/O controller printed circuit (PC) cards, where each controller consists of one to three PC cards. The cooling section consists of four fans and a plenum chamber that forces laminar air flow through the card cages. The power supply section contains up to four power supply modules. Multiple cabinets can be bolted together.

The system can accommodate a maximum of 16 processor modules on a DYNABUS pair. Each processor module--consisting of an IPU, memory, DYNABUS control, and I/O channel--is powered by an associated power supply. The power distribution system is shown in Figure 4.

Figure 4. NonStop VLX System Cabinet (left) and power distribution (right)

If a failed processor module is to be replaced, its associated power supply is shut off, the module is replaced, and the power supply is turned on. Each card cage slot in the I/O card cage is powered by two different power supplies. Each of the I/O controllers is connected via its dual-port arrangement to

two processors. Each of those processors has its own power supply; usually, but not necessarily, those two supplies are the ones that power the I/O controller (see Figure 4 again). Thus, if a power supply fails or if one is shut down to repair a processor, no I/O controllers are affected.

I/O controllers draw current from two supplies simultaneously. If a power supply fails, the second power supply provides all the current for a given controller. There is also circuitry to provide for a controlled ramping of current draw on insertion, removal, turn-on, and turn-off. This circuitry smooths power demands from a given supply, masking a potential momentary dip in supply voltage.

# **EVOLUTIONARY CHANGES**

Processor architecture has evolved to keep pace with technology. These improvements include:

- Expansion to 1 GB of virtual memory (NonStop II system) and to 2 GB (Cyclone system)

- Incorporation of cache memory (TXP system)

- Expansion of physical memory addressability to 256 MB (VLX system) and to 2 GB (Cyclone system)

- Incorporation of separate instruction and data caches (Cyclone system)

- Incorporation of superscalar architecture (Cyclone system) [Horst, Harris, and Jardine, 1990]

- Incorporation of an independent instruction fetch unit with dynamic branch prediction (Cyclone system).

Technological improvements include:

- · Evolution from core memory to 1Mb dynamic RAMs

- Evolution from Schottky TTL (NonStop I and II systems) to Programmable Array Logic (TXP system) [Horst and Metz, 1984] to bipolar gate arrays (VLX system) to silicon-compiled custom CMOS (CLX system) [Lenoski, 1988].

The Tandem multiprocessor architecture allows a single processor design to cover a wide range of processing power. Having processors of varying power adds another dimension to this flexibility. For instance, for approximately the same processing power, a customer can choose a 2-processor VLX system, a 3-processor TXP system, or a 4-processor CLX-700 system. Having a range of processors extends the range of applications from those sensitive to low-entry price to those with extremely high-volume processing needs. In a different performance range, the customer may chose a four-processor Cyclone system or a 16-processor VLX system.

#### PERIPHERALS

In building a fault-tolerant system, the entire system, not just the processor, must have the basic faulttolerant properties of dual paths, modularity, and fail-fast design, as well as good price/performance. Many improvements in all of these areas have been made in peripherals and in the maintenance subsystem.

The basic architecture provides the ability to configure the I/O system to allow multiple paths to each I/O device. With dual-ported controllers and dual-ported peripherals, there are actually four paths to each device. When disks are mirrored, there are eight paths that can be used to read or write data.

In the configurations illustrated in Figure 3, there are many paths to any given disk--typically two controllers access each disk and each controller is attached to two processor channels. Software is used to mirror disks; that is, data is stored on two disks so that if one fails, the data is still available on the other disk. Consequently, the data can be retrieved regardless of any single failure of a disk drive, disk controller, power supply, processor, or I/O channel.

The original architecture did not provide as rich an interconnection scheme for communications and terminals. The first asynchronous terminal controller was dual-ported and connected to 32 terminals. The terminals themselves were not dual-ported, so it was not possible to configure the system in a way to withstand a terminal controller failure without losing a large number of terminals. The solution for critical applications was to have two terminals nearby that were connected to different terminal controllers.

# The 6100 Communication Subsystem

The 6100 Communications Subsystem, introduced in 1983, helped reduce the impact of a failure in the communications subsystem. The 6100 consists of two dual-ported Communications Interface Units (CIUs) that communicate with I/O buses from two different processors (see Figure 3). Individual Line Interface Units (LIUs) connect to both CIUs, and to the communications line or terminal line. With this arrangement, CIU failures are completely transparent, and LIU failures result in the loss of only the attached line or lines. An added advantage is that each LIU can be downloaded with a different protocol in order to support different communications environments and to offload protocol interpretation from the main processors.

The 6100 Communications Subsystem is configured to have up to 45 LIUs. Each LIU can support up to 19.2 Kb/s of asynchronous communication or 64 Kb/s of synchronous communication. Redundant power supplies and cooling fans provide an extra margin of fault tolerance and permit online replacement of components.

### Disk Subsystem

Modularity is standard in peripherals; it is common to mix different types of peripherals to match the intended application. In online transaction processing (OLTP), it is desirable to independently select increments of disk capacity and of disk performance. OLTP applications often require more disk arms per megabyte than is provided by traditional large (14 inch) disks. This may result in customers buying more megabytes of disk than they need in order to avoid queuing at the disk arm.

In 1984, Tandem departed from traditional disk architecture by introducing the V8 disk drive. The V8 was a single cabinet that contained up to eight 168-MB, 8-inch Winchester disk drives in six square feet of floor space. Using multiple 8-inch drives instead of a single 14-inch drive provided more access paths and less wasted capacity. The modular design was more serviceable, because individual drives could be removed and replaced online. In a mirrored configuration, system software automatically brought the replaced disk up-to-date while new transactions were underway.

Once a system can tolerate single faults, the second-order effects begin to become important in system failure rates. One category of compound faults is the combination of a hardware failure and a human error during the subsequent human activity of diagnosis and repair. The V8 reduced the likelihood of such compound hardware-human failures by simplifying servicing and eliminating preventative maintenance.

In fault-tolerant systems design, keeping down the price of peripherals is even more important than in traditional systems. Some parts of the peripheral subsystem must be duplicated, yet they provide little or no added performance.

For disk mirroring, two disk arms give better read performance than two single disks because the seeks are shorter and because the read work is spread evenly over the two servers [Bitton, 1988, 1989]. Write operations, on the other hand, do demand twice as much channel and controller time. Also, mirroring does double the cost per megabyte stored. To reduce the price per megabyte of storage, the XL8 disk drive was introduced in 1986. The XL8 had eight 9-inch Winchester disks in a single cabinet and had a total capacity of 4.2GB. As in the V8 drive, disks within the same cabinet could be mirrored,

saving the costs of added cabinetry and floor space. Also, like the V8, the reliable sealed media and modular replacement kept maintenance costs low.

The V80 disk storage facility replaced the V8 in 1988. Each of the V80's eight 8-inch disk drives has a formatted capacity of 265 MB. Thus, each cabinet can hold 2.7 GB of unformatted storage, or 2.1 GB of formatted storage. Externally, the V80 resembles the V8, housed in a single cabinet that occupies six square feet of floor space. The internal design of the V80, however, extends the capacity and reliability of the V8 with a fully-checked interface to the drives. Furthermore, the design reduces by a factor of five the number of external cables and connectors between the storage facility and the control unit.

The disk drive interface is based on the emerging industry-standard IPI-2 interface design, which has parity checking on data and addressing to ensure the integrity of data and commands. (The previous SMD-based design provided only data parity.) IPI's parallel and batched data and command interface between the disks and their controller allow higher data transfer rates (2.4 MB/sec) and reduced interrupts.

A radial connection between the controller and the drives eliminates possible drive interaction that could occur with conventional bus structures. The five-fold reduction in the number of external cables and connections is achieved by placing the control logic in the disk cabinet. Within the cabinet, a new interconnect design has reduced by a factor of five the number of internal cables and connections.

In 1989, the XL80 replaced the XL8 in similar fashion, doubling the storage capacity per drive, and also moving to an IPI-2 storage interface. In addition, the XL80 cabinet contains sensors for inlet air temperature, power supply and board voltages, and fan operation; this information is polled periodically by the cabinet's maintenance subsystem and reported to the peripheral controller when an exception condition exists. A fully-configured XL80 disk subsystem, including storage modules, power supplies, and cooling fans, appears in Figure 5.

# **Peripheral Controllers**

Peripheral controllers have fail-fast requirements similar to processors. They must not corrupt data on either of their I/O buses when they fail. If possible, they must return error information to the processor when they fail. In terms of peripheral fail-fast design, the Tandem contribution has been to put added emphasis on error detection within the peripheral controllers. An example is a VLSI tape controller which uses dual, lockstepped Motorola 68000 processors with compare circuits to detect errors. It also contains totally self-checked logic and self-checking checkers to detect errors in the ad-hoc logic portion of the controller.

Beyond this contribution, the system software uses "end-to-end" checksums generated by the high-level software. These checksums are stored with the data and are recomputed and rechecked when the data is reread.

The single-board controller supporting the V80 and XL80 disks uses CMOS VLSI technology. The controller is managed by dual, lockstepped Motorola 68010 microprocessors that provide sophisticated error-reporting and fault-isolation tools. The controller is contained on a single board; thus, it requires only half the input/output slots of previous controllers.

Other efforts to reduce peripheral prices include the use of VLSI gate arrays in controllers to reduce part counts and improve reliability and use of VLSI to integrate the standalone 6100 communications subsystems into a series of single-board controllers.

The Tandem evolution of fault tolerance in peripherals is summarized in Table 2.

Figure 5. XL80 Disk Subsystem (Front View)

13

| Table 2. Tandem Evolution of Peripheral Fault Tolerance |                                              |                                                                                                      |  |  |  |

|---------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Year                                                    | Product                                      | Contribution                                                                                         |  |  |  |

| 1976                                                    | NonStop I System                             | Dual-ported controllers,<br>single-fault-tolerant I/O system                                         |  |  |  |

| 1 <b>97</b> 7                                           | NonStop I System                             | Mirrored and dual-ported disks                                                                       |  |  |  |

| 1982                                                    | INFOSAT                                      | Fault-tolerant satellite communications                                                              |  |  |  |

| 1983                                                    | 6100 Communications<br>Subsystem             | Fault-tolerant communications subsystem                                                              |  |  |  |

| 1983                                                    | FOX                                          | Fault-tolerant, high-speed, fiber-optic LAN                                                          |  |  |  |

| 1984                                                    | V8 Disk Drive                                | Eight-drive, fault-tolerant disk array                                                               |  |  |  |

| 1985                                                    | 3207 Tape Controller                         | Totally self-checked VLSI tape controller                                                            |  |  |  |

| 1 <b>9</b> 85                                           | XL8 Disk Drive                               | Eight-drive, high-capacity/low-cost, fault-tolerant disk array                                       |  |  |  |

| 1986                                                    | TMDS                                         | Fault-tolerant maintenance system                                                                    |  |  |  |

| 1987                                                    | CLX                                          | Fault-tolerant system that is 98% user-serviceable                                                   |  |  |  |

| 1988                                                    | V80 Storage Facility                         | Reduced disk cabling and fully-checked disk interfaces                                               |  |  |  |

| 1988                                                    | 3120 Disk Controller                         | Totally self-checked VLSI disk controller                                                            |  |  |  |

| 1 <b>9</b> 89                                           | XL80 Storage Facility                        | Reduced disk cabling, fully-checked disk interfaces,<br>environmental monitoring within disk cabinet |  |  |  |

| 1989                                                    | Fiber-Optic Interconnect<br>for V80 and XL80 | Reduced cabling to a minimum, reduced transmission errors                                            |  |  |  |

### **PROCESSOR MODULE IMPLEMENTATION DETAILS**

The following sections outline the implementation details of each of the Tandem processors summarized in Table 1.

#### NonStop I

The NonStop I processor module, introduced in 1976, included a 16-bit IPU, main memory, DYNABUS interface, and an I/O channel. Physically, the IPU, I/O channel, and DYNABUS control consisted of two PC boards that measure 16 inches by 18 inches, each containing approximately 300 integrated circuit packages. These boards employed Schottky TTL circuitry.

The processor module was viewed by the user as a 16-bit, stack-oriented processor, with a demand paging, virtual memory system capable of supporting multiprogramming.

The IPU was a microprogrammed processor consisting of: (1) an execution unit with ALU, shifter, register stack, and Program counter, (2) a microprogram sequencer with 1024 32-bit words stored in ROM, (3) address translation maps supporting system code and data, and current user code and data segments, (4) up to 512 KB of main memory, (5) 96 KB memory boards with single error correction and double error detection, and (5) battery backup for short-term main memory ride-through of power outages of up to 4 hours.

The heart of the I/O system is the I/O channel. In the NS I, all I/O was done on a direct memory access (DMA) basis. The channel was a microprogrammed, block-multiplexed channel; individual controllers determine the block size.

The channel did not execute channel programs, as on many systems, but did transfer data in parallel with program execution. The memory system priority always permitted I/O accesses to be handled before IPU or DYNABUS accesses. The maximum I/O transfer was 4 KB.

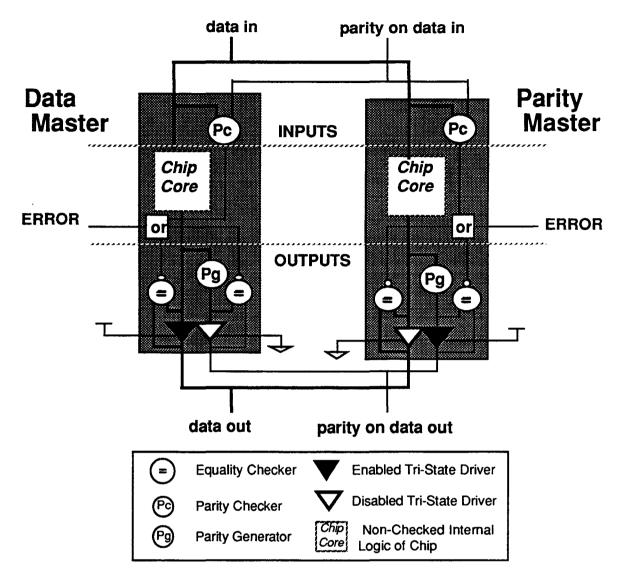

#### **Dual-Port** Controllers

The dual-ported I/O device controllers provided the interface between the NonStop I I/O channel and a variety of peripheral devices using distinct interfaces. While these I/O controllers were vastly different depending on the devices they interfaced to, there was a commonality among them that fitted them into the NonStop I architecture.

Each controller contained two independent I/O channel ports implemented by IC packages that were physically separate from each other so that no interface chip could simultaneously cause failure of both ports. Logically, only one of the two ports was active. The other port was utilized only in the event of a path failure to the primary port. An "ownership" bit, as illustrated in Figure 6, indicated to each port if it was the primary port or the alternate.

Ownership changed only when the operating system issued a TAKE OWNERSHIP I/O command. Executing this special command caused the I/O controller to swap its primary and alternate port designation and to do a controller reset.

Any attempt to use a controller that was not owned by a given processor resulted in an ownership violation. If a processor determined that a given controller was malfunctioning on its I/O channel, it could issue a DISABLE PORT command that logically disconnected the port from that I/O controller. This disconnection did not affect the ownership status. Thus, if the problem was within the port, the alternate path could be used; but if the problem was in the common portion of the controller, ownership was not forced on the other processor.

,

Figure 6. Ownership Circuitry and Logic

# Fault-Tolerant I/O Considerations

The I/O channel interface consisted of a two-byte data bus and control signals. All data transferred over the bus was parity-checked in both directions, and errors were reported through the interrupt system. A watchdog timer in the I/O channel detected if a nonexistent I/O controller was addressed, or if a controller stopped responding during an I/O sequence.

The data transfer byte count word in the channel command entry contained four status bits, including a protect bit. When this bit was set on, only output transfers were permitted to this device.

Because I/O controllers were connected between two independent I/O channels, it was very important that word count, buffer address, and direction of transfer be controlled by the processor instead of within the controller. If that information were to be kept in the controller, a single failure could fail both processors attached to it. Consider what would happen if a byte count register were located in the controller and was involved a situation where the count did not decrement on an input transfer. It would be possible to overwrite the buffer and render system tables meaningless. The error would propagate to the other processor upon discovery that the first processor was no longer operating.

Other error conditions that the channel checked for were violations of I/O protocol, attempts to transfer to absent pages (it is the operating system's responsibility to "lock down" the virtual pages used for I/O buffering), uncorrectable memory errors, and map parity errors.

# NonStop II

The NonStop II was a compatible extension of the NonStop I. The major changes from the NonStop I processor module were the introduction of a 32-bit addressing scheme and a Diagnostic Data Transceiver (DDT) processor. The software for the NonStop II system was upward-compatible with the NonStop I system. Thus, application programs written for the NonStop I system could be run on the NonStop II system.

The IPU was implemented using Schottky TTL logic using a microinstruction cycle time of 100 nsec. Instructions were added to support 32-bit extended addressing. An optional floating-point instruction set was also added for high-speed scientific calculations--eventually, these instructions became a standard part of the instruction set. The instruction sets were implemented in microcode in a high-speed control store, which had 8K 32-bit words of loadable storage and 1K words of read-only storage. The loadable part of the control store was initialized when the operating system was loaded. Before loading the control store, the system performed a set of diagnostic routines to verify that the processor was operating correctly.

The processor's internal data paths and registers were parity-checked to ensure data integrity. The IPU featured a two-stage pipeline that allowed it to fetch the next instruction while executing the current instruction.

Memory boards for the NonStop II system contained 512KB, 2MB or 4MB of storage. Up to four of these boards, in any combination, could reside in one processor for a maximum of 16MB. A fully-configured 16-processor system allowed up to 64 boards with a total of 256MB of memory. The memory access time was 400 nsec.

Each memory word was 22 bits long. Six bits of the word provide an error correction code that enabled the system to correct any single-bit error and detect any double-bit error. The error- correction code also checked the address sent from the IPU to ensure that the memory access was valid.

#### I/O Channel

Each processor module contained a separate processor dedicated to I/O operations. Because the I/O processor operated independently from the IPU, I/O transfers were extremely efficient and required only a minimum of IPU intervention. The channel was a burst multiplexor.

Every I/O device controller was buffered, which allowed data transfers between main memory and the controller buffer to occur at full memory speed. I/O transfers had a maximum length of 64KB. The high-speed I/O channels used burst-multiplexed direct memory access to provide transfer rates of up to 5 MB/s. Thus, the aggregate burst I/O rate of a fully-configured 16-processor system was 80 MB/s.

The I/O processor supported up to 32 device controllers. Depending on the type, device controllers could support up to eight peripheral units. Therefore, as many as 256 devices could be connected to a single processor. Multipoint communication lines were treated as a single device, so each processor could support very large terminal configurations.

I/O device controllers were intelligent devices. This intelligence allowed them to relieve the central processing unit of many routine functions such as polling synchronous terminals, checking for data transmission errors, and so forth.

#### **Diagnostic Data Transceiver (DDT)**

The Diagnostic Data Transceiver (DDT) was a separate microprocessor included as part of each processor module. The DDT provided two distinct functions:

- The DDT allowed communication between a processor module and the Operations and Service Processor (OSP), which supports both operational and maintenance functions such as running diagnostics. More about the OSP appears under Maintenance Facilities and Practices, later in this chapter.

- The DDT monitored the status of the central processing unit, DYNABUS interface, memory, and the I/O processor, and reported any errors to the OSP.

. . .

#### Virtual Memory

The virtual memory addressing scheme, introduced by the NonStop II processor, is used by all subsequent processors. It converted the system from 16-bit addressing to 32-bit addressing. This addressing is supported by the instruction set, and is based on segments that contain from 1 to 64 pages each. A page contains 2048 bytes. Each processor can address up to 8192 segments, which provides it with a billion bytes (1 GB) of virtual memory address space (later extended to 2 GB on the Cyclone processor, introduced in 1989).

The instruction set supports standard and extended addressing modes. The standard 16-bit addressing mode provides high-speed access within the environment of an executing program. The extended 32-bit addressing mode allows access to the entire virtual memory space by privileged processes. Programs written in Pascal, C, COBOL85, and the Transaction Application Language (TAL), can use extended addressing for access to large data structures.

The instruction set supports two types of extended addressing: absolute and relocatable. Absolute extended addressing is available only to privileged users such as the operating system itself. Absolute addresses can address any byte within the virtual memory. Relocatable extended addresses are available to all users. This form of addressing can reference any byte of the current process's data space as well as one or more private relocatable extended data segments. Each extended data segment can contain up to 127.5MB.

To provide efficient virtual-to-physical address translations, each NonStop II processor included 1024 high-speed map registers. The memory maps contained absent, dirty, and referenced bits to help the software manage virtual memory.

### Maintenance

A major feature of the NonStop II system was the Operations and Service Processor (OSP) located in a console supplied with the system. In addition to serving as an operations interface for communication with the system, the OSP was a powerful diagnostic and maintenance tool. The OSP is described later in this section, under Maintenance Facilities and Practices.

# **TXP PROCESSOR**

While the NonStop II system extended the instruction set of the NonStop I system to handle 32-bit addressing, it did not efficiently support that addressing mode. The existing 5MB/s I/O channel and 26MB/s DYNABUS interprocessor bus offered more than enough bandwidth to handle a processor with two to three times the performance. The existing packaging had an extra processor card slot for future enhancements, and the existing power supplies could be reconfigured to handle a higher-powered processors. The NonStop TXP processor module, introduced in 1983, was designed in this environment.

The main problems concerned designing a new microarchitecture that would efficiently support the 32bit instructions at much higher speeds, with only 33% more printed circuit board area and the existing backplane. This design involved eliminating some features that were not critical to performance and finding creative ways to save area on the PC board, including strategic uses of programmable array logic and an unusual multilevel control-store scheme.

The performance improvements in the NonStop TXP system were attained through a combination of advances in architecture and technology. The NonStop TXP architecture used dual 16-bit data paths, three levels of macroinstruction pipelining, 64-bit parallel access from memory, and a large cache (64KB

per processor). Additional performance gains were obtained by increasing the hardware support for 32bit memory addressing.

The machine's technology includes 25-nsec programmable array logic, 45-nsec 16K static RAM chips, and Fairchild Advanced Schottky Technology (FAST) logic. With these high-speed components and a reduction in the number of logic levels in each path, a 12-MHz (83.3 nsec per microinstruction) clock rate could be used.

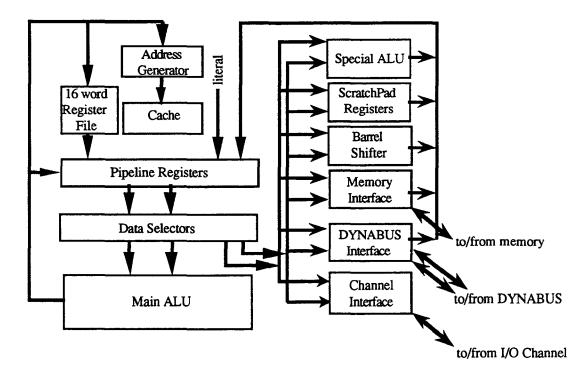

The TXP's dual data-path arrangement increased performance through added parallelism, as shown in Figure 7. A main arithmetic-and-logic unit operation could be performed in parallel with another operation done by one of several special modules. Among these modules were a second ALU to perform both multiplications and divisions, a barrel shifter, an array of 4,096 scratchpad registers, an interval timer, and an interrupt controller. Other modules provide interfaces among the IPU and the interprocessor bus system, I/O channel, main memory, and a diagnostic processor.

Figure 7. Parallel Data Paths of the TXP processor.

The selection of operands for the main ALU and the special modules was done in two stages. In the first stage, data was accessed from the dual-ported register file or external registers and placed into two of the six registers. During the same cycle, the other four pipeline registers were loaded with cache data, a literal constant, the results of the previous ALU operation, and the result of the previous special-module operation.

In the second stage, one of the six pipeline registers was selected for each of the main ALU inputs and another one of these registers was selected for each special-module operand. Executing the register selection in two stages, so that the register file could be two-ported rather than four-ported, greatly reduced the cost of multiplexers and control storage; the flexibility in choosing the required operands was unimpeded. An example of the way microcode used the parallel data paths is shown in Table 3. This example shows the inner loop of the COMPARE-BYTE instruction. Each of the dual ALUs in the TXP system extracted one byte; then the extracted bytes were compared. This operation took two clock cycles on the TXP system, but would require three if the extract operations were not done simultaneously.

| Clock | NonSto               | Traditional<br>Architecture |                |

|-------|----------------------|-----------------------------|----------------|

| Cycle | Main ALU Special ALU |                             |                |

| 1     | Extract Byte 1       | Extract Byte 2              | Extract Byte 1 |

| 2     | Compare Bytes        | -                           | Extract Byte 2 |

| 3     | (Repeat)             | (Repeat)                    | Compare Bytes  |

| 4     | -                    | _                           | (Repeat)       |

Table 3. Compare Byte Instructions (Inner Loop)

The dual 16-bit data paths tended to require fewer cycles than a single 32-bit path when manipulating byte and 16-bit quantities. However, the paths did require slightly more cycles when manipulating 32-bit quantities. A 32-bit add took two cycles rather than one, but the other data path was free to use the two cycles to perform either another 32-bit operation or two 16-bit operations. Measurements of transaction-processing applications showed that the frequencies of 32-bit arithmetic were insignificant relative to data-movement and byte-manipulation instructions, which were handled more efficiently by the dual data paths than by a single 32-bit data path. Most instructions include enough parallelism to let the microcode make effective use of both data paths.

To control the large amount of parallelism in the NonStop TXP processor, a wide control-store word was required. The effective width of the control store was over 100 bits. To reduce the number of RAMs required, the control store was divided between a vertical control store of 8K 40-bit words and a horizontal control store of 4K 84-bit words. The vertical control store controlled the first stage of the microinstruction pipeline and included a field that addressed the horizontal control store, whose fields controlled the pipeline's second stage. Lines of microcode that required the same or similar horizontal controls could share horizontal control-store entries.

Unlike microprocessor-based systems that have microcode fixed in read-only memory, the NonStop TXP system microcode was implemented in RAM so that it could be changed along with normal software updates and so that new performance-enhancing instructions could be added. Because instructions were pipelined, the TXP processor could execute its fastest instructions in just two clock cycles (167 nsec). The processor could also execute frequently-used load and branch instructions in only three clock cycles (250 nsec).

Each NonStop TXP processor had a 64KB cache holding both data and code. A 16-processor NonStop TXP system had a full megabyte of cache memory. To determine the organization of the cache, a number of measurements were performed on a NonStop II system using a specially-designed hardware monitor. The measurements showed that higher cache hit ratios resulted with a large, simple cache (directly mapped) than with a smaller, more complex cache (organized as two-way or four-way

associative). Typical hit ratios for transaction processing on the NonStop TXP system fell in the range of 96% to 99%.

Cache misses were handled in a firmware subroutine rather than by the usual method of adding a special state machine and dedicated data paths for handling a miss. Because of the large savings in cache hardware, the cache could reside on the same board as the primary data paths. Keeping these functions proximal reduced wiring delays, contributing to the fast 83.3nsec cycle time.

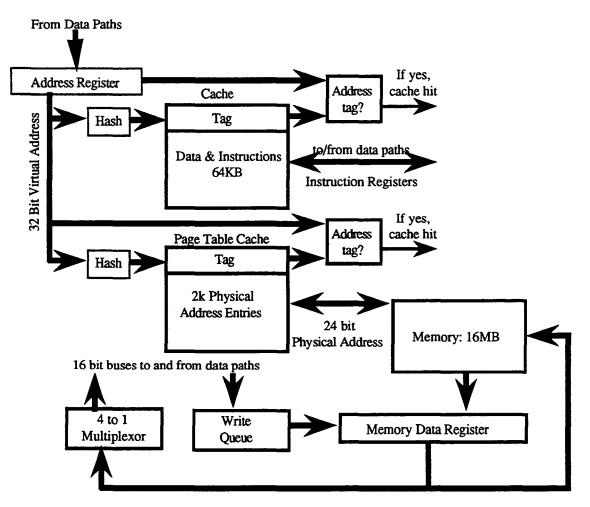

The cache was addressed by the 32-bit virtual address rather than by the physical address, thus eliminating the extra virtual-to-physical translation step that would otherwise be required for every memory reference. The virtual-to-physical translation, needed to refill the cache on misses and to store through to memory, was handled by a separate page table cache that held mapping information for as many as 2,048 pages of 2 KB each (see Figure 8).

Figure 8. TXP Memory Access

A cache memory by itself does not necessarily boost a processor's performance significantly. It is of little use for the cache to provide instructions and data at a higher rate than the rest of the IPU can process. In the TXP processor, the cache's performance was tuned to provide instructions and data at a

rate consistent with the enhancements to instruction processing provided by increased pipelining and parallelism.

# Manufacturing and Testing

The NonStop TXP processor was implemented on four large PC boards using high-speed FAST logic, PALs, and high-speed static RAMs. Each processor module had from one to four memory boards. Each memory board contains up to 8MB of error-correcting memory. A 16-processor NonStop TXP system could therefore contain up to 256MB of physical memory.

The NonStop TXP system was designed to be easy to manufacture and efficient to test. Data and control registers were implemented with shift registers configured into several serial-scan strings. The scan strings were valuable in isolating failures in field-replaceable units. This serial access to registers also made board testing much faster and more efficient because the tester could directly observe and control many control points. A single custom tester was designed for all four IPU boards and for the memory-array board.

# VLX PROCESSOR MODULE

The VLX processor module combines advanced VLSI technology with the fault-tolerant features of its predecessors. This processor module uses ECL gate array technology to implement its dual data path structure and other extensions to the TXP system. These features include:

- Dual interleaved control store

- 83.3 nanosecond cycle time

- 64 KB direct mapped, store-through cache with 16-byte block size

- Hardware cache fill

- 256 MB of physical memory addressing

- Up to 96 MB of physical memory with 48 MB memory boards

- Online power and temperature monitoring

- Four-stage instruction pipeline, supporting single clock instruction execution

- Dual 20 MB/sec DYNABUS interprocessor bus

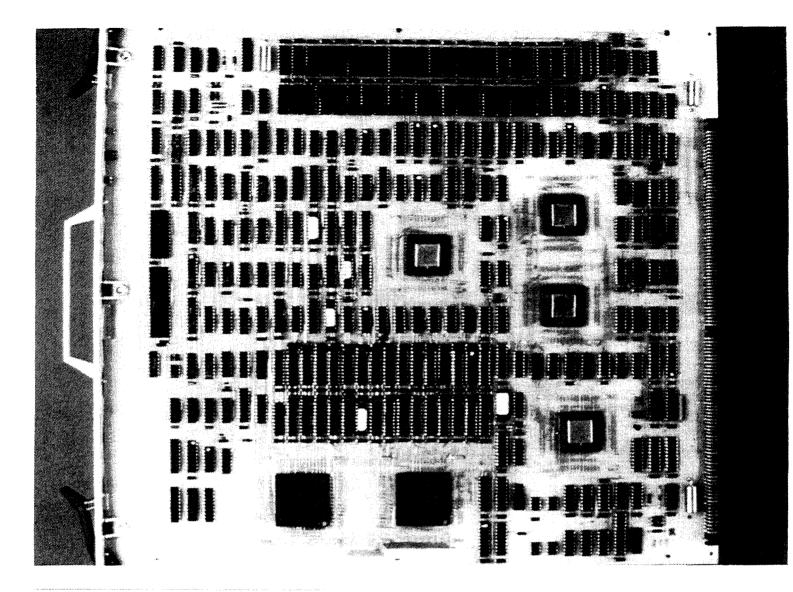

One of the VLX processor module's printed circuit boards appears in Figure 9. The VLX IPU uses 32-bit native addressing and 64-bit main memory transfers to improve upon the transaction throughput of its predecessors, move large amounts of data, and lower the cost per transaction. Failed component sparing in cache memory allows a single malfunctioning component to be replaced by means of a logical switch to a spare--and thus, a single point of failure does not require a service call.

Chips in the VLX processors contain up to 20,000 circuits, producing modules with over three times the density of the TXP processor. This increased density adds functions that enhance error checking and fault correction, as well as performance. By making it possible to reduce the number of components and interconnections, the increased density improves both performance and reliability.

VLX processor gate arrays use Emitter-Coupled Logic (ECL) for enhanced internal performance, and Transistor-to-Transistor Logic (TTL) for input/output functions. Each VLX processor includes 31 ECL/TTL gates arrays spread over only two modules.

A major goal of the VLX processor was to reduce the cost of servicing the system. This goal was accomplished in several ways, as described below.

Figure 9. Printed Circuit Board from VLX Processor Module

Traditional mainframe computers have error-detection hardware as well as hardware that allows instructions to be retried after a failure. This hardware is used both to improve availability and to reduce service costs. The Tandem architecture does not require instruction retry for availability; processors can be fail-fast. The VLX processor is the first Tandem processor to incorporate a kind of retry hardware, primarily to reduce service costs.

In the VLX processor, most of the data path and control circuitry is in high-density gate arrays, which are extremely reliable. This design leaves the high-speed static RAMs in the cache and the control store as the major contributors to processor unreliability. Both the cache and the control store are designed to retry intermittent errors, and both have spare RAMs that can be switched in to continue operating despite a hard RAM failure [Horst, 1989].

The cache provides store-through operation, so there is always a valid copy of cache data in main memory. A cache parity error just forces a cache miss, and the correct data is refetched from memory. The microcode keeps track of the parity error rate; when this rate exceeds a threshold, the microcode switches in the spare RAM.

The VLX control store has two identical copies to allow a two-cycle access of each control store starting on alternate cycles. The second copy of control store is also used to retry an access in case of an intermittent failure in the first copy. Again, the microcode switches in a spare RAM online once the error threshold is reached.

Traditional instruction retry was not included due to its high cost and complexity relative to the small improvement in system MTBF it would yield.

There is also parity checking on all data paths, single-bit error correction and double-bit error detection on data in memory, as well as single-bit error detection on addresses. Bus control lines are checked for line errors, and hardware consistency checks are used throughout the system.

Each processor contains a microprocessor-based diagnostic interface, which ensures the processor is functioning properly before the operating system receives control. Pseudo-random scan diagnosis is conducted to provide a high-level of coverage and a short execution time. Correct operation of the processor is verified before processing begins.

#### Maintenance

For the VLX system, the Tandem Maintenance and Diagnostic System (TMDS) replaced the Operations and Service Processor (OSP) used on the NonStop II and TXP processors. Information about TMDS appears later in this chapter, under Maintenance Facilities and Practices.

# **CLX PROCESSOR MODULE**

The CLX system was designed to fill the need for a low-cost distributed system. The design goal was to provide user serviceability, modular design, and fault tolerance with lower service and maintenance costs.

The CLX is based on a custom CMOS chip set developed using silicon compilation techniques [Lenoski, 1988]. The original CLS-600 processor was introduced in 1987 and is based on  $2.0\mu$  CMOS. The silicon compiler allowed the processor chip to be retargeted into  $1.5\mu$  CMOS for the CLX-700. The CLX-700, introduced less than 18 months after the 600, raised performance by 50%. While further process retargeting will yield even faster CLX's in the future, the performance numbers given in this section are for the CLX-700.

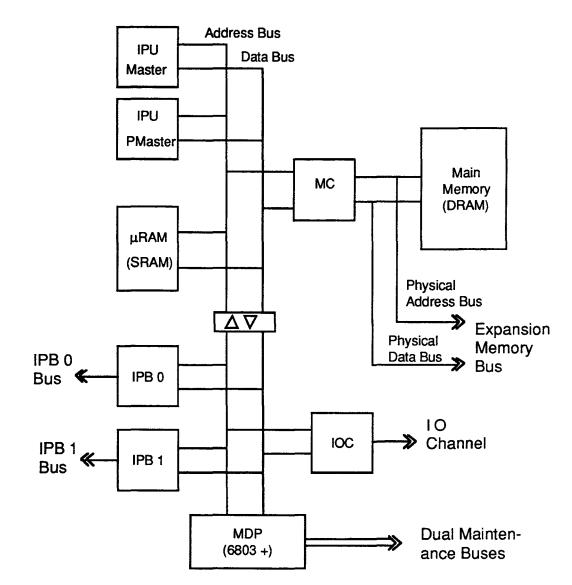

All CLX processors have a similar micro-architecture that integrates the features of both traditional board-level minicomputers and high-performance VLSI microprocessors. This hybrid design incorporates several novel structures, including a single static RAM array that serves three functions: writeable control store, data cache, and page table cache. The processor also features intensive fault checking to promote data integrity and fault-tolerant operation.

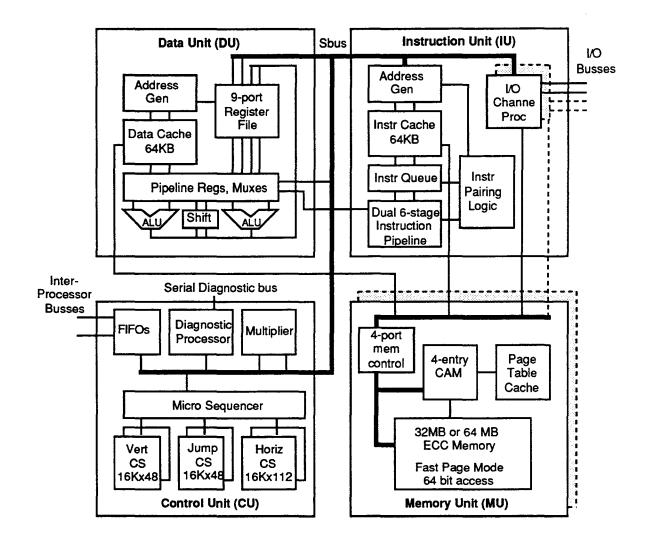

A fully-equipped, single-cabinet CLX system contains two processor boards with optional expansion memory, six I/O controllers, five 145MB disk drives, and one cartridge tape drive. Dual power supplies and cooling fans are also included in the cabinet. The entire system operates within the power, noise, and size requirements of a typical office environment. To expand the system, the customer simply adds more I/O or processor cabinets to the basic configuration. The CLX system architecture appears in Figure 10. A view of the actual cabinet appears in Figure 11.

As with the other Tandem processors, each processor communicates with other processors over two interprocessor buses (IPBs). Each bus operates synchronously on 16-bit wide data, and each provides a

peak bandwidth of 20MB/sec. The two buses transfer data independently of one another, providing a total bandwidth of 40 MB/sec for a maximum of eight processors.

Figure 10. CLX System Architecture

Processors communicate with I/O devices either through a local I/O bus or through the IPB to another processor and its I/O bus. Each processor contains a single asynchronous, burst-multiplexed I/O bus that transfers data at a maximum rate of 4.4 MB/s to a maximum of 16 controllers. As with the other processors, these controllers are dual-ported and can be driven by either of the processors to which they are attached.