# [537] Threads

Chapters 26 Tyler Harter 10/01/14

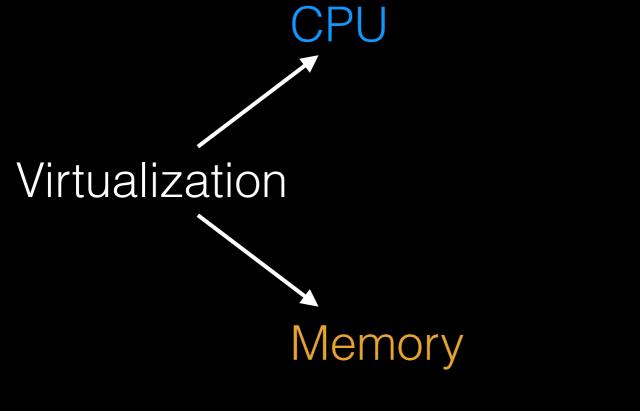

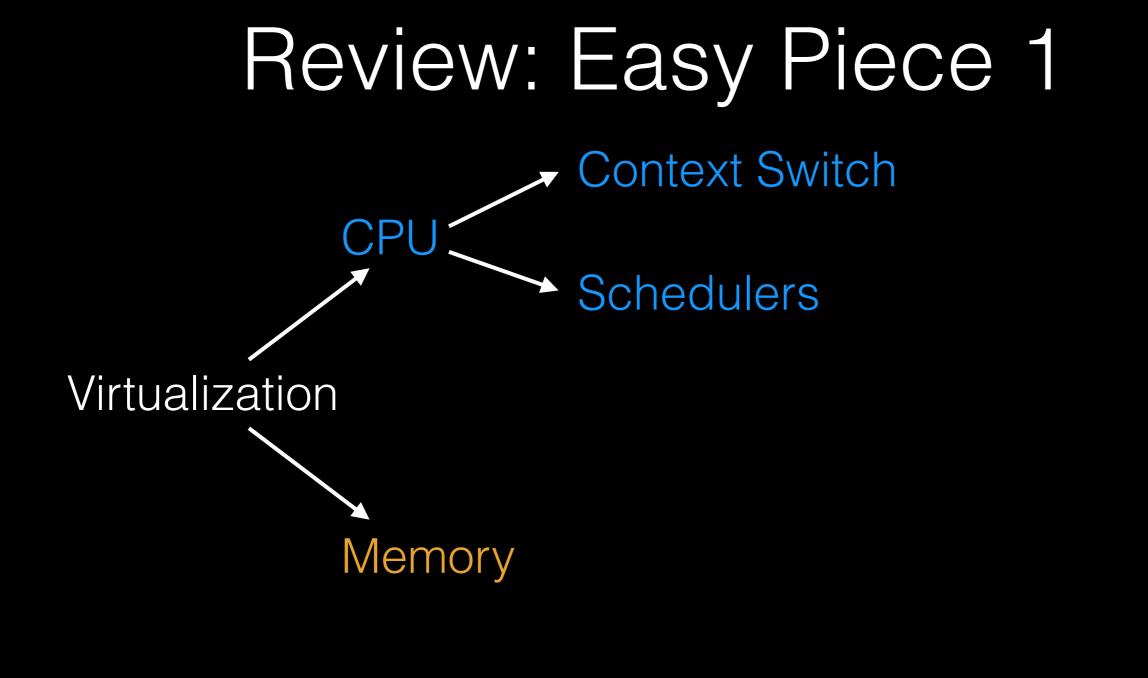

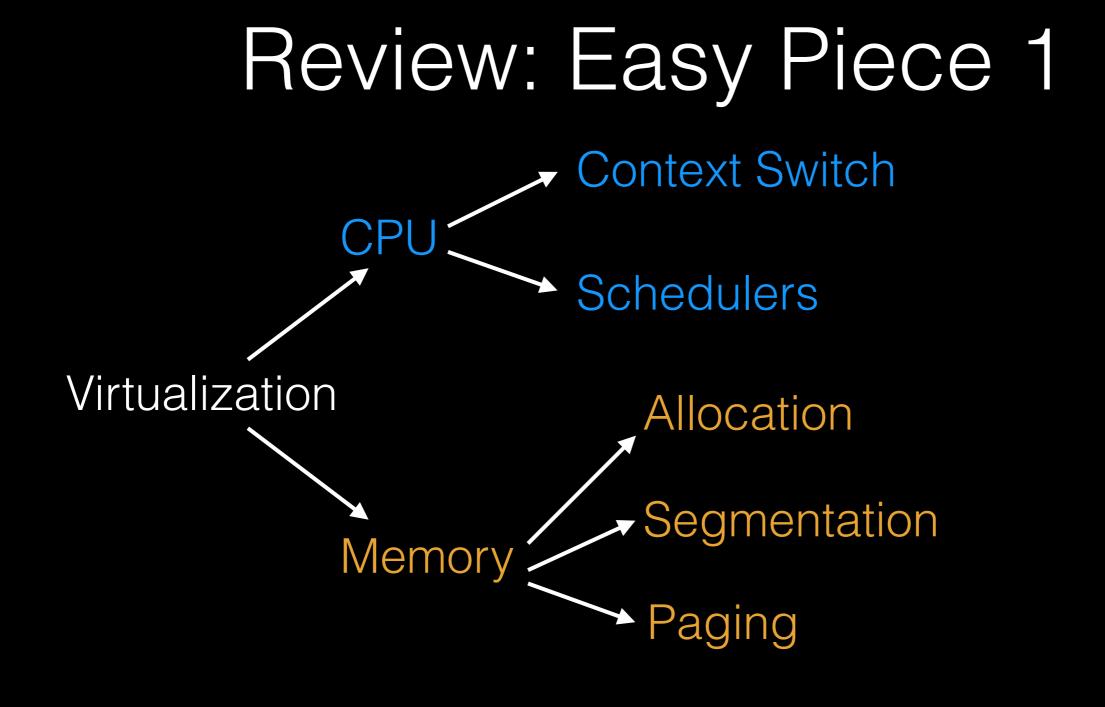

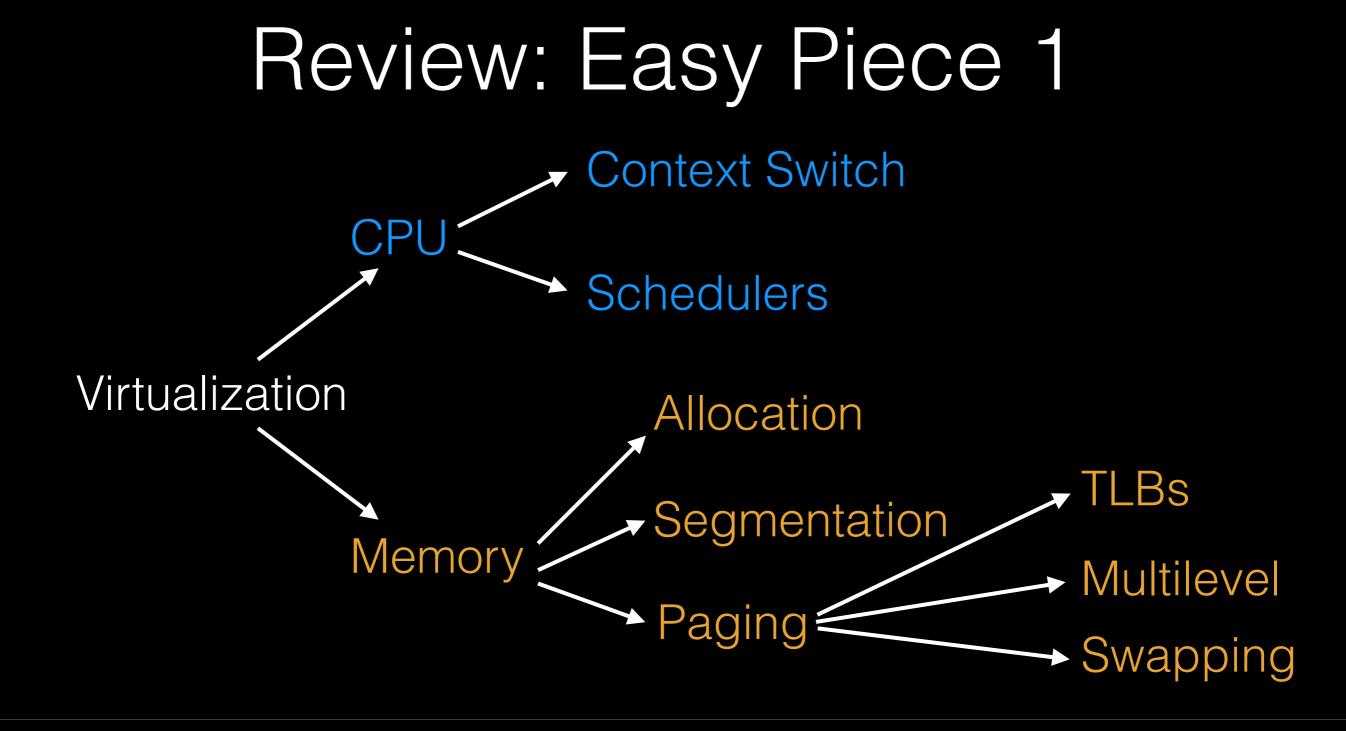

# Review: Easy Piece 1

# Review

- (1) name 3 places xv6 stores registers for context switches?

- (2) how can you game the multi-level feedback queue?

- (3) what field does malloc need for a free node that a kernel doesn't need to track a free page?

- (4) which segment needs different translation rules? Why?

- (5) how can a TLB avoid flushing for context switches

- (6) what's the advantage of multi-level PT over segmented PTs?

- (7) what H/W support is needed to do LRU swapping?

# Threads

#### What if there is only one process?

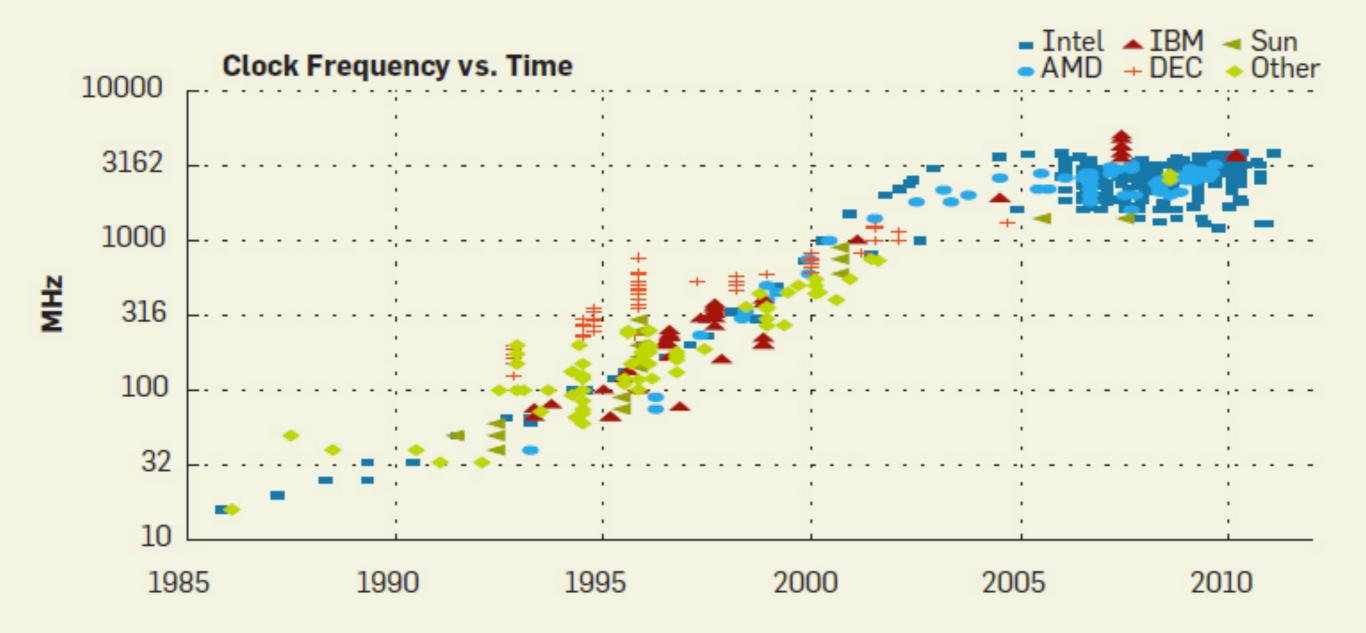

http://cacm.acm.org/magazines/2012/4/147359-cpu-db-recording-microprocessor-history/fulltext

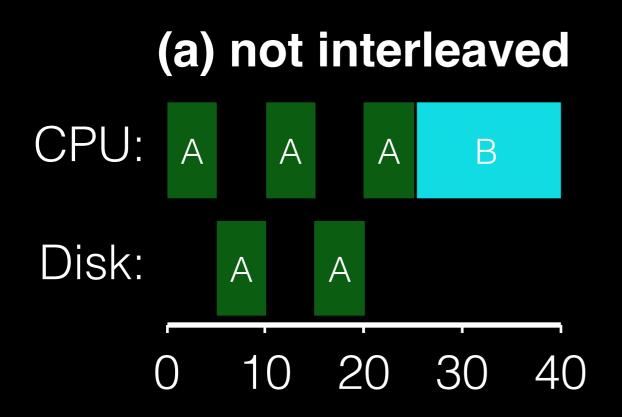

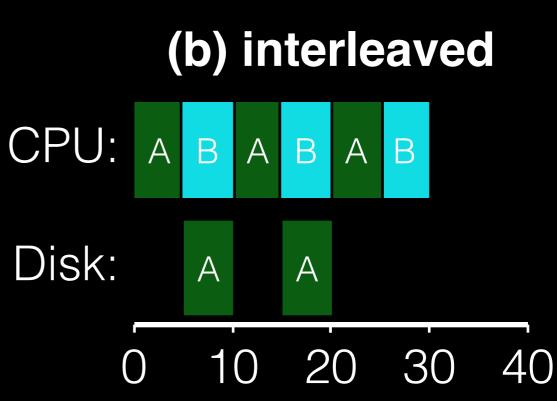

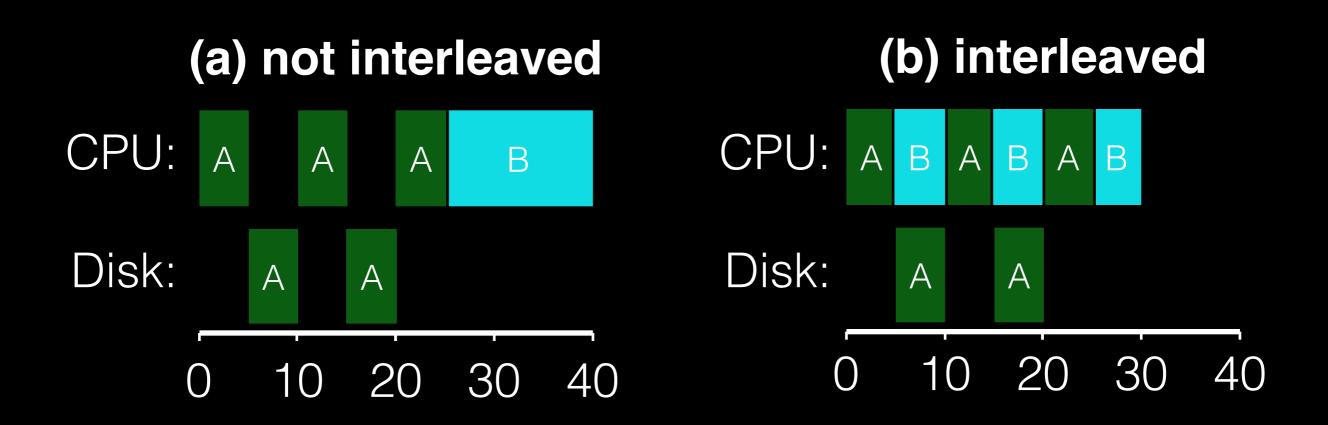

# CPU Trends

#### The future:

- same speed

- more cores

Faster programs => concurrent execution

# Goal

#### Write applications that fully utilize many CPUs...

# Strategy 1

Build applications from many communicating processes

- like Chrome (process per tab)

- communicate via pipe() or similar

Pros/cons?

# Strategy 1

Build applications from many communicating processes

- like Chrome (process per tab)

- communicate via pipe() or similar

Pros/cons?

- don't need new abstractions

- cumbersome programming

- copying overheads

- expensive context switching (why expensive?)

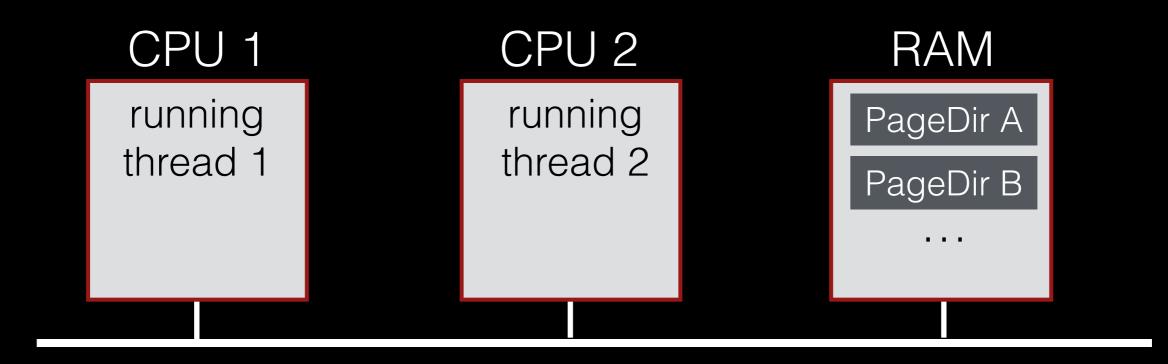

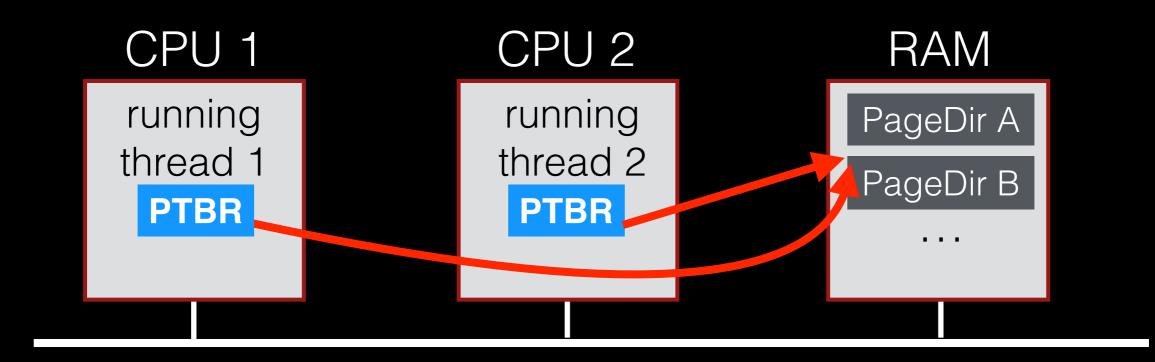

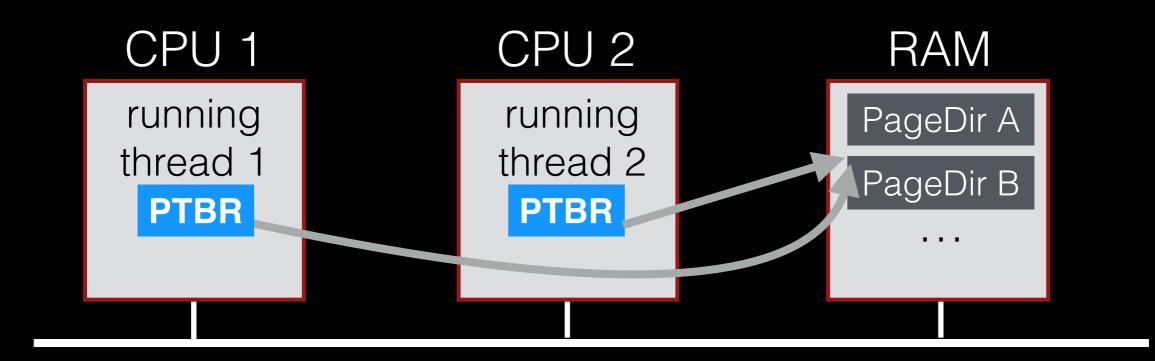

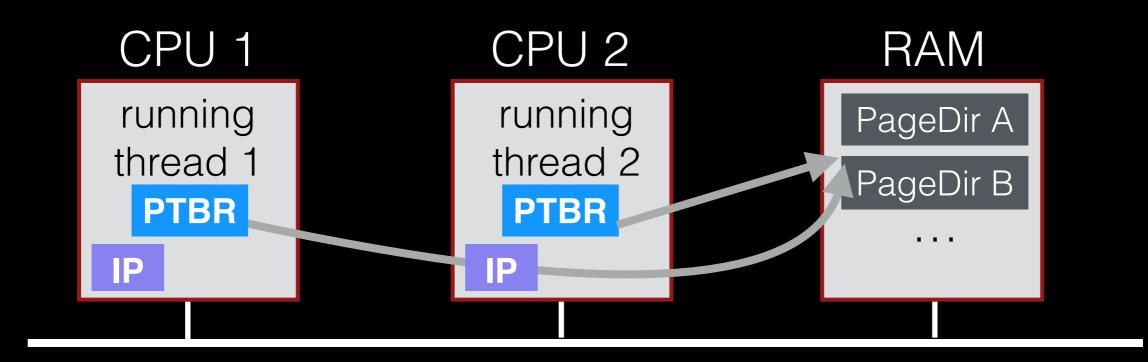

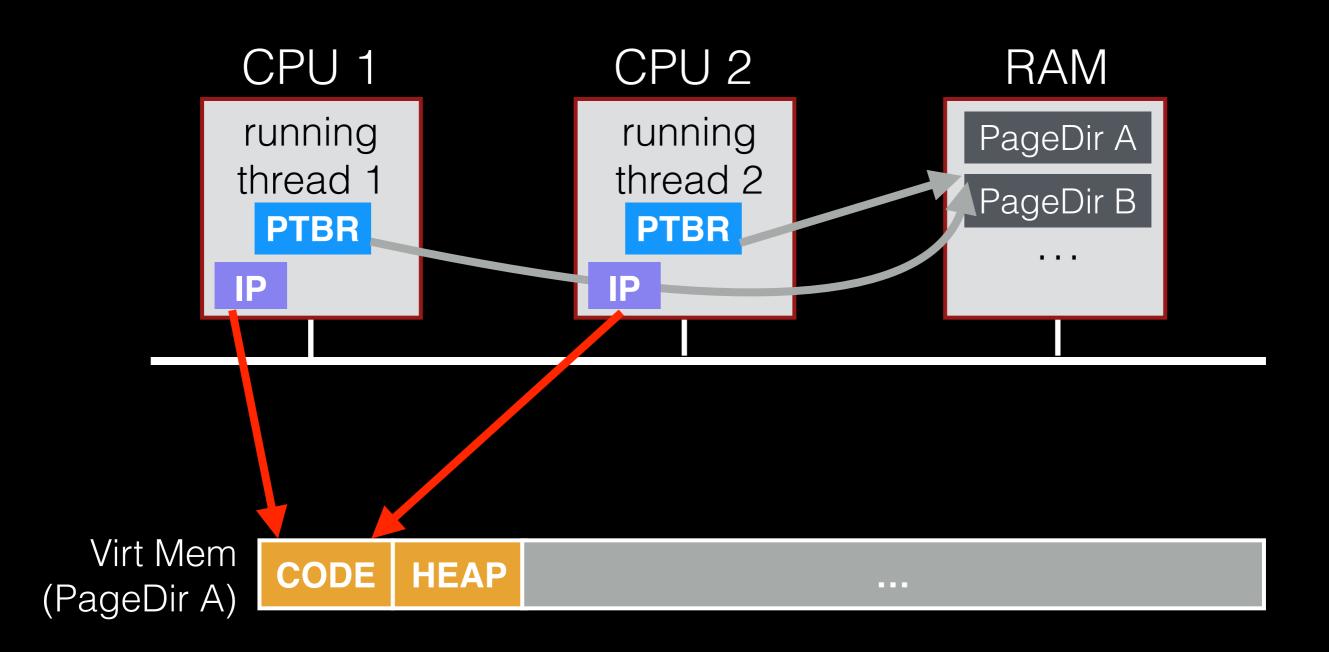

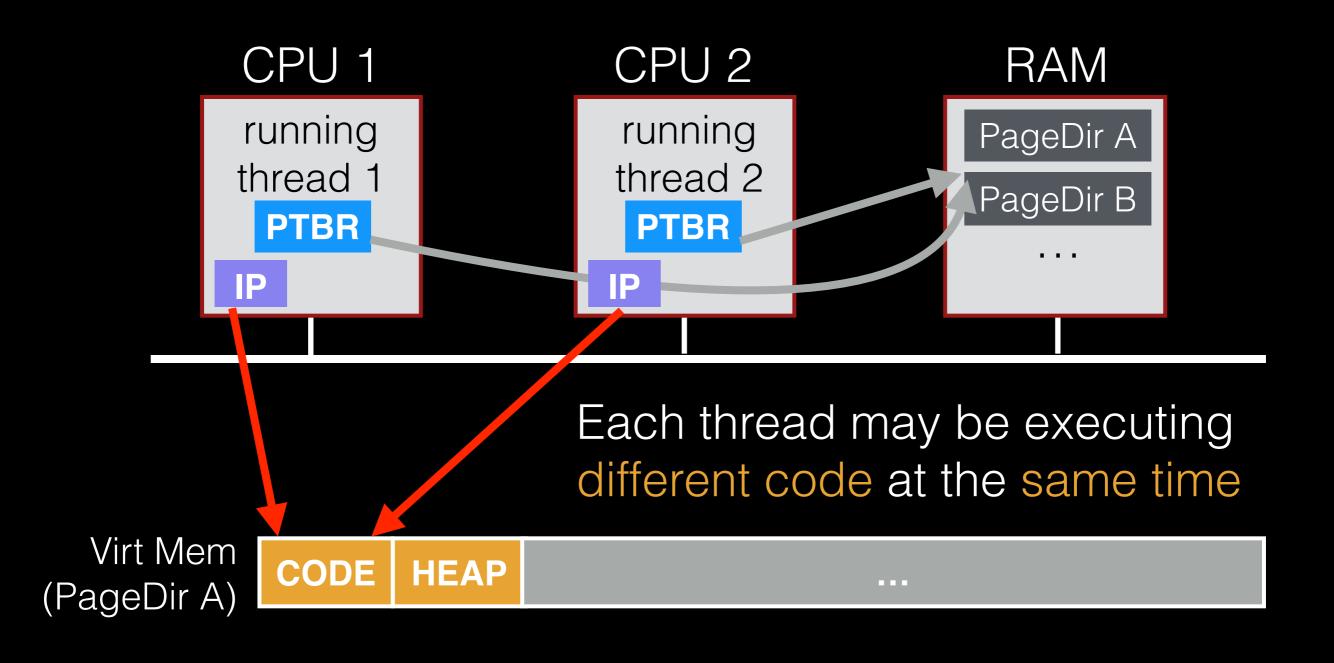

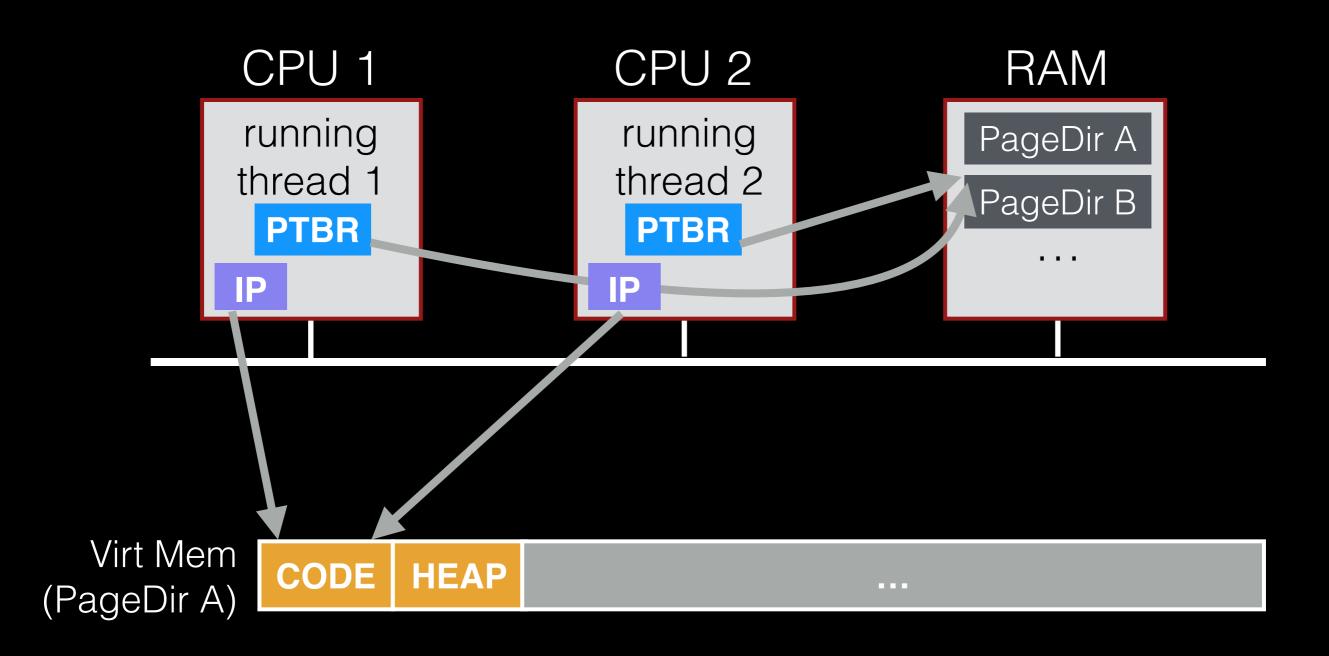

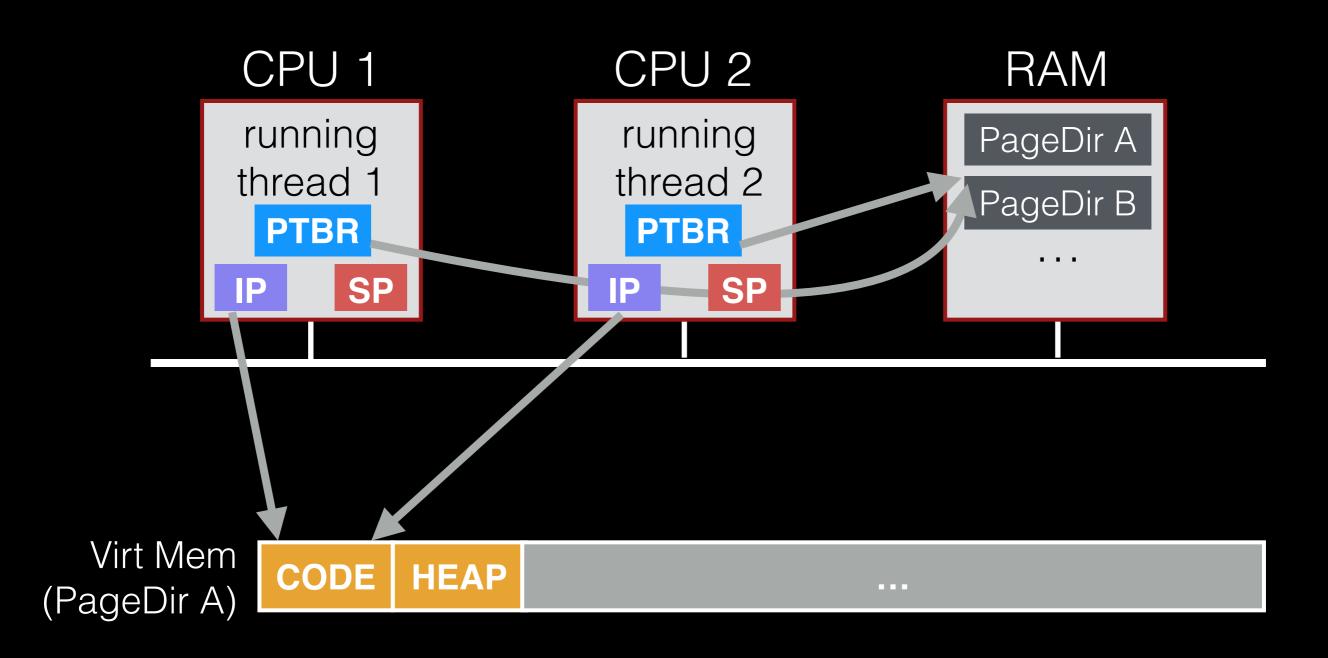

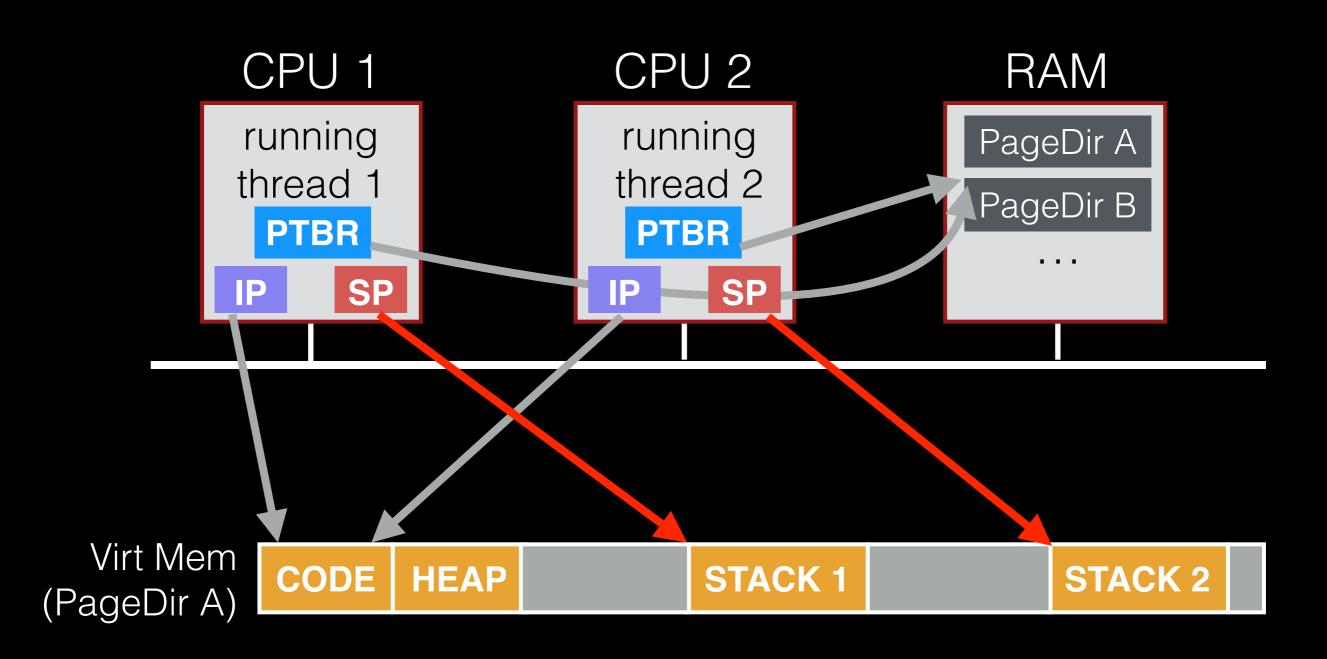

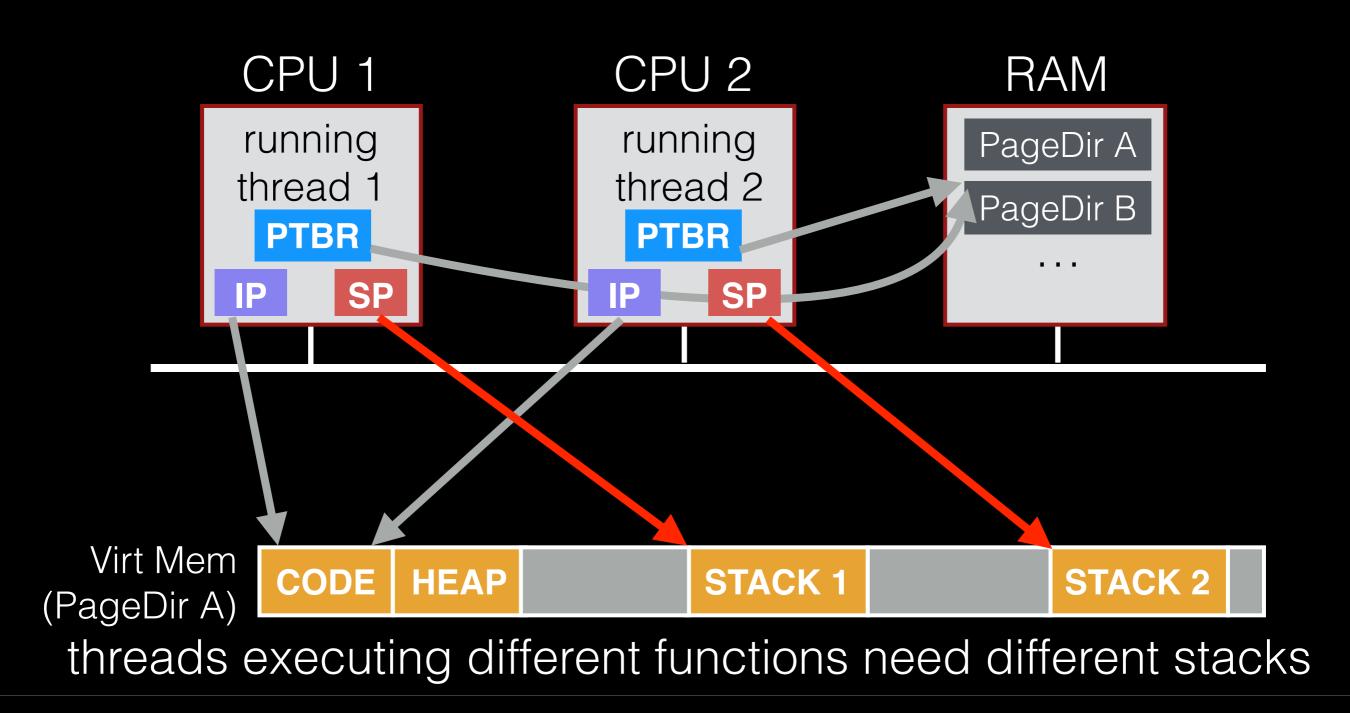

# Strategy 2

New abstraction: the **thread**.

Threads are just like processes, but they share the address space (e.g., using same PT).

# Demo: basic threads

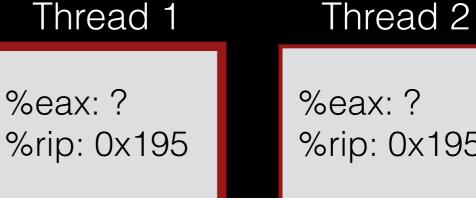

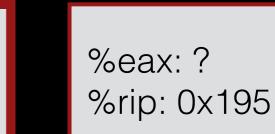

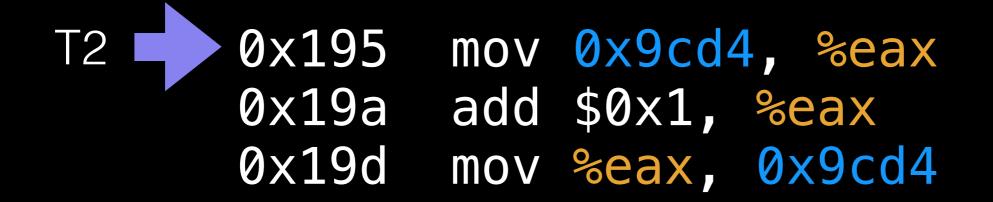

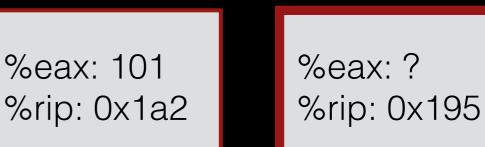

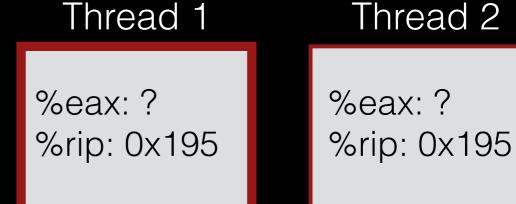

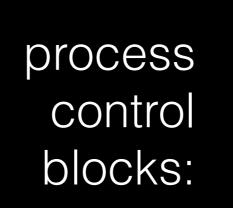

- State: 0x9cd4: 100 %eax: ? %rip = 0x195

- process control blocks:

%eax: ? %rip: 0x195

Τ1 Øx195 mov Øx9cd4, %eax 0x19a add \$0x1, %eax 0x19d mov %eax, 0x9cd4

State:

0x9cd4: 100

%eax: 100

%rip = 0x19a

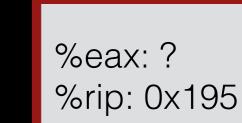

process control blocks:

%eax: ? %rip: 0x195 Thread 2

%rip: 0x195

%eax: ?

Thread 1

0x195

mov

0x9cd4, %eax

0x19a

add

\$0x1, %eax

0x19d

mov

%eax, 0x9cd4

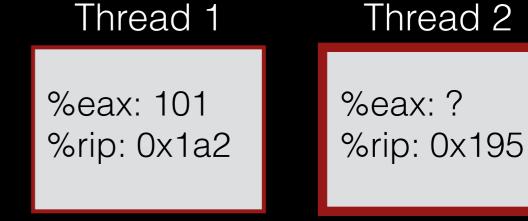

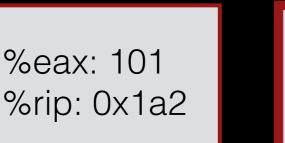

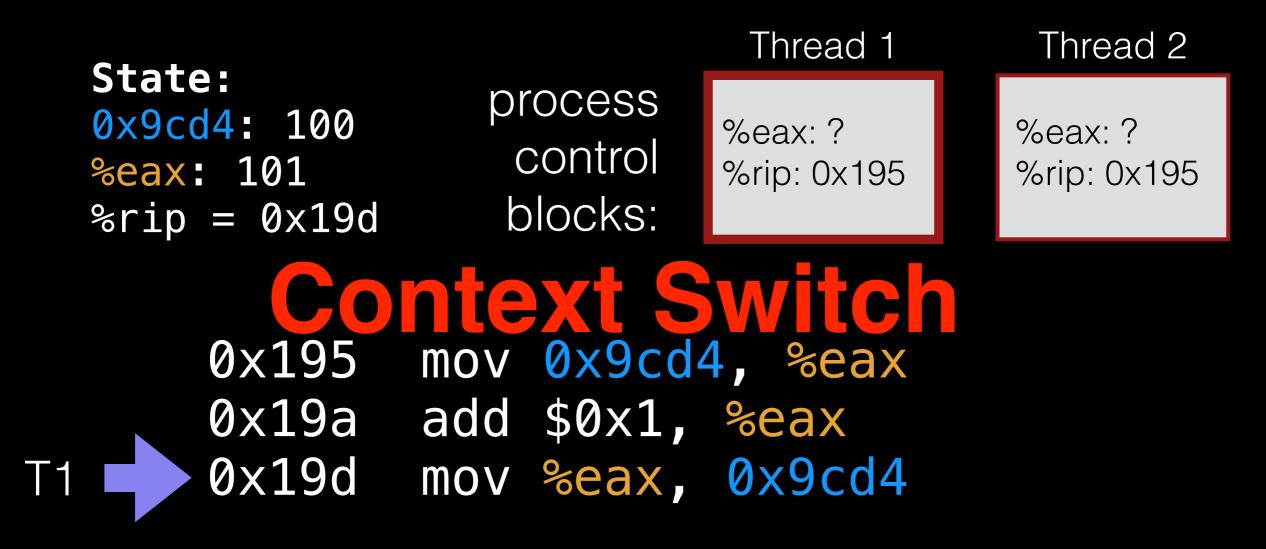

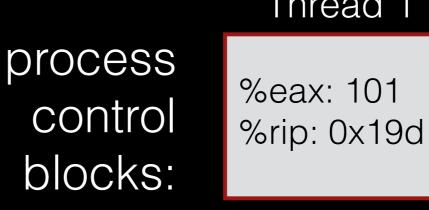

State:

0x9cd4: 100

%eax: 101

%rip = 0x19d

process control blocks:

0x195 mov 0x9cd4, %eax 0x19a add \$0x1, %eax T1 0x19d mov %eax, 0x9cd4

Thread 1

%rip: 0x195

%eax: ?

State:

0x9cd4: 101

%eax: 101

%rip = 0x1a2

T1

process control blocks:

Thread 2

0x195 mov 0x9cd4, %eax 0x19a add \$0x1, %eax 0x19d mov %eax, 0x9cd4

| Stata                                                          |                               | Thread 1                 | Thread 2               |

|----------------------------------------------------------------|-------------------------------|--------------------------|------------------------|

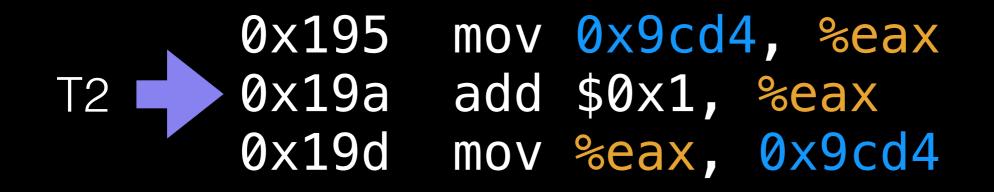

| <pre>State:     0x9cd4: 101     %eax: ?     %rip = 0x195</pre> | process<br>control<br>blocks: | %eax: 101<br>%rip: 0x1a2 | %eax: ?<br>%rip: 0x195 |

| State:       | nrococc |

|--------------|---------|

| 0×9cd4: 101  | process |

| %eax: 101    | control |

| %rip = 0x19a | blocks: |

| State:       |

|--------------|

| 0x9cd4: 101  |

| %eax: 102    |

| %rip = 0x19d |

Thread 2

Thread 1

| Øx195    | MOV | 0x9cd4 | 1, %eax |

|----------|-----|--------|---------|

| 0x19a    | add | \$0x1, | %eax    |

| T2 0x19d | MOV | %eax,  | 0x9cd4  |

- State:

0x9cd4: 102

%eax: 102

%rip = 0x1a2

- process control blocks:

Thread 1

%eax: ? %rip: 0x195

Thread 2

0x195 mov 0x9cd4, %eax 0x19a add \$0x1, %eax 0x19d mov %eax, 0x9cd4

| GOOD                                                             | ļ                             | Thread 1                 | Thread 2               |

|------------------------------------------------------------------|-------------------------------|--------------------------|------------------------|

| <pre>State:<br/>0x9cd4: 102<br/>%eax: 102<br/>%rip = 0x1a2</pre> | process<br>control<br>blocks: | %eax: 101<br>%rip: 0x1a2 | %eax: ?<br>%rip: 0x195 |

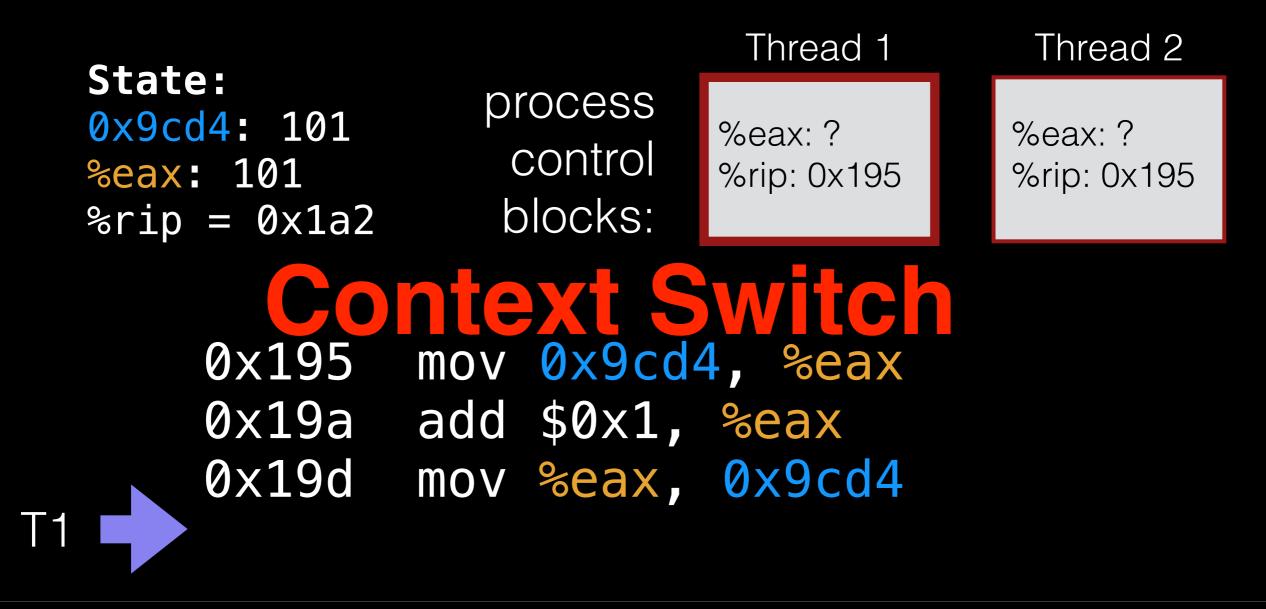

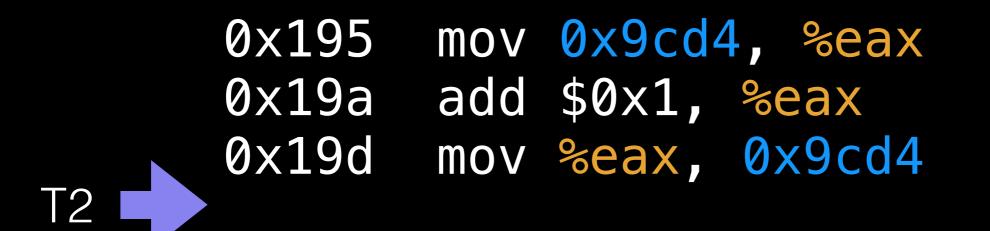

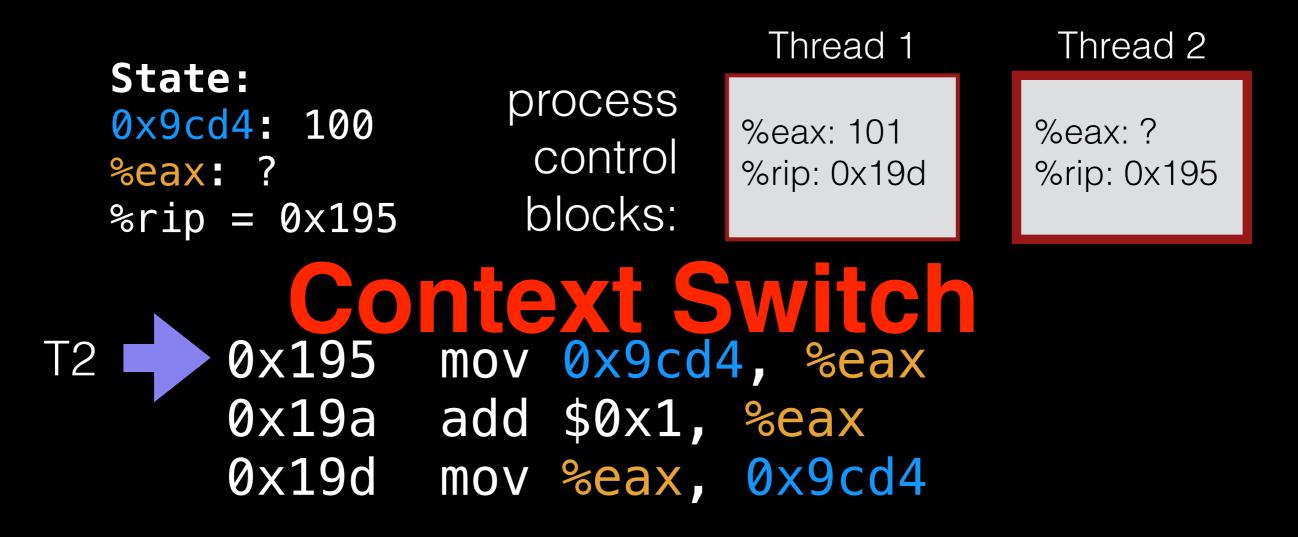

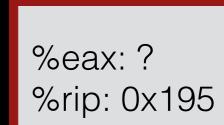

## Another schedule

- State: 0x9cd4: 100 %eax: ? %rip = 0x195

- process control blocks:

%eax: ? %rip: 0x195

Τ1 Øx195 mov Øx9cd4, %eax 0x19a add \$0x1, %eax 0x19d mov %eax, 0x9cd4

State:

0x9cd4: 100

%eax: 100

%rip = 0x19a

process control blocks:

%eax: ? %rip: 0x195 Thread 2

%rip: 0x195

%eax: ?

Thread 1

0x195

mov

0x9cd4, %eax

0x19a

add

\$0x1, %eax

0x19d

mov

%eax, 0x9cd4

State:

0x9cd4: 100

%eax: 101

%rip = 0x19d

process control blocks:

0x195 mov 0x9cd4, %eax 0x19a add \$0x1, %eax T1 0x19d mov %eax, 0x9cd4

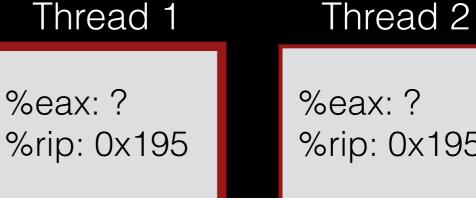

| State:<br>0x9cd4: 100 | process |  |

|-----------------------|---------|--|

| %eax: ?               | control |  |

| %rip = 0x195          | blocks: |  |

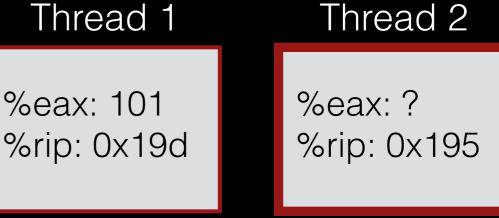

Thread 1

%eax: 101

%rip: 0x19d

| State:   |      |

|----------|------|

| 0x9cd4:  | 100  |

| %eax: 10 | 0    |

| %rip = 0 | x19a |

Thread 2

Thread 1

| State:   |       |

|----------|-------|

| 0x9cd4:  | 100   |

| %eax: 1  | 01    |

| %rip = 0 | 0x19d |

Thread 2

0x9cd4, %eax 0x195 MOV add \$0x1, %eax 0x19a 0x19d mov %eax, 0x9cd4 T2

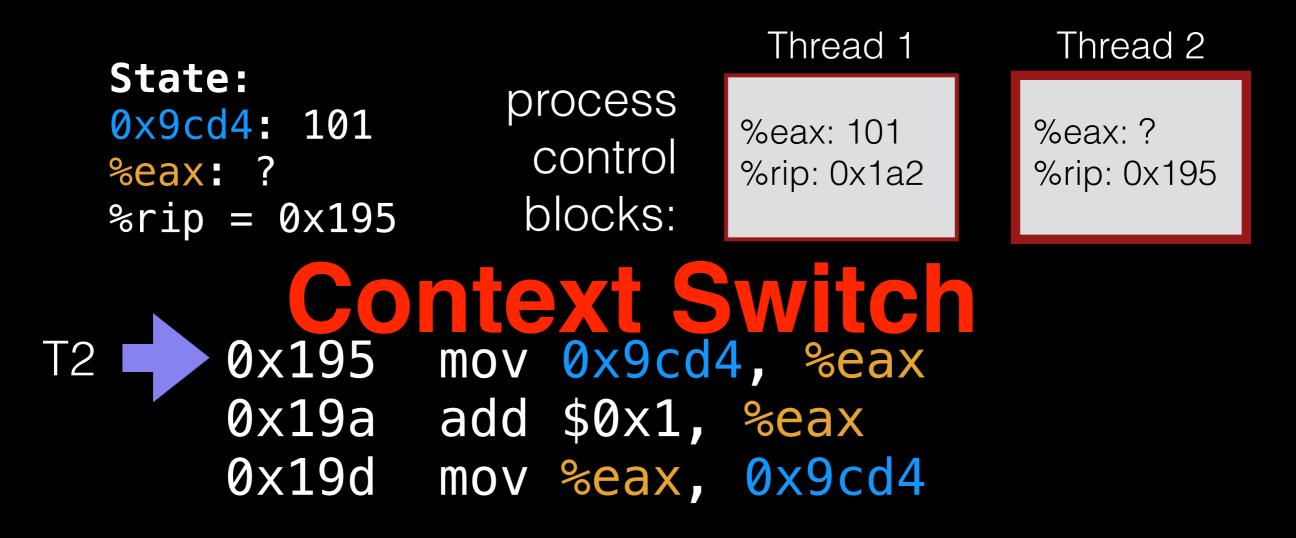

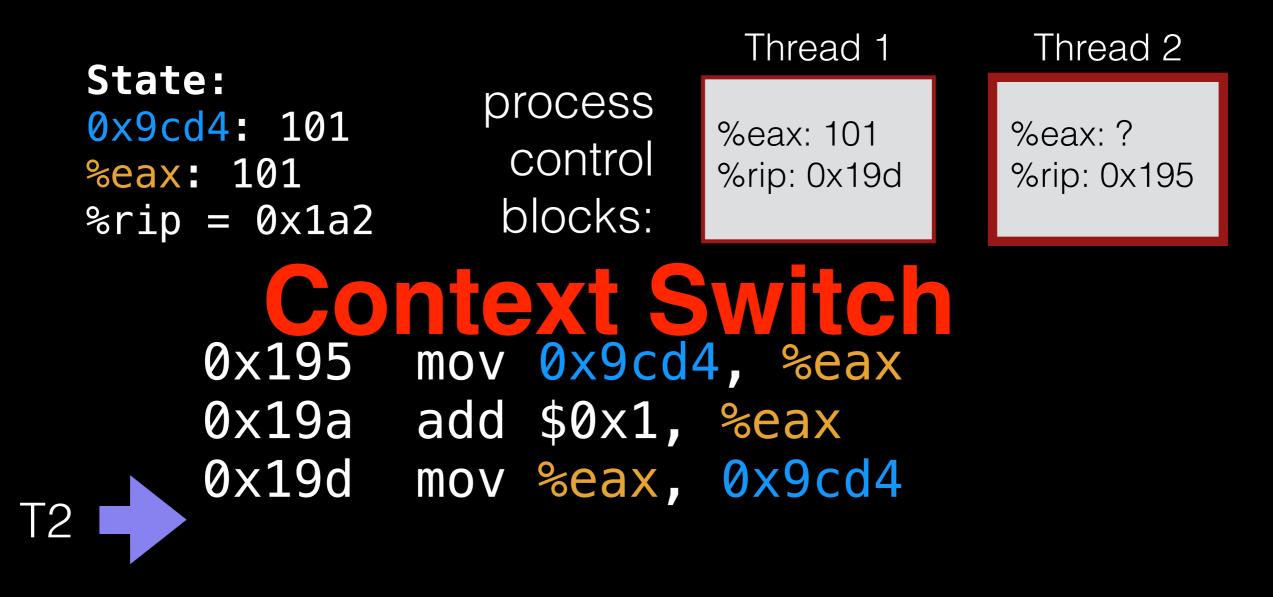

- State:<br/>0x9cd4: 101process<br/>control%eax: 101control<br/>blocks:

- Thread 1Thread 2%eax: 101<br/>%rip: 0x19d%eax: ?<br/>%rip: 0x195

0x195 mov 0x9cd4, %eax 0x19a add \$0x1, %eax 0x19d mov %eax, 0x9cd4

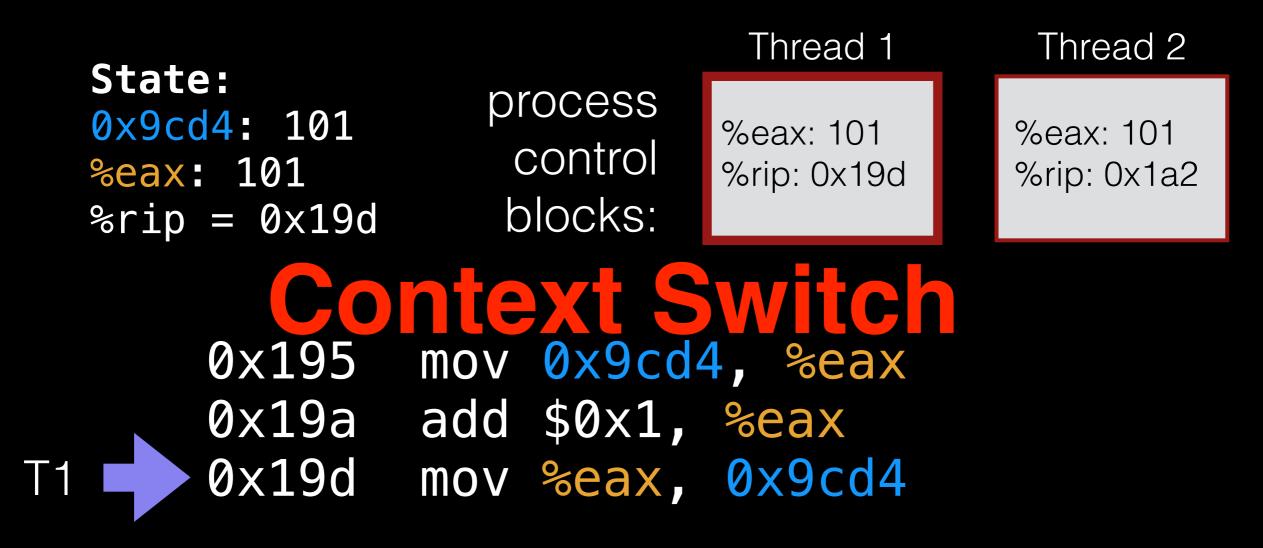

| State:   |      |

|----------|------|

| 0x9cd4:  | 101  |

| %eax: 10 | 1    |

| %rip = 0 | x19d |

process control blocks:

Thread 1

%eax: 101

%rip: 0x19d

State:

0x9cd4: 101

%eax: 101

%rip = 0x1a2

T1

process control blocks:

%eax: 101 %rip: 0x1a2

Thread 2

0x195 mov 0x9cd4, %eax 0x19a add \$0x1, %eax 0x19d mov %eax, 0x9cd4

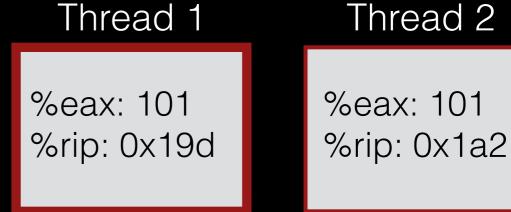

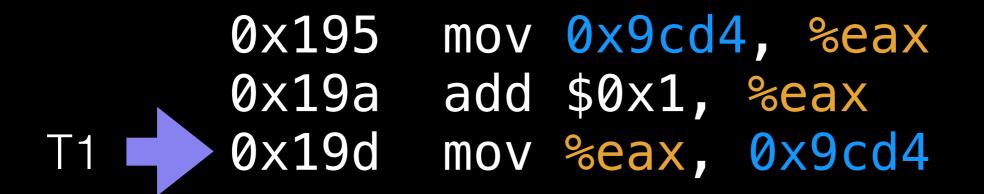

| WRON                                                             | IG!                           | Thread 1                 | Thread 2                 |

|------------------------------------------------------------------|-------------------------------|--------------------------|--------------------------|

| <pre>State:     0x9cd4: 101     %eax: 101     %rip = 0x1a2</pre> | process<br>control<br>blocks: | %eax: 101<br>%rip: 0x19d | %eax: 101<br>%rip: 0x1a2 |

0x195 mov 0x9cd4, %eax 0x19a add \$0x1, %eax 0x19d mov %eax, 0x9cd4

#### **Thread 1**

mov 0x123, %eax add %0x1, %eax mov %eax, 0x123

#### **Thread 2**

mov 0x123, %eax add %0x1, %eax mov %eax, 0x123

Thread 1Thread 2mov 0x123, %eaxadd %0x1, %eax

mov 0x123, %eax

mov %eax, 0x123

add %0x1, %eax mov %eax, 0x123

Thread 1

Thread 2 mov 0x123, %eax

mov 0x123, %eax

add %0x1, %eax

add %0x1, %eax

mov %eax, 0x123

**Thread 1**

#### **Thread 2**

mov 0x123, %eax add %0x1, %eax mov %eax, 0x123

mov 0x123, %eax add %0x1, %eax mov %eax, 0x123

**Thread 1**

**Thread 2**

mov 0x123, %eax add %0x1, %eax

mov 0x123, %eax add %0x1, %eax mov %eax, 0x123

mov %eax, 0x123

# Debugging

Concurrency leads to non-deterministic bugs, called race conditions.

Whether bug manifests depends on CPU schedule!

Passing tests means little.

How to program: imagine scheduler is malicious.

### What do we want?

Want all or none of these instructions to execute. That is, we want them to be atomic.

> mov 0x123, %eax add %0x1, %eax mov %eax, 0x123

## What do we want?

Want all or none of these instructions to execute. That is, we want them to be atomic.

> mov 0x123, %eax add %0x1, %eax mov %eax, 0x123 — critical section

## What do we want?

Want all or none of these instructions to execute. That is, we want them to be atomic.

> mov 0x123, %eax add %0x1, %eax mov %eax, 0x123 - critical section

We want mutual exclusion for critical sections. That is, if I run, you can't (and vice versa).

# More Demos

#### Announcements

Be sure you've read up to Chapter 24 in OSTEP!

p2a due this Friday.

Office hours today. In office. 1pm.