# **Deadline-Aware Offloading for High-Throughput Accelerators**

Tsung Tai Yeh<sup>\*,^</sup>

Matthew D. Sinclair<sup>+,||</sup> Bradford M. Beckmann<sup>||</sup> Timothy G. Rogers<sup>\*</sup>

|| AMD Research \* Purdue University ^ National Chiao Tung University + University of Wisconsin ttyeh@cs.nctu.edu.tw sinclair@cs.wisc.edu Brad.Beckmann@amd.com timrogers@purdue.edu

# Abstract

Contemporary GPUs are widely used for throughput-oriented data-parallel workloads and increasingly are being considered for latency-sensitive applications in datacenters. Examples include recurrent neural network (RNN) inference, network packet processing, and intelligent personal assistants. These data parallel applications have both high throughput demands and real-time deadlines (40µs-7ms). Moreover, the kernels in these applications have relatively few threads that do not fully utilize the device unless a large batch size is used. However, batching forces jobs to wait, which increases their latency, especially when realistic job arrival times are considered.

Previously, programmers have managed the tradeoffs associated with concurrent, latency-sensitive jobs by using a combination of GPU streams and advanced scheduling algorithms running on the CPU host. Although GPU streams allow the accelerator to execute multiple jobs concurrently, prior state-of-the-art solutions use the relatively distant CPU host to prioritize the latency-sensitive GPU tasks. Thus, these approaches are forced to operate at a coarse granularity and cannot quickly adapt to rapidly changing program behavior.

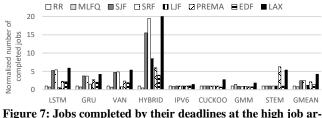

We observe that fine-grain, device-integrated kernel schedulers efficiently meet the deadlines of concurrent, latencysensitive GPU jobs. To overcome the limitations of softwareonly, CPU-side approaches, we extend the GPU queue scheduler to manage real-time deadlines. We propose a novel laxity-aware scheduler (LAX) that uses information collected within the GPU to dynamically vary job priority based on how much laxity jobs have before their deadline. Compared to contemporary GPUs, 3 state-of-the-art CPU-side schedulers and 6 other advanced GPU-side schedulers, LAX meets the deadlines of 1.7X - 5.0X more jobs and provides better energy-efficiency, throughput, and 99-percentile tail latency.

*Keywords* – *GPGPU*, *job scheduling*, *laxity*

#### 1 Introduction

GPUs are the programmable accelerator of choice for massively data-parallel applications that do not have strict latency requirements. However, there is a growing class of latencysensitive, data-parallel workloads that can benefit from the GPU's throughput. Examples include machine learning (ML) inference for RNNs [24]-[28][51], network packet processing [61]-[63], and natural language processing (NLP) in intelli-

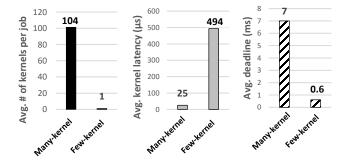

Figure 1: Characteristics of many-kernel latency-sensitive jobs versus few-kernel latency-sensitive jobs, listed in Table 4.

gent personal assistants (IPAs) [65][70]. These latency-sensitive applications have become a staple of contemporary datacenters, which increasing include GPUs and other highthroughput accelerators. Given the availability of GPUs in the datacenter, and the data-parallel nature of the applications, there is significant potential to offload work from overburdened CPUs to an accelerator. However, contemporary GPUs are deadline-blind and have no mechanism to predict which work can be offloaded and completed in time.

Many deadline-driven applications exhibit a middling amount of data-parallelism [43]. Enough to justify GPU acceleration, but not enough to fully utilize the GPU's resources [69][70]. As a result, executing one job on the GPU at a time causes severe underutilization. To alleviate this issue, programmers batch similar jobs together [28], greatly improving throughput and utilization at the expense of additional latency. This increase in latency is usually unacceptable for tasks with tight deadlines [3], especially when realistic job arrival rates are considered. GPU programs can avoid batching, while still executing multiple jobs at once with streams. Streams allow kernels from independent jobs to be scheduled concurrently on multiple command queues located between the CPU and GPU [45][49][52]. However, as we discuss further in Section 2, software cannot efficiently manage the relative priority of these queues at short time scales, which makes it difficult to efficiently re-prioritize jobs with different deadlines as contention in the GPU changes.

State-of-the-art GPU solutions for managing latency-sensitive tasks are restricted to varying priorities at a coarse granularity on the host CPU [53]-[55], and thus do not fully utilize the GPU's integrated queue scheduling logic. Consequently, the precision of information available to these CPU-side mechanisms is limited. Dynamic, microsecond-scale information about GPU-side contention, which some latency-sensitive applications require, is difficult to track from host-side software. As a result, these software-only techniques are less effective when scheduling many latency-sensitive jobs and primarily focus on mixing latency-insensitive and latencysensitive work. We discuss related work further in Section 7. In contrast, we target a common situation where datacenters execute homogenous, latency-sensitive jobs in parallel [80].

Figure 1 demonstrates how quickly scheduling decisions must be made when executing concurrent latency-sensitive jobs. To better understand their demands, we subdivide our latency-sensitive applications into two categories: *many-kernel* and *few-kernel*. The *many-kernel* applications we study, which come from ML inference, are composed of several relatively small, short kernels, and typically have deadlines on the order of milliseconds. The *few-kernel* applications, which come from network packet processing and IPAs, execute a single, much longer kernel, but have more aggressive deadlines (usually < 1 ms). To efficiently manage both *many-kernel* and *few-kernel* applications, per-kernel scheduling decisions must be made at the microsecond timescale.

We argue that dynamic, integrated stream scheduling is necessary to meet the low-latency scheduling demands of these workloads. An analogy can be made to the memory hierarchy in modern CPUs. At the lower-levels of the CPU memory hierarchy, the operating system is responsible for managing the replacement of relatively large pages in physical memory from the relatively high-latency disk. However, smaller cache blocks, which require nanosecond-scale response times, are managed by hardware. In throughput-oriented GPUs, scheduling relatively few, millisecond- or second-scale kernels in software is acceptable. However, managing many short-running kernels to meet sub-millisecond or millisecond-scale deadlines can be enhanced with improved scheduling within the GPU, which to our knowledge no prior work evaluating compute workloads has proposed.

Integrated GPU stream scheduling in contemporary compute-oriented GPUs operates in a deadline-blind manner. Typically, the GPU driver statically assigns priority levels to each command queue [76], although some APIs allow priorities to be set by the application [16] on stream allocation. In contrast, an effective deadline-aware scheduler must: (1) be aware of each job's deadline, (2) estimate each job's remaining execution time, and (3) frequently adjust job priority as time progresses and the contention level in the GPU changes. We propose an integrated *laxity-aware* stream scheduler (LAX) that achieves all three of these requirements.

LAX leverages the idea that stream-based GPU applications enqueue all their kernels in quick succession. In *manykernel* jobs, although each kernel launch is dependent on the data output by the previous kernel, all kernels associated with a particular job are known before the GPU begins execution. Thus, LAX uses the GPU's queue scheduler [or command processor (CP)], to perform a novel *stream inspection* technique that estimates the amount of work in each job. LAX's scheduling algorithm then combines this information, the job's deadline, and fine-grain information about current perkernel work completion rates to accurately estimate how much *laxity* the job has. A job's laxity is an estimate of how much earlier than its deadline it will finish given current conditions [46]. Based on each job's estimated laxity, LAX reprioritizes jobs to complete as many as possible by their respective deadlines. With the rich, fine-grained information available to GPU stream schedulers, LAX also prevents job oversubscription with a Little's Law-based queuing delay estimate [30][50] to reject work predicted to miss its deadline.

Contemporary GPUs perform device-side stream scheduling in a round-robin fashion, which ignores deadlines and the amount of remaining work. To our knowledge, no prior work has considered both job deadline and remaining work for real-time prioritization techniques on GPU compute applications. We compare LAX against 6 other advanced schedulers in the command processor (described in Table 3). LAX outperforms all other advanced schedulers by leveraging stream inspection and the work completion rate to judiciously reject jobs and prioritize critical work, demonstrating that deadlineaware scheduling is possible and practical in GPUs.

Prior work on real-time systems in the CPU space has used laxity to schedule jobs (discussed further in Section 7). However, the GPU's task-based (a.k.a, kernel-based) programming model presents a unique set of challenges and opportunities compared to applying laxity to OS-managed CPU threads. GPUs use a hierarchical execution model, where jobs contain one or more executed kernels that are themselves composed of workgroups. To leverage laxity scheduling within the GPU, we propose a novel job estimation mechanism based on workgroup completion times that naturally adjusts as both workgroups and kernels scale (discussed further in Section 4). Another unique challenge in applying laxity to GPUs is quickly and appropriately adapting to the extreme contention in massively parallel workloads. Our workgroupcentric estimation mechanism adapts to contention by monitoring the fine-grained workgroup completion rate.

Prior work on GPU kernel preemption or re-execution [56]-[59][79] are alternative mechanisms that can be used in combination with better stream scheduling. However, for latencysensitive workloads, the overheads associated with preempting GPU kernel contexts, whose aggregate registers and scratchpad size can be 100s of KBs (Table 1), may be prohibitive. Additionally, the benefits of preemption are muted for short running kernels that finish long before the cost of preemption and rescheduling can be amortized. Specifically,, Table 1 indicates that the vast majority of kernels in our evaluated latency-sensitive workloads complete within 10  $\mu$ s. Recently proposed preemption-based techniques, such as PREMA, are effective at intelligently preempting and scheduling relatively coarse-grained tasks [79]. However, LAX is able to outperform PREMA by 2.0X geomean on fine-grain

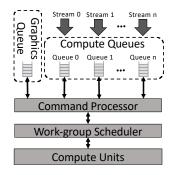

Figure 2: GPU Queue Scheduler Architecture.

tasks, by making intelligent fine-grained scheduling decisions without preemption (Section 6). We compare against additional preemption-based techniques in Section 7.

Overall, this paper makes the following contributions:

- 1. We observe that emerging, latency-sensitive applications use a *many-kernel* execution pattern and *fewkernel* jobs have very tight deadlines, both of which require microsecond-level scheduling decisions.

- We propose a novel stream inspection mechanism, which is used in combination with a dynamic, perkernel work completion rate to generate accurate estimates of work and time remaining in each job, given current contention conditions.

- 3. We propose a laxity-aware algorithm (LAX) and compare it to a continuum of solutions that range from doing all scheduling in host-side software to entirely within the GPU's CP. Given a per-job deadline provided by the programmer, LAX dynamically varies job priorities to improve throughput while attempting to meet real-time latency requirements.

- 4. LAX's combination of access to fine-grained information, more accurate queuing delay model, tight CP integration, and ability to rapidly adapt to contention completes more jobs by their deadlines and significantly improves GPU job throughput over a variety of contemporary and advanced schedulers by 1.7X-5.0X. LAX also provides a better combination of energy and performance, as well as throughput and 99-percentile latency, making latency-sensitive RNN inference [12][13], networking [61]-[63][66], and IPA [65][70] applications more practical on GPUs.

# 2 GPU Stream Scheduler Background

Unlike CPUs, GPUs contain multiple levels of hardware scheduling to manage the large number of in-flight threads. Contemporary GPUs contain multiple queues to manage independent work submitted asynchronously with streams [45][49][52]. This independent work can be executed concurrently when GPU resources are available. We next describe current stream scheduling architecture and operation.

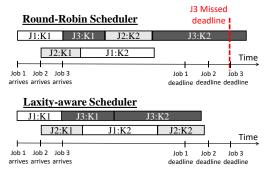

Figure 3: Comparison of Round Robin and Laxity-aware Schedulers for a GPU that can simultaneously execute 2 jobs.

# 2.1 GPU Command Processor

The CP is an integrated microprocessor within a GPU, which parses the kernel contexts and schedules streams. In Figure 2, each stream is mapped to a queue and each queue holds multiple kernels from a single stream. Inter-kernel dependencies between kernels in the same stream are maintained, but GPUs can asynchronously execute kernels from different streams simultaneously. Each queue entry describes a separate kernel and includes details such as thread dimensions, register usage, and local data store (LDS) size. The work-group (WG) scheduler reads these fields to dispatch work groups to compute units (CUs). Generally, GPU WG schedulers issue all WGs from one kernel before switching to WGs from another kernel. Despite this restriction, WGs from kernels in different queues often interleave execution.

Normally, the CP in modern GPUs schedules kernels within these queues in a round robin (RR) manner [48]. This deadline-blind scheduling policy improves throughput, but makes it harder to complete jobs by their real-time deadlines. The top half of Figure 3 illustrates the problem with RR. In this example, the GPU is running three jobs with varying arrival times such that the deadline of each job varies. Each job contains two kernels with different execution times. For simplicity, we assume that at most two kernels can be concurrently executed. RR will schedule kernel 1 from job 1 (J1:K1) and kernel 1 from job 2 (J2:K1) first because they arrive before job 3. When job 3 arrives, its first kernel is scheduled after J1:K1, and then J3 is not scheduled again until both J1:K2 and J2:K2 have executed. Since J3 is the longest job, if it had been prioritized over J1 and J2, all the jobs could have made their deadlines. However, since RR is unaware of this, J3 misses its deadline.

# 2.2 Priority-based GPU Programming

At the application level, programmers can specify a limited number of priorities (e.g., high and low) typically immediately after allocating the stream [16]. Contemporary drivers and CPs are not designed to dynamically vary the priority of streams, which limits their ability to adapt to tight deadlines. First, the priority level submitted by programmers simply indicates the kernel's relative importance and does not indicate *when* the kernel must be completed. Second, priorities assigned to individual streams do not provide the GPU a global view of when to complete a chain of dependent kernels. Programmers conservatively set a job's priority to ensure that its deadline is met. Finally, jobs can have different amounts of work despite potentially having the same static priority level.

We propose to dynamically adjust the priorities of each job (and its associated queue) based on the job's estimated execution time. By adjusting the priorities, kernel launches are re-ordered to increase the number of jobs completed by their deadlines. The bottom half of Figure 3 demonstrates that with reasonably accurate execution time estimates, a deadlineaware scheduler can optimize the scheduling of deadline-sensitive jobs (similar to prior work for CPUs [74][75]). The bottom example begins like the top example, with the GPU scheduling J1 and J2 first, because they arrive earlier than J3. However, the LAX scheduler is aware of the deadlines and durations of all 3 jobs, so it prioritizes J3 since it will miss its deadline if not immediately scheduled (i.e., it has zero laxity). As a result, all jobs completed by the deadlines.

# 3 Latency-sensitive GPU Applications

This section characterizes important, latency-sensitive applications by their response time, level of parallelism and kernel composition. It then examines the tradeoff of increasing batch size versus the number of streams, and the impact of realistic arrival times on latency-sensitive GPU applications.

# 3.1 Applications

We study a wide group of latency-sensitive GPU applications that represent different use cases and access patterns to understand how they perform on contemporary GPUs.

### 3.1.1 Recurrent Neural Networks

RNNs are well suited for domains such as language translation [8][9] and speech recognition [10][11] where prior events persist and influence subsequent ones. RNNs contain loops that allow this information to persist across multiple iterations (or time steps). The number of times the loop is unrolled represents the RNN's sequence length, which varies across jobs and determines the length of the recurrent step. As a result, RNNs behave very differently than convolutional neural networks (CNNs) [4][5][7][44]. The hidden state is calculated by looking at the previous hidden state and the input at the current step. RNN models such as long-short-termmemory (LSTM) [32] and gated recurrent unit (GRU) [42] add memory cells to improve accuracy.

Each RNN time step contains multiple kernels with varying degrees of parallelism and execution time. As shown in Table 1, a single-batched LSTM job with a sequence length of 13 consists of 6 unique kernels and each kernel is called multiple times (we only show LSTM due to space constraints, Vanilla and GRU are similar). Unlike the training phase where latency is less critical [1][71]-[73], RNN inference jobs have real-time constraints [2][3][28][31][69]. It is challenging to

| Applications       | Kernel name         | # of calls | Exec time | Threads | Context size |

|--------------------|---------------------|------------|-----------|---------|--------------|

|                    | TensorKernel 1      | 3          | 3.96 µs   | 16384   | 397 KB       |

| -                  | TensorKernel 2      | 5          | 1.79 µs   | 128     | 3.1 KB       |

| LSTM [12][13]      | TensorKernel 3      | 2          | 4.45 µs   | 2048    | 106.8 KB     |

| L31W1[12][13]      | TensorKernel 4      | 40         | 4.74 μs   | 64      | 9.1 KB       |

|                    | ActivationKernel 5  | 39         | 8.87 µs   | 128     | 11.1 KB      |

|                    | rocBLASGEMMKernel 1 | 13         | 127.48 µs | 1024    | 562.4 KB     |

| IPV6 [66]          | IPV6Kernel          | 1          | 25 µs     | 8192    | 329 KB       |

| CUCKOO [66]        | cuckooKernel        | 1          | 300 µs    | 8192    | 566 KB       |

| GMM [65]           | GMMKernel           | 1          | 1.5 ms    | 2048    | 195.5 KB     |

| STEM [65]          | STEMKernel          | 1          | 150 µs    | 4096    | 317 KB       |

| 100                |                     | 180        | 147 293   | 210     | 213          |

| 120 —              |                     |            |           | _       | -            |

| . 100              |                     |            |           |         |              |

| 00 ee time<br>0 80 |                     |            |           |         |              |

| Se ti              |                     |            |           |         |              |

Table 1: Summary of kernels in latency-sensitive benchmarks.

LSTM GRU VAN IPV6 CUCKOO GMM STEM HYBRID LSTM GRU VAN IPV6 CUCKOO GMM STEM HYBRID LSTM GRU VAN IPV6 CUCKOO GMM STEM HYBRID

Figure 4: Comparing response times with varying job arrival rates, normalized to batch size 1.

fully utilize the GPU while minimizing the end-to-end latency of RNN inference applications.

#### 3.1.2 Network Packet Processing

Network packet processing increasingly utilizes GPUs to take advantage of their massive parallelism. For example, IPV6 performs a Longest Prefix Matching computation used in IPV6 network packet table lookups and has a stringent 40  $\mu$ s deadline [61][66]. Similarly, Cuckoo must complete cuckoo hash table lookups to map MAC address to output ports within 600  $\mu$ s [61][66]. Unlike RNNs, these networking applications are composed of a single kernel, and their input sizes are determined by the speed of the network. In Table 1, the input size of 8K represents the number of network packets that arrived per 100  $\mu$ s in 40 Gbps networks.

# 3.1.3 Intelligent Personal Assistants

IPAs also have significant real-time constraints. Although prior work explores a series of algorithms used in an automatic speech recognition (ASR) pipeline by IPAs, we focus on Gaussian mixture model (GMM) and Stemmer (STEM), two single kernel pieces that consume the most time in IPAs and thus present the biggest challenge [70]. GMM maps input feature vectors to multi-dimensional space and consumes 85% of ASR's computational time [65][70]. STEM reduces inflected words to a certain word stem and takes up to 85% of the remaining time in the ASR pipeline [65][70].

### 3.2 Small Data-Parallel Kernels

Table 1 characterizes each kernel in a single HIP [17][18] RNN LSTM inference job where its batch size is 1 and its hidden layer is 128. Both LSTM and GRU use 5 unique MI-Open [14] kernels and one rocBLAS [19] GEMM kernel that are called multiple times in an RNN forward pass. The MI-Open kernels perform tensor and activation operations. Each kernel has a varying number of threads. However, most kernels have few threads, and do not occupy the entire GPU.

The number of threads, registers, and LDS size of kernels determine the GPU utilization. In an AMD Radeon RX 580 GPU with 36 CUs based on the GCN architecture [22], each CU can concurrently execute 2560 threads, has 256 KB 32bit vector registers, and has 64 KB of LDS. However, LSTM's GEMM kernel only uses 1.11% of thread contexts, 1.26% of registers, and 2.78% of the LDS space. The other LSTM kernels similarly use relatively few resources. Hence, a single RNN job significantly under-utilizes the GPU, as prior work has also shown for other sequence lengths, hidden sizes, and batch size combinations [27][69]. Moreover, although IPV6, Cuckoo, GMM, and STEM are single kernel applications, they also complete very quickly and have narrow kernels with few threads that also under-utilize the GPU.

### 3.3 Impact of Job Arrival Rate

In a real system, the GPU receives job requests from different users or processes with varying arrival rates. Batching improves GPU utilization and throughput when requests arrive at the same time. However, it will delay individual jobs when requests arrive at varying rates. Streams alleviate this aspect of batching by allowing work to begin as soon as it arrives.

Figure 4 measures our application's response time on an AMD Radeon RX 580 GPU. We use streams to launch 32K jobs for the networking and IPA benchmarks and 512 jobs for the RNN benchmarks based on our GPU's maximum memory space. For the RNNs, we also show data for Hybrid RNNs (described in Section 5.2). In this experiment, all streams use the same static priority. We issue 10000 short execution time jobs per second for IPV6, CUCKOO, and STEM and 1000 jobs per second for RNNs and GMM with an exponential arrival rate. Each RNN job may have a different sequence length (see Section 5.2). We add padding and additional waiting time for the arrival of all jobs in a batch when the batch size is greater than 1 as needed.

In general, the high degree of parallelism within large batches increases resource contention and job execution time. For example, the response time of applications with a batch size of 128 can be 20-293X slower than the single-batched job due to the overhead of waiting for additional jobs to arrive. Thus, larger batch sizes may improve utilization for these applications, but this often comes at the cost of not meeting its deadline. In contrast, using multiple streams reduces normalized runtime and allows the GPU to process multiple jobs simultaneously. However, closer inspection of these results reveals that individual job execution times vary tremendously. For example, RNN jobs with long sequence lengths complete much slower than RNN jobs with shorter sequence lengths. The observation exposes an opportunity for a more advanced GPU scheduler to prioritize longer running jobs and allow more overall jobs to meet a given deadline.

Figure 5: LAX procedure and system overview.

*LaxityTime* = *Deadline* - (*TimeRemaining* + *DurationTime*)

**Equation 1: Laxity Time Calculation.**

# 4 LAX: Laxity-Aware GPU Job Scheduling

### 4.1 LAX System Overview

Figure 5 presents an overview of our LAX framework. In multi-job GPU applications, all kernels associated with a single job are enqueued on the same stream or underlying GPU compute queue. Before running a job, as discussed in Section 1, LAX performs stream inspection to look ahead, parsing all the kernels in a queue to determine their names and associated number of WGs. For example, for the RNNs the sequence length determines the number of kernels in the job. To store this information, LAX introduces a Job Table that stores information about the work remaining in each compute queue. After parsing the WG information for every kernel in a queue, this information is added to the corresponding WGList for the queue. Stream inspection can be performed entirely in the CP, by reading the contents of the command queues, or by having the CPU driver insert a custom packet at the head of the queue indicating the work behind it.

LAX computes the estimated time remaining in each job using the number of WGs from the *WGList* and a per-kernel work completion rate stored in a *Kernel Profiling Table*. Given the estimated time remaining and a programmer-specified deadline (passed when initializing a job on a stream), LAX computes the laxity of each job using Equation 1.<sup>1</sup> The *LaxityTime* tells us how close to its deadline a job is predicted to finish. Jobs with less *LaxityTime* have higher priority.

Similar to prior work, LAX uses a pull-based model for offloading work from a CPU server [53][54][80]. As jobs arrive at the server, LAX successfully offloads as many jobs as possible. However, unlike prior work, LAX uses its per-job completion time estimates to generate a queuing delay estimate for new jobs entering the system. Based on current contention, if LAX estimates that the new job will not meet its deadline, it will not attempt to offload the job to the GPU.

### 4.1.1 Implementing LAX

Although modern GPUs have CPs, their software is not easily modified, and GPU vendors have not publicly released an API to reprogram them. Moreover, LAX requires fast access

<sup>&</sup>lt;sup>1</sup> If additional work is later enqueued to the job's stream, LAX will update its prediction.

```

Algorithm 1: Steady State Queuing Delay Calculation.

1. totRemTime = 0

2. // new jobs are pushed to the end of the queue

3. For i = JobQ.begin() to JobQ.end()

holdJobTime = 0

4.

5.

durTime = curTick() - JobQ[i].startTime

For (j = 0; j < JobQ[i].WGList.size; j++)</pre>

6.

7.

kernelID = JobQ[i].WGList[j].kernelID

If (JobO[i].state != init)

8.

/* sum the total remaining time of jobs */

9.

totRemTime += JobQ[i].WGList[j].numWG

10.

/ kernelTable[kernelID].WGCompRate

Else /* initialize new job's estimate */

11.

holdJobTime += (JobQ[i].WGList[j].numWG

12.

kernelTable[kernelID].WGCompRate)

13.

End /*end if*/

End /*end for*/

14.

If (totRemTime + (holdJobTime + durTime) <</pre>

15.

JobQ[i].Deadline)

16.

/* New-invoked job's priority is the highest */

If (JobQ[i].state == init) JobQ[i].prior = 0

17.

18.

JobQ[i].state = readyState

totRemTime += holdJobTime

19.

20.

Else /* Cannot complete job in time, tell CPU */

rejectJob()

21.

22.

End /*end if*/

23. End /*end for*/

```

to custom performance counters since LAX frequently recalculates job priorities based on dynamic information (Sections 4.2 - 4.4). LAX also utilizes a customized per-kernel WG completion rate as part of its calculations (Section 4.2). Accordingly, we extend the CP as necessary. First, we extend the CP software to store the Job Table that tracks important information per kernel and make scheduling decisions based on information passed from the hardware. Next, we modify the GPU to add a new counter that tracks the WG completion rate and extend the existing counters to allow them to be frequently read by the CP, which stores and uses these counter values when making its scheduling decisions.

### 4.2 Job Remaining and Laxity Time Estimates

To estimate the laxity of currently executing jobs and the queuing delay for incoming jobs, LAX generates an estimate of the time remaining in each job with the help of an inmemory Job Table. As shown in Figure 5, each table entry has six fields: 1) QueueID (QID); 2) Priority (used by the CP to make scheduling decisions); 3) WGList (the list of the job's kernels and the number of WGs in each kernel); 4) Deadline (provided by the programmer); 5) StartTime; and 6) State (either init, ready, or running). In addition to the Job Table, LAX stores the per-kernel WG completion rates in a Kernel Profiling Table which is periodically updated (empirically set at 100  $\mu$ s) to reflect the GPU's contention conditions. Overall, LAX requires only 4240 bytes of memory to store this information for a 128-compute queue system.

To predict a job's remaining time, LAX scans the WGList to generate an estimate for how long each kernel in the job will take. For each entry in the list, LAX looks up the current WG completion rate for this particular kernel in the Kernel Profiling Table. By dividing the number of WGs in each kernel by the current WG completion rate for that kernel type, LAX generates a time estimate for the kernel. The kernels in our evaluated jobs have sequential dependencies and thus must be executed sequentially, thus LAX simply sums the estimated execution time of each kernel to generate the per-job estimate. As WGs complete, the WGCount entry in the Job Table is decremented to reflect the fact that the job has less work remaining. LAX combines the job's remaining time estimate with the user-specified Deadline and the job's Start-Time to generate the estimated LaxityTime. We describe the State and Priority fields in more detail in Sections 4.3 and 4.4.

# 4.3 Preventing Oversubscription with Queuing Delay Estimation

When designing a GPU to accept multiple jobs, each of which has a tight deadline, preventing oversubscription is critical. As discussed in Section 4.1, LAX only accepts jobs predicted to complete before their deadlines. To make this prediction, LAX must: (1) estimate how long a job J will take on the GPU under current conditions and (2) estimate how long J may be delayed behind other jobs already sent to the GPU, i.e. its queuing delay. Using each job's time remaining estimate from Section 4.2, LAX first computes how long Jshould take, given current completion rates. This allows LAX's estimates to adapt quickly and effectively to changing contention levels. If no estimate exists yet for a given kernel, LAX optimistically assumes it takes no time, to avoid rejecting work it could potentially complete.

Estimating J's queuing delay is more challenging because the deadlines and arrival rates of latency-sensitive jobs vary significantly. However, Little's Law works well independent of arrival rate [30][50]. Thus, LAX uses Little's Law to model the queuing delay of the jobs running on the GPU. Accordingly, Algorithm 1 uses Little's Law to sum up the predicted remaining time of all jobs currently execution in the system, including jobs that are *ready* but not *running*. Combining this estimate with the runtime estimate, if LAX predicts J will complete by its deadline, it accepts J and changes its state from *init* to *ready*, informing the CP that J's first kernel is ready to be executed on the GPU. Algorithm 1 shows the steady-state behavior; before enough WGs complete (line 12, Algorithm 1), we use the programmer-provided deadline.

### 4.4 Laxity-Aware Job Scheduling Algorithm

Next LAX needs to determine which job(s) should be run next. A job's laxity determines its priority in the laxity-aware job scheduler. The scheduler assigns each queue (job) a priority level and may adjust it over time. The job with the smallest current laxity is assigned the highest priority.

Algorithm 2 describes LAX's priority update mechanism, where priority zero is the highest priority level. Every  $100 \,\mu$ s, the priorities are updated, as we empirically found this improved performance. Since we want to prioritize jobs with the least laxity, any job that is predicted to complete by its deadline is assigned its laxity value as its priority (Line 12, Algorithm 2). LAX decreases a job's priority when it predicts the job will not reach the deadline (Line 18, Algorithm 2). When

```

Algorithm 2: Laxity-aware Scheduling.

1. For i = JobQ.begin() to JobQ.end()

2.

JobQ[i].RemTime = 0

For j = 0; j < JobQ[i].WGList.size; j++</pre>

З.

kernelID = JobQ[i].WGList[j].kernelID

4

JobQ[i].RemTime += JobQ[i].WGList[j].numWG

5.

6.

/ kernelTable[kernelID].WGCompRate

End /*end for*/

7.

JobQ[i].durTime = curTick() - JobQ[i].startTime

8.

ComplTime = JobO[i].RemTime + JobO[i].durTime

9.

If (JobQ[i].deadline > ComplTime)

10.

11.

/*laxityTime = deadline - ComplTime*/

JobQ[i].prior = JobQ[i].deadline - ComplTime

12.

13.

Else

JobQ[i].prior = ComplTime

14.

15

End /*end if*/

16.

/*deprioritize job if LAX cannot make deadline */

17.

If (JobQ[i].durTime > JobQ[i].deadline)

JobQueue[i].prior = INF

18.

End /*end if*/

19.

20. End /*end for*/

```

a job is predicted to miss a deadline, its *completionTime* (*remainingTime* + *durationTime*, where durationTime is the time since this job was enqueued) is greater than the deadline. To de-prioritize the job, LAX sets its priority to be equal to the *completionTime* (Line 14, Algorithm 2), because it is greater than the deadline, guaranteeing that the job has a lower priority than any other job that still has positive laxity.

After adjusting all job's priority, LAX issues all WGs from the highest priority job. If additional WG slots are available, it moves on to the next highest priority ready job, and so on until all WG slots are filled. After issuing the WGs from a kernel, LAX updates the associated job's status to *running*.

# 5 Methodology

We use the gem5 simulator [20][29], which offers native GPU ISA support [20]-[23] and a high fidelity, cycle-level GPU microarchitecture model [29] to evaluate the latencydriven applications (Table 2). The simulated system assumes the CPU and GPU share a single unified cache coherent address space and do not require explicit copies [77]. Since the original benchmark's codes assume discrete memory spaces between the CPU and GPU and use device copies, we modified the benchmarks to remove the device copies wherever possible. We analyze energy consumption with per-instruction energies [6][81]. Finally, we assume the CP can parse four streams in parallel every 2  $\mu$ s [29][48], including the latency of any memory accesses required by the scheduler.

### 5.1 Evaluated Compute Queue Scheduling Policies

We compare our laxity-based scheduler against ten other queue scheduling policies, which are detailed in Table 3 and implemented in gem5. These schedulers leverage various policies with static and dynamic information to schedule kernels and can be broken into three groups: state-of-the-art CPUside schedulers [28][53][54], GPU approaches that extend the CP, and variants of our laxity-based scheduler.

CPU-side scheduling mechanisms such as BAT [28], BAY [54], and PRO [53] (see Table 3 for details) improve throughput without requiring hardware changes. However, BAT,

Table 2: Key simulated system parameters.

| 14010 10 1109                | finalatea system parameterst                                |  |  |  |  |  |  |

|------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| GPU Clock                    | 1500 MHz                                                    |  |  |  |  |  |  |

| The number of CUs            | 8                                                           |  |  |  |  |  |  |

| Number of SIMD units per CU  | 4                                                           |  |  |  |  |  |  |

| Max wavefronts per SIMD unit | 10                                                          |  |  |  |  |  |  |

| Vector register size per CU  | 256KB                                                       |  |  |  |  |  |  |

| The number of compute queues | 128                                                         |  |  |  |  |  |  |

| CPU Clock                    | 4000MHz                                                     |  |  |  |  |  |  |

| # CPUs                       | 2                                                           |  |  |  |  |  |  |

| GPU L1-D\$ per CU            | 16 KB, 64B line                                             |  |  |  |  |  |  |

| GPU L1-I\$ per 2 CUs         | 32KB, 64B line, 16 way                                      |  |  |  |  |  |  |

| GPU L2 cache per 64 CUs      | 4MB, 64B line                                               |  |  |  |  |  |  |

| Main Memory                  | 16 GB DDR4 [92], 16 channels, 16 banks/channel,<br>1000 MHz |  |  |  |  |  |  |

|                              | 1000 MHZ                                                    |  |  |  |  |  |  |

| Table 3: Scheduling Policie | s. |

|-----------------------------|----|

|-----------------------------|----|

| Scheduler Description    |                                                                   |  |  |  |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                          | Prior CPU-Side Scheduling                                         |  |  |  |  |  |  |  |  |

| BatchMaker (BAT) [28]    | A dynamic batching technique where each stream can have a         |  |  |  |  |  |  |  |  |

|                          | different batch size.                                             |  |  |  |  |  |  |  |  |

| Baymax (BAY) [54]        | Uses pre-trained models to predict a jobs execution time and      |  |  |  |  |  |  |  |  |

|                          | re-orders the priorities of jobs based on their QoS headroom.     |  |  |  |  |  |  |  |  |

| Prophet (PRO) [53]       | Uses offline profiling to choose which concurrent jobs to issue   |  |  |  |  |  |  |  |  |

|                          | in order to fully utilize the GPU and improve QoS.                |  |  |  |  |  |  |  |  |

|                          | orary GPU Command Processor Scheduling                            |  |  |  |  |  |  |  |  |

| Round-Robin (RR)         | The baseline scheduler that processes compute queues in a cy-     |  |  |  |  |  |  |  |  |

|                          | clic manner.                                                      |  |  |  |  |  |  |  |  |

| Advano                   | ced GPU Command Processor Scheduling                              |  |  |  |  |  |  |  |  |

| Multi-Level Feedback     | Moves jobs between two priority queues based on their runtime     |  |  |  |  |  |  |  |  |

| Queue (MLFQ) [64]        | and uses RR to schedule jobs in the high priority queue.          |  |  |  |  |  |  |  |  |

| Earliest Deadline First  | A dynamic scheduling policy that schedules kernels from the       |  |  |  |  |  |  |  |  |

| (EDF) [91]               | job with the earliest deadline first.                             |  |  |  |  |  |  |  |  |

| Shortest-Job First (SJF) | A static scheduling policy that schedules kernels with the short- |  |  |  |  |  |  |  |  |

|                          | est job first.                                                    |  |  |  |  |  |  |  |  |

| Shortest Remaining Time  | A dynamic policy that uses LAX's remaining execution time         |  |  |  |  |  |  |  |  |

| Job First (SRF)          | estimator to assign job priorities. It then assigns the job with  |  |  |  |  |  |  |  |  |

|                          | the shortest estimated remaining time the highest priority.       |  |  |  |  |  |  |  |  |

| Longest-Job First (LJF)  | A static scheduling policy that schedules kernels from the long-  |  |  |  |  |  |  |  |  |

|                          | est jobs first.                                                   |  |  |  |  |  |  |  |  |

| PREMA [79]               | A multi-task scheduler for heterogeneous systems that predicts    |  |  |  |  |  |  |  |  |

|                          | job priorities and preempts lower priority jobs.                  |  |  |  |  |  |  |  |  |

|                          | osed Laxity-Aware Scheduling Variants                             |  |  |  |  |  |  |  |  |

| LAX                      | Our laxity-aware scheduling policy described in Section 4.        |  |  |  |  |  |  |  |  |

| LAX-SW                   | A variant of LAX that uses CPU-side scheduling.                   |  |  |  |  |  |  |  |  |

| LAX-CPU                  | A variant of LAX that does CPU-side scheduling but changes        |  |  |  |  |  |  |  |  |

|                          | the API to allow rapid changing of the priority of the jobs.      |  |  |  |  |  |  |  |  |

BAY, and PRO incur overheads for communicating between the CPU and GPU. For a tightly coupled GPU like the one in our system, this adds 4  $\mu$ s of host-device communication overhead per kernel in a job. Similarly, we add 50  $\mu$ s of overhead to BAY for calls to its regression model, based on reported data [54].

Modern GPUs perform deadline-blind RR scheduling (Section 2.1), but since the CP is programmable (although GPU vendors have not disclosed an API), it is possible to extend the CP for other widely used schedulers like LJF, MLFQ, SJF, and SRF. Like LAX, SJF, SRF, and LJF utilize predicted runtime information to decide what to schedule; however, they do not model queuing delay or laxity. MLFQ performed better with two priority levels, demoting jobs to lower priority level [64] when runtime exceeds 1/3 of the jobs' deadline, and promoting back to the higher priority when its runtime exceeded 2/3 of its deadline. We also compare against EDF [91], which prioritizes the job with the earliest deadline. Although some EDF implementations strictly ensure that the job(s) with the earliest deadline is always executing, this requires preemption. For jobs with longer deadlines such as those studied in prior work [91], this context switching overhead can be amortized. However, given the short deadlines in our workloads and the fine-grained scheduling granularity we use, strict EDF with preemption would perform poorly. For example, prior work assumes preemption incurs around 1 ms of overhead [91], which exceeds some of our workload's deadlines (CUCKOO, IPV6, and STEM) and consumes a significant portion of the deadline for the remainder (GMM and the RNNs). Thus, we instead implement EDF by prioritizing jobs with the earliest deadlines first, without preemption.

Finally, we compare against PREMA, which utilizes userdefined prioritizes and slowdown calculations to preempt lower priority jobs [79]. Like the authors, we use a 250 µs preemption interval. Although PREMA was designed for TPUs running a single, large job, we extended it to run multiple jobs since our workloads do not fully utilize the GPU. We also extended PREMA to use LAX's frequent updates for PREMA's calculations.

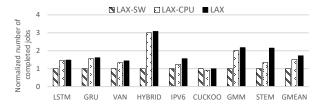

Finally, since LAX changes multiple components (Section 4), we also design the three variants to identify if laxity-aware scheduling could provide the same benefits without extending the CP: LAX, which extends the CP as discussed in Section 4; LAX-SW, which performs CPU-side scheduling (and incurs overheads for host-device communication); and LAX-CPU, which also does CPU-side scheduling, but changes the API to allow dynamic job priority updates from user-level software. To do this, we update the API to write updated priorities to memory-mapped registers that control each queue's priorities [29]. Finally, for all LAX variants we initialize the job priority to the highest priority, as this empirically gave the best results.<sup>2</sup>

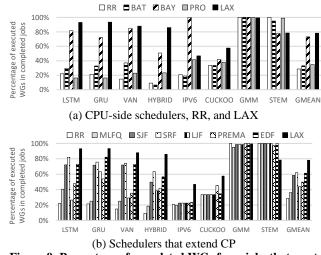

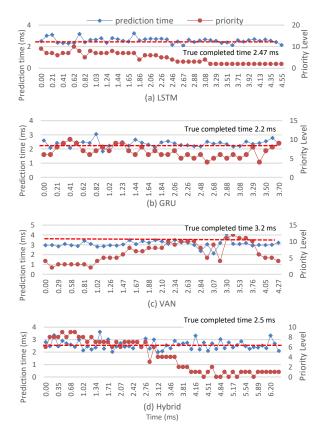

# 5.2 Benchmarks

To evaluate the schedulers, we use the eight latency-sensitive benchmarks discussed in Section 3. Table 4 details their input size, deadline, and arrival rates. Where available, we use deadlines from recent work: 7 ms for RNNs [2][3][28][31], 40  $\mu$ s for IPV6 [61][63], and 600  $\mu$ s for Cuckoo [61]. For the many-kernel RNNs, deadlines are set for the entire multi-layer computation. For the IPA benchmarks, we used the same methodology as the authors: we ran each benchmark in isolation, then doubled the worst case latency [53][54]. LAX does not affect latency-insensitive applications because the programmer does not provide a deadline for them.

To demonstrate how GPUs can simultaneously execute kernels with different degrees of parallelism, we also include a Hybrid RNN benchmark that includes the two most popular RNN variants, LSTM and GRU, with a mixed hidden layer size of 128 and 256, respectively. The input for all RNNs is based on the WMT '15 language translation trace [47], which has an average sequence length of 16. Furthermore, we share weight data across RNN inference jobs with the same hidden size [6][28]. Although our technique is applicable to any data

| Benchmark Deadline Input / hid-<br>den layer Bize (jobs/s)<br>Many Kernels per Job<br>LSTM [12][13] 7 ms 128 8000 5000 3000<br>VAN [12][13] 7 ms 128 8000 5000 3000<br>VAN [12][13] 7 ms 128 8000 5000 3000<br>VAN [12][13] 7 ms 128 256 8000 5000 3000<br>Few Kernels per Job<br>PV6 [61]-[63] 40 µs 8192 64000 32000 16000<br>CUCKOO [61]-[63] 600 µs 8192 8000 5000 3000<br>GMM [65][70] 300 µs 8192 8000 5000 3000<br>STEM [65][70] 300 µs 8192 8000 5000 3000<br>STEM [65][70] 300 µs 8192 8000 5000 3000<br>GMM [65][70] 300 µs 4096 64000 32000 16000<br>STEM [65][70] 300 µs 4096 64000 32000 16000<br>LSTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN<br>(a) High job arrival rate<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |          |          |              |              |              |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|----------|--------------|--------------|--------------|-------------|

| Image: size         (jobs/s)         (jobs/s)         (jobs/s)           LSTM [12][13]         7 ms         128         8000         5000         3000           GRU [12][13]         7 ms         128         8000         5000         3000           VAN [12][13]         7 ms         128         8000         5000         3000           VAN [12][13]         7 ms         128/256         8000         5000         3000           Few Kernels per Job         IPV6 [61]-[63]         40 μs         8192         64000         32000         16000           CUCKOO [61]-[63]         600 μs         8192         8000         5000         3000           STEM [65][70]         3 ms         2048         32000         16000         8000           STEM [65][70]         300 μs         4096         64000         32000         16000           STEM [65][70]         300 μs         4096         64000         32000         16000           Stem [65][70]         300 μs         4096         64000         32000         16000           Stem [65][70]         GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN         (a) High job arrival rate         10         10         10         10         10         10                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |          |          | Input / hid- | High Job Ar- | Medium Job   | Low Job Ar- |

| Many Kernels per Job           LSTM [12][13]         7 ms         128         8000         5000         3000           GRU [12][13]         7 ms         128         8000         5000         3000           VAN [12][13]         7 ms         128         8000         5000         3000           HYBRID [12][13]         7 ms         128/256         8000         5000         3000           HYBRID [12][13]         7 ms         128/256         8000         5000         3000           IPV6 [61]-[63]         40 µs         8192         64000         32000         16000           GRM [65][70]         3 ms         2048         32000         16000         8000           Stem [65][70]         300 µs         4096         64000         32000         16000           Stem [65][70]         300 µs         4096         64000         32000         16000           LSTM         GRU         VAN         HYBRID         IPV6 CUCKOO GMM STEM GMEAN<br>(a) High job arrival rate           10         ISTM         GRU         VAN         HYBRID         IPV6 CUCKOO GMM STEM GMEAN<br>(b) Medium job arrival rate           10         ISTM         GRU         VAN         HYBRID         IPV6 CUC                                                                                                                                                                                                                                                                                                                                                                                                                                        | Benchr            | nark     | Deadline |              | rival Rate   | Arrival Rate | rival Rate  |

| LSTM [12][13] 7 ms 128 8000 5000 3000<br>GRU [12][13] 7 ms 128 8000 5000 3000<br>VAN [12][13] 7 ms 128 256 8000 5000 3000<br>Few Kernels per Job<br>IPV6 [61]-[63] 40 µs 8192 64000 32000 16000<br>CUCKOO [61]-[63] 600 µs 8192 8000 5000 3000<br>GMM [65][70] 300 µs 4096 64000 32000 16000 8000<br>STEM [65][70] 300 µs 4096 64000 32000 16000<br>STEM [65][70] 300 µs 4096 64000 32000 16000<br>LSTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN<br>(a) High job arrival rate<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |          |          |              |              | (jobs/s)     | (jobs/s)    |

| GRU [12][13]         7 ms         128         8000         5000         3000           VAN [12][13]         7 ms         256         8000         5000         3000           HYBRID [12][13]         7 ms         128/256         8000         5000         3000           HYBRID [12][13]         7 ms         128/256         8000         5000         3000           HYBRID [12][13]         7 ms         128/256         8000         5000         3000           IPV6 [61]-[63]         40 µs         8192         8000         5000         3000           CUCKOO [61]-[63]         600 µs         8192         8000         5000         8000           STEM [65][70]         300 µs         4096         64000         32000         16000           STEM [65][70]         300 µs         4096         64000         32000         16000           10         Intermediation of the main of                                                                                                                                                                                                                                |                   |          | N        | Aany Kernels | s per Job    |              |             |

| VAN [12][13]         7 ms         256         8000         5000         3000           HYBRID [12][13]         7 ms         128/256         8000         5000         3000           Few Kernels per Job         Few Kernels per Job         1000         32000         16000         3000           CUCKOO [61]-[63]         40 µs         8192         8000         5000         3000           GMM [65][70]         3 ms         2048         32000         16000         8000           STEM [65][70]         300 µs         4096         64000         32000         16000           Step of failed and the step of failed |                   |          |          | 128          | 8000         | 5000         | 3000        |

| HYBRID [12][13]       7 ms       128/256       8000       5000       3000         Few Kernels per Job         IPV6 [61]-[63]       40 μs       8192       64000       32000       16000         GMM [65][70]       3 ms       2048       32000       16000       8000         Stem [65][70]       3 00 μs       4096       64000       32000       16000         10       14 20       IRR BAT DBAY PROLAX       IAN       IAN       IAN         10       14 20       IRR BAT DBAY PROLAX       IAN       IAN         10       ISTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN       (a) High job arrival rate       IAN         10       ISTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN       (b) Medium job arrival rate         10       ISTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN       (b) Medium job arrival rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GRU [12][1        | 3]       | 7 ms     | 128          | 8000         | 5000         | 3000        |

| Few Kernels per Job           IPV6 [6]]-[63]         40 µs         8192         64000         32000         16000           CUCKOO [6]-[63]         600 µs         8192         8000         5000         3000           GMM [65][70]         3 ms         2048         32000         16000         8000           STEM [65][70]         300 µs         4096         64000         32000         16000           10         14 20         RR<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |          | 7 ms     |              | 8000         | 5000         | 3000        |

| IPV6 [61]-[63]         40 μs         8192         64000         32000         16000           CUCKOO [61]-[63]         600 μs         8192         8000         5000         3000           GMM [65][70]         3 ms         2048         32000         16000         8000           STEM [65][70]         300 μs         4096         64000         32000         16000           10         1420         RR         BAT         BAY         PRO         LAX           10         10         1420         RR         BAT         BAY         PRO         LAX           10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HYBRID [1         | 2][13]   |          |              |              | 5000         | 3000        |

| CUCKOO         [61]-[63]         600 µs         8192         8000         5000         3000           GMM [65][70]         3 ms         2048         32000         16000         8000           STEM [65][70]         300 µs         4096         64000         32000         16000           10         14         20         RR         BAT         BAY         PRO         LAX           10         10         14         20         RR         BAT         BAY         PRO         LAX           10         10         10         14         20         RR         BAT         BAY         PRO         LAX           10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10         10 <td></td> <td></td> <td></td> <td></td> <td>per Job</td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |          |          |              | per Job      | -            | -           |

| GMM [65][70] 3 ms 2048 32000 16000 8000<br>STEM [65][70] 300 µs 4096 64000 32000 16000<br>14 20 □ RR ■ BAT Ø BAY □ PRO ■ LAX<br>10<br>10<br>14 20 □ RR ■ BAT Ø BAY □ PRO ■ LAX<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |          |          |              |              |              |             |

| STEM [65][70] 300 µs 4096 64000 32000 16000<br>14 20 RR BAT BAY PRO LAX<br>14 20 RR BAT BAY PRO LAX<br>10 LAX<br>10 LSTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN<br>(a) High job arrival rate<br>10 LSTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN<br>(b) Medium job arrival rate<br>10 LSTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN<br>(b) Medium job arrival rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |          |          |              |              |              |             |

| 14 20 DRR BAT BAY PRO LAX<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |          |          |              |              |              |             |

| bind bind bind bind bind bind bind bind                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | STEM [65][        | 70]      | 300 µs   | 4096         | 64000        | 32000        | 16000       |

| (a) High job arrival rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |          |          |              | n n-PA       |              | n-Pn        |

| (b) Medium job arrival rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |          |          |              | na_na_na%n   |              |             |

| 10<br>S 8<br>S 8<br>S 8<br>S 8<br>S 8<br>S 8<br>S 8<br>S 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Z                 | LSTIM    | GRU VA   |              |              |              | GIVIEAN     |

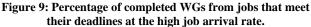

| LSTM GRU VAN HYBRID IPV6 CUCKOO GMM STEM GMEAN<br>(c) Low job arrival rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |          |          |              |              |              |             |