|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Homework 4 [Due at lecture on Fri, Oct 10]

Primary contact for this homework: Sujith Surendran [sujiths at cs dot wisc dot edu]

You must do this homework alone. Please hand in the copy of the homework listing your section number, full name (as appear in Learn@UW) and UW ID. You must staple all pages of your homework together to receive full credit.

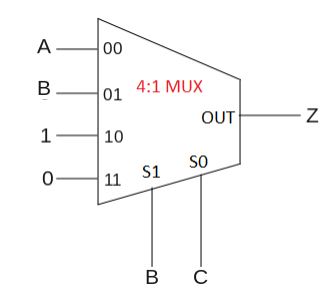

Fill in the truth table (Table 1) for the following combinational circuit that uses 4:1 multiplexer. A,B,C are inputs to this combinational circuit and the output of the combinational circuit is Z.

Implement a logic circuit for a 2-input XOR gate using a decoder and a 2-input OR gate. The XOR gate takes inputs A, B and produces an output Z as per the following truth table:

Consider a finite state machine (FSM) that recognizes the pattern "1000". The input to the FSM is a sequence of binary bits, one after the other. When the FSM receives 1000 as inputs in successive bits, it should output 1. Otherwise, the output should be 0.

Consider a 512 MB memory with 16-bit address. What is the addressability of this memory?

Consider a machine which implements an ISA in which every instruction is 32 bits long and has the following format:

Given that an instruction takes 4 cycles to complete execution in a machine which has a clock period of 10 ns, find the following:

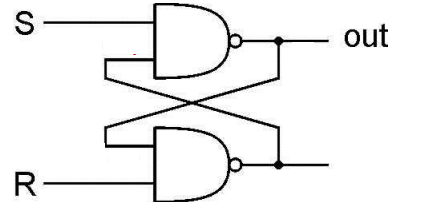

An RS latch is shown in the figure below. Assuming that the inputs to this R-S latch are changed every second (as shown in Table 2), specify what would be the value of "out" signal for each of these sets of inputs.

What is the difference between a sequential circuit and a combinational circuit ?

|