|

|

|||||||||||||||||||||||||||||||||||||||||||

Homework 4 [Due at lecture on Mon, March 4]

Primary contact for this homework: Pradip Vallathol [pradip16 at cs dot wisc dot edu]

You should do this homework in groups of two. Please write the full name and the student id of each member on every page and staple multiple pages together.

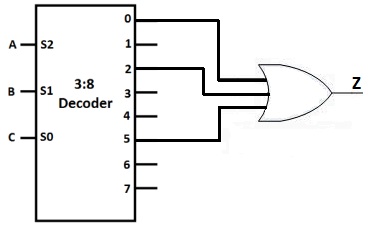

Implement the following truth table, in which A, B and C are in the inputs and Z is the output, using a 3:8 decoder and a 3-input OR gate. Use Figure 1 to represent the 3:8 decoder.

Suppose the number of address bits in memory is decreased by 8 bits and the addressability is doubled. By what factor has the size of memory changed relative to the original one?

2-7

An instruction takes 7 cycles to execute in a processor with a clock frequency of 70 MHz. Find the following:

1/(clock frequency) = 10-7/ 7

(70 * 106 cycles/second) / (7 cycles/instruction) = 107 instructions/second

(250 instructions) / (107 instructions/second) = 2.5 * 10-5 seconds

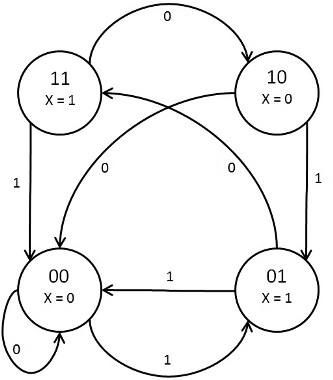

Consider the State Diagram shown below. Each state is denoted as a 2-bit value, the values on the arrows represent the input, and X in each state represents the output.

Number of flops needed = Number of bits used to represent a state = 2

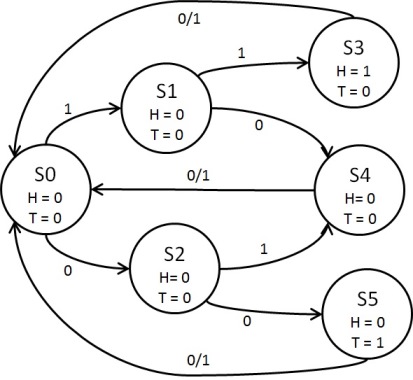

Design a Moore finite state machine (FSM) that counts the number of Heads and Tails in 2 consecutive tosses of a fair coin. The input to the FSM is a sequence of bits, where 1 represents a Head and 0 represents a Tail. After each toss, the FSM should output a 1-bit value (H) which specifies if it has seen 2 Heads and a 1-bit value (T) which specifies if it has seen 2 Tails. After every second toss, the next toss resets the system, i.e., the outputs H and T are set to 0, irrespective of whether the result of that toss is a Head or a Tail.

S0 is the start state

Consider a machine which implements an ISA in which every instruction is 20 bits long and has the following format:

Where DR = Destination register, SR1 = Source Register 1, and SR2 = Source register 2. The fields DR, SR1 and SR2 are represented using the same number of bits.

25 = 32

Number of bits to represent a register = 12/3 = 4

Number of bits for DR, SR1 and SR2 = 20 - 5 = 15

Consider the 6 stage Instruction Cycle as discussed in the lecture (or Section 4.3.2 or your textbook). The time taken to execute a stage of the Instruction cycle is defined as follows:

Fetch = 10

Fetch = 10

Fetch = 10

|