# Computer Organization

For Everyone

Shayne Wadle and Karthikeyan Sankaralingam

# Contents

|                                    |    |

|------------------------------------|----|

| 1 The Big Ideas of Computing       | 5  |

| 2 Bits and Representation          | 9  |

| 3 Digital Logic                    | 31 |

| 4 Von Neumann Architecture         | 53 |

| 5 Elements of an ISA               | 57 |

| 6 Assembly Language                | 61 |

| 7 Programming in Assembly Language | 65 |

| 8 Input and Output                 | 69 |

| About the Author                   | 73 |

# 1 The Big Ideas of Computing

Welcome to the study of computer organization! Before we dive into the nuts and bolts of bits, bytes, and processors, we need to start with the foundational concepts that make computers possible. What *is* a computer, really? And how can a machine built from simple on/off switches perform tasks of such breathtaking complexity?

The answer lies in a handful of profound “Big Ideas.” These are the pillars upon which the entire digital world is built. Understanding them gives you a framework for everything that follows in this book.

## Big Idea #1: The Universal Computing Machine

In the 1930s, long before physical computers existed, a brilliant mathematician named **Alan Turing** asked a powerful question: Is there a limit to what can be computed? He devised a thought experiment to answer this, and in doing so, designed the theoretical blueprint for every computer that would ever be built.

He imagined a simple machine:

- An infinitely long **tape**, divided into cells, each containing a symbol (like a 0, 1, or blank).

- A **head** that can read the symbol in a cell, write a new symbol, and move left or right on the tape.

- A set of **rules** that tells the head what to do based on the machine’s current state and the symbol it just read.

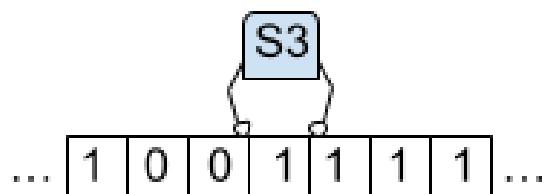

Figure 1.1: A Turing Machine head moving along the infinite tape following rule S3 currently.

This theoretical device, the **Turing Machine**, seems primitive. Yet, Turing proved something astonishing: this simple machine could compute *any* problem that was computable by *any* conceivable machine. It is a **universal computing machine**. This principle is now called **Turing Completeness**. If a system (like a programming language or a processor) is Turing complete, it has the power to simulate any other Turing machine—meaning it can compute anything that is fundamentally computable.

This is the bedrock of all modern computing: we don't need a special machine for calculating finances, another for playing music, and a third for editing photos. A single, universal machine can do it all.

## Big Idea #2: The Stored-Program Computer

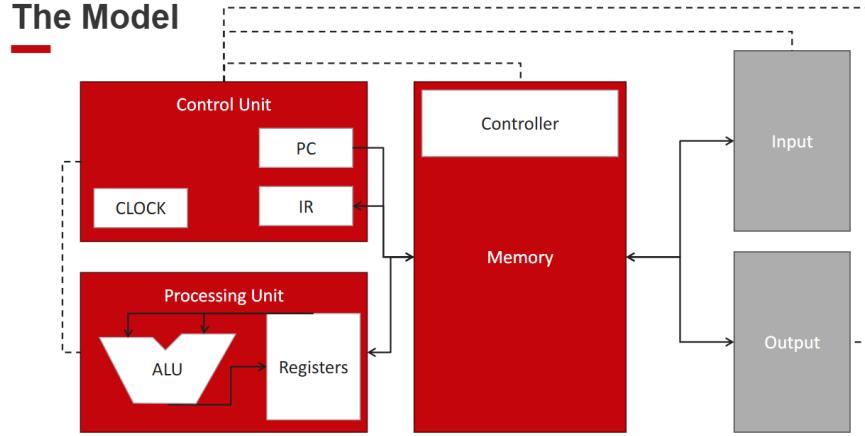

Turing's machine was a theoretical concept. The practical leap forward was the idea of a **programmable computer**, where the instructions (the program) could be easily changed. The key innovation that made this possible is the **stored-program concept**: the idea that the instructions for the computer are stored in memory, right alongside the data the instructions operate on.

This means the program isn't physically wired into the machine; it's just data. To change what the computer does, you simply load a different program into its memory. This simple but powerful idea is the defining characteristic of every modern computer. This concept has evolved over time:

- The **Atanasoff-Berry Computer (ABC)** (early 1940s) is often considered the first electronic digital computing device, taking early steps toward this goal.

- **ENIAC** (mid-1940s) was a huge leap in speed, but it had to be physically rewired to change its program, a tedious process that could take days.

- The **IBM System/360** (1960s) introduced the idea of a family of computers that could all run the same programs (software), cementing the stored-program model in the commercial world.

- The **Intel 8086** processor (late 1970s) launched the personal computer (PC) revolution, bringing the power of the stored-program computer into homes and offices.

- **ARM** processors (popularized in the 2000s) powered the smartphone revolution with their efficient design, putting a powerful stored-program computer in billions of pockets.

- Modern **Deep Learning chips (GPUs, TPUs)** are specialized processors designed to execute the mathematical operations needed for AI at incredible speeds.

All these machines, from the room-sized ENIAC to the chip in your phone, share the same fundamental DNA: they are all implementations of the stored-program computer.

## Big Idea #3: Specialization vs. Generality

If a single machine can do everything, why would we ever build one that can't? The answer is a classic engineering trade-off: **efficiency**. A general-purpose, programmable computer is flexible, but a specialized, **fixed-function** device that does only one task can be much faster, cheaper, and more power-efficient.

You're surrounded by fixed-function computers: the chip in your microwave, a simple pocket calculator, or the controller for your car's anti-lock brakes. A modern, high-stakes example is a **Bitcoin mining chip like the BM1370**. Its one and only job is to perform a specific cryptographic calculation (SHA-256) over and over, as fast as humanly possible. It can't run a web browser or a word processor, but it can perform its one task millions of times more efficiently than a general-purpose CPU.

## Big Idea #4: New Frontiers in Computation

For decades, the stored-program model has been the undisputed king. But today, we are exploring fundamentally new types of computing.

- **Quantum Computing:** This is a completely different model built on the strange rules of quantum mechanics. Instead of bits (0 or 1), it uses **qubits**, which can be 0, 1, or a superposition of both at the same time. This allows quantum computers to explore a vast number of possibilities simultaneously, making them potentially millions of times faster for specific problems like materials science and code-breaking.

- **Deep Learning:** This represents a new way of *creating* a program. Instead of a human writing explicit rules (an algorithm), a program called a **model** is *generated* by training it on massive amounts of data. The model itself—a giant collection of numbers—becomes the program. You interact with it using **prompts**, which are a new kind of input that directs this learned program. While the theory is still evolving, it's important to remember that these powerful DL models are still *created by* and *run on* the stored-program computers we will be studying.

## The Overarching Idea: Abstraction

So how do we manage all this complexity? A modern processor has billions of transistors. An operating system has millions of lines of code. No single person can possibly understand every detail. The magic that makes this all work is **abstraction**.

**Abstraction** is the process of hiding complex details behind a simple model, or interface. This allows us to build complex systems in layers, where each layer only needs to understand the layer immediately below it, not all the details beneath.

The key to abstraction is separating the **interface** (the *what*) from the **implementation** (the *how*).

- **Interface:** A set of simple rules and guarantees about what a system can do.

- **Implementation:** The complex, hidden details of how the system actually does it.

## 1 The Big Ideas of Computing

Think about driving a car. The **interface** is the steering wheel, pedals, and gear shift. You know that pressing the accelerator makes the car go faster. The **implementation** is the engine, fuel injectors, transmission, and exhaust system. You don't need to know anything about internal combustion to drive to the store. The simple interface hides the complex implementation.

Computers are built on layers and layers of abstraction. A programmer doesn't think about individual transistors; they use a programming language (an abstraction). The language is converted to machine instructions (another abstraction), which are executed by processor components (another abstraction), which are built from logic gates (another abstraction), which are finally built from transistors.

This book is a journey through these layers of abstraction, starting from the bottom up. We will focus on the dominant model of computing—the **programmable, stored-program computer**—and see how these powerful ideas work in practice.

### Cheatsheet: The Big Ideas

- **Universal Computation:** The concept of a **Turing Machine** proved that a single, simple machine could theoretically solve any computable problem. This property is called **Turing Completeness**.

- **The Stored-Program Computer:** The defining feature of modern computers. The **instructions (software) are stored in memory** just like data, which allows the computer's function to be changed easily.

- **Specialization vs. Generality:** This is the fundamental trade-off between a flexible, **general-purpose** computer (like a CPU) and a highly efficient but inflexible **fixed-function** device (like a Bitcoin mining chip).

- **Abstraction:** The essential technique for managing complexity. It involves hiding the complex details (**implementation**) behind a simple set of rules or guarantees (**interface**). This allows us to build incredibly complex systems in layers.

- **New Frontiers:** New computing paradigms are emerging. **Quantum Computing** uses qubits to solve certain problems exponentially faster, while **Deep Learning** creates “programs” (models) by learning from data rather than being explicitly programmed.

# 2 Bits and Representation

## The Digital Universe: It's All About the Bits

Take a moment to think about your digital world. The music you stream, the high-definition videos you watch, the photos you share, the very words you are reading right now—all of it seems incredibly complex and diverse. Yet, at the most fundamental level inside any computer, all of this information is stored and processed in the exact same way: as a massive collection of simple, tiny switches. The state of these switches, either **on** or **off**, is the basic language of the computer. Our first step in understanding how a computer works is to learn this language, which begins with a single concept: the bit.

### What is a Bit?

A **bit**, short for **binary digit**, is the smallest and most basic unit of information in computing. A bit can only have one of two possible values, which we represent with the symbols **0** and **1**.

You can think of a bit like a light switch. It can either be in the “off” position (0) or the “on” position (1). There are no other possibilities. This two-state system is the foundation upon which all digital information is built.

- **0:** Represents off, false, low voltage.

- **1:** Represents on, true, high voltage.

Image of a single light switch in the off position labeled '0' and on position labeled '1'

A single bit by itself isn’t very useful; it can only answer a yes/no question. To represent more complex information, we need to group bits together.

### Grouping Bits to Represent More Information

If we use two bits, we can represent four unique combinations:

00    01    10    11

With three bits, we can create eight unique combinations:

000    001    010    011    100    101    110    111

## 2 Bits and Representation

Notice the clear pattern emerging? Every time we add a new bit, we double the number of unique things we can represent. This relationship can be expressed with a simple formula:

### Core Principle

With **n** bits, you can represent  $2^n$  unique things.

This exponential growth is the key to a computer's power. For example, a group of 8 bits, known as a **byte**, can represent  $2^8 = 256$  different things.

When we write down a string of bits, which we call a **binary string**, there is a standard convention. We write the bits in order of their position, or index. For a 4-bit string, we might label the bits as follows:

$$b_3 b_2 b_1 b_0$$

By convention, the rightmost bit,  $b_0$ , is called the **least significant bit (LSB)**, and the leftmost bit,  $b_3$ , is the **most significant bit (MSB)**. For now, don't think of these strings as numbers. Think of them simply as unique patterns. For example, if a grocery store sold 11 types of fruit, we couldn't give each fruit a unique 3-bit code (since  $2^3 = 8$  is not enough). However, we could use 4-bit codes (since  $2^4 = 16$  is more than enough). We could assign 'apple' the code 0000, 'banana' the code 0001, and so on.

### A Glimpse into Quantum Computing: The Qubit

While this textbook focuses on classical computers, it's worth knowing about a fascinating development in computing. **Quantum computers** don't use bits; they use **qubits**. Unlike a bit, which must be either a 0 or a 1, a qubit can exist in a state of **superposition**, meaning it can be a combination of both 0 and 1 *at the same time*.

This property gives quantum computers immense potential power. A system of  $n$  classical bits can only represent *one* of  $2^n$  possible values at any given moment. A system of  $n$  qubits, however, can represent all  $2^n$  values simultaneously! This allows them to tackle certain problems—like code-breaking and molecular simulation—that are impossible for even the most powerful classical supercomputers.

## What's Next?

We've established that we can use groups of bits to represent a collection of unique items. This is a powerful idea, but to build a computer, we need to represent something more structured and universally useful. In the following sections, we will explore how these simple strings of 0s and 1s form the foundation for representing numbers, characters, and other data types that are the bedrock of all computation.

## Cheatsheet: Key Takeaways

- A **bit** (binary digit) is the smallest unit of data in a computer and can have one of two values: 0 or 1.

- The fundamental formula: with **n** bits, you can represent  $2^n$  unique patterns or values.

- A **byte** is a group of 8 bits and can represent  $2^8 = 256$  different values.

- In a binary string (e.g.,  $b_3b_2b_1b_0$ ), the rightmost bit ( $b_0$ ) is the **Least Significant Bit (LSB)** and the leftmost bit ( $b_3$ ) is the **Most Significant Bit (MSB)**.

## Representing Numbers: Integers

Now that we understand that bits can represent unique patterns, let's apply this to something concrete: representing numbers. The most fundamental type of number in computing is the **integer**. Before we dive into how binary is used, let's revisit how our familiar decimal number system works.

### The Power of Position: Decimal and Binary

When we write the number '743' in the decimal (base-10) system, we intuitively understand that the position of each digit matters. The '3' is in the ones place, the '4' is in the tens place, and the '7' is in the hundreds place. This is called a **weighted positional notation**. Each position has a weight that is a power of 10.

$$743 = (7 \times 10^2) + (4 \times 10^1) + (3 \times 10^0)$$

$$743 = (7 \times 100) + (4 \times 10) + (3 \times 1) = 700 + 40 + 3$$

The binary system works on the exact same principle, but the base is 2 instead of 10. Each position's weight is a power of 2.

### Unsigned Integers

The most straightforward way to represent an integer is as an **unsigned integer**, which means it can only represent non-negative values (zero and positive numbers). To find the value of an unsigned binary number, you simply sum the weights of the positions that contain a '1'.

For example, let's find the value of the 4-bit binary number '1101':

$$1101_2 = (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0)$$

$$1101_2 = (1 \times 8) + (1 \times 4) + (0 \times 2) + (1 \times 1)$$

$$1101_2 = 8 + 4 + 0 + 1 = 13_{10}$$

With  $n$  bits, we can represent any integer from 0 (all bits are 0) to  $2^n - 1$  (all bits are 1).

### The Problem of Negativity: Signed Integers

Unsigned numbers are great, but we often need to represent negative values. How can we do this with only 0s and 1s? The most obvious approach is to reserve one bit, typically the **most significant bit (MSB)**, to represent the sign. This bit is called the **sign bit**. By convention, a '0' in the sign bit means the number is positive, and a '1' means it is negative. The remaining bits represent the number's magnitude (its absolute value). This method is called **Sign and Magnitude**.

For example, with 4 bits:

- '0101' represents +5 (sign bit is 0, magnitude is  $101_2 = 5$ ).

- '1101' represents -5 (sign bit is 1, magnitude is  $101_2 = 5$ ).

However, this simple approach has two major flaws:

1. **Two Zeros:** '0000' represents +0, and '1000' represents -0. Having two different patterns for the same value is inefficient and complicates the computer's hardware.

2. **Difficult Arithmetic:** The hardware for addition and subtraction becomes very complex, as it has to check the signs before performing an operation. If you try to add +5 and -5 ('0101 + 1101'), simple column-wise addition does not work: you get '10010' which does not match the expected result of '0000'.

### A Better Way: Complements

To solve the problems with sign and magnitude, computer scientists developed complement systems. The goal was to make arithmetic simple and have only one representation for zero.

#### One's Complement

In a **one's complement** system, positive numbers are represented just like in sign and magnitude. To get the negative representation of a number, you simply **flip every bit**. This is called taking the complement.

- To represent +5: 0101

- To get -5: Flip every bit of 0101 → 1010

This system makes some arithmetic easier, but it still suffers from one major flaw: it has two representations for zero. 0000 is +0, and if you flip all its bits, you get 1111, which represents -0.

## Two's Complement: The Gold Standard

This brings us to **two's complement**, the system used by virtually all modern computers. It is elegant, efficient, and solves the problems of the previous systems.

To get the negative of a number in two's complement:

1. **Flip every bit** (like one's complement).

2. **Add 1.**

Let's find the representation of  $-5$  using 4 bits:

1. Start with  $+5$ : 0101

2. Flip all the bits: 1010

3. Add 1:  $1010 + 1 = 1011$ .

So, 1011 represents  $-5$  in two's complement.

Why is this so powerful?

- **One Zero:** There is only one representation for zero (0000). If we try to negate 0000, we flip the bits (1111) and add 1, which results in (1)0000. The carry bit is discarded, leaving 0000.

- **Simple Arithmetic:** Addition works for both positive and negative numbers without any special logic. Let's add  $+5$  and  $-5$ :

$$\begin{array}{r} 0101 \quad (+5) \\ + 1011 \quad (-5) \\ \hline (1)0000 \quad (0, \text{ after discarding the carry bit}) \end{array}$$

The hardware for addition now automatically handles subtraction. The system works perfectly. We will shortly explain more about this carry bit - it's similar to the carryover of addition in decimal numbers.

## Integer Representation Tables

The following tables compare the values represented by the same binary strings using the different systems we've discussed.

Table 2.1: 3-Bit Integer Representations

| Binary String | Unsigned | Sign & Mag. | One's Comp. | Two's Comp. |

|---------------|----------|-------------|-------------|-------------|

| 000           | 0        | +0          | +0          | +0          |

| 001           | 1        | +1          | +1          | +1          |

| 010           | 2        | +2          | +2          | +2          |

| 011           | 3        | +3          | +3          | +3          |

| 100           | 4        | -0          | -3          | -4          |

| 101           | 5        | -1          | -2          | -3          |

| 110           | 6        | -2          | -1          | -2          |

| 111           | 7        | -3          | -0          | -1          |

Table 2.2: 4-Bit Integer Representations

| Binary String | Unsigned | Sign & Mag. | One's Comp. | Two's Comp. |

|---------------|----------|-------------|-------------|-------------|

| 0111          | 7        | +7          | +7          | +7          |

| 0110          | 6        | +6          | +6          | +6          |

| ...           | ...      | ...         | ...         | ...         |

| 0001          | 1        | +1          | +1          | +1          |

| 0000          | 0        | +0          | +0          | +0          |

| 1111          | 15       | -7          | -0          | -1          |

| 1110          | 14       | -6          | -1          | -2          |

| ...           | ...      | ...         | ...         | ...         |

| 1001          | 9        | -1          | -6          | -7          |

| 1000          | 8        | -0          | -7          | -8          |

### Cheatsheet: Integer Ranges for n Bits

- **Unsigned:** Can represent  $2^n$  numbers.

- Range: 0 to  $2^n - 1$

- **Sign and Magnitude:** Has two zeros.

- Range:  $-(2^{n-1} - 1)$  to  $+(2^{n-1} - 1)$

- **One's Complement:** Has two zeros.

- Range:  $-(2^{n-1} - 1)$  to  $+(2^{n-1} - 1)$

- **Two's Complement:** The standard. Has one zero and an asymmetric range.

- Range:  $-2^{n-1}$  to  $+(2^{n-1} - 1)$

## Operations on Bits and Numbers

We've now established how to represent both positive and negative integers using bits. The next logical step is to perform operations on them. In this section, we'll cover how to convert between the number systems we've learned, how to perform arithmetic, and finally, how to use fundamental logical operations that form the bedrock of all computation.

### Conversions: Moving Between Bases

Being able to seamlessly convert numbers between their decimal (base-10) and binary (base-2) forms is a critical skill.

#### Binary to Decimal Conversion

The method for converting a binary number to decimal depends on its encoding. The first step is always to look at the most significant bit (MSB).

**Case 1: The number is positive (MSB = 0)** If the MSB is 0, the number is positive. For **Unsigned, Sign & Magnitude, One's Complement, and Two's Complement**, the method is the same: simply sum the weighted powers of 2 for each bit position that has a 1.

- **Example:** Convert the 8-bit number 01011001 to decimal.

$$\text{Value} = (1 \times 2^6) + (0 \times 2^5) + (1 \times 2^4) + (1 \times 2^3) + (0 \times 2^2) + (0 \times 2^1) + (1 \times 2^0)$$

$$\text{Value} = 64 + 16 + 8 + 1 = 89_{10}.$$

**Case 2: The number is negative (MSB = 1)** If the MSB is 1, the method depends on the encoding. Let's convert the 4-bit number 1101 in each system.

- **Sign & Magnitude:** The MSB (1) is the sign. The remaining bits (101) are the magnitude. Magnitude =  $(1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) = 5$ . Final value =  $-5_{10}$ .

- **One's Complement:** To find the magnitude, flip all the bits back to their positive form. Original: 1101 → Flipped: 0010. Magnitude =  $(1 \times 2^1) = 2$ . Final value =  $-2_{10}$ .

- **Two's Complement:** To find the magnitude, flip all the bits and add 1. Original: 1101 → Flip: 0010 → Add 1: 0011. Magnitude =  $(1 \times 2^1) + (1 \times 2^0) = 3$ . Final value =  $-3_{10}$ .

#### Decimal to Binary Conversion

To convert from decimal to binary, we first handle the sign.

**Case 1: The number is positive (or unsigned)** We use the method of **repeated division by 2**. We divide the decimal number by 2, record the remainder, and continue dividing the quotient until it becomes 0. The binary number is the sequence of remainders read from bottom to top.

- **Example:** Convert  $44_{10}$  to an 8-bit unsigned binary number.

$44 \div 2 = 22$  remainder **0** (LSB);  $22 \div 2 = 11$  remainder **0**;  $11 \div 2 = 5$  remainder **1**;  $5 \div 2 = 2$  remainder **1**;  $2 \div 2 = 1$  remainder **0**;  $1 \div 2 = 0$  remainder **1** (MSB). Reading the remainders up: 101100. As an 8-bit number, we pad with leading zeros: 00101100.

**Case 2: The number is negative** First, convert the **absolute value** to binary, then apply the rule for the target encoding.

- **Example:** Convert  $-25_{10}$  to an 8-bit binary number.

1. **First, convert the absolute value, 25, to binary:** 00011001.

2. **Now, apply the encoding rules:**

- **Sign & Magnitude:** Set the MSB to 1. Result: 10011001.

- **One's Complement:** Flip all the bits of the positive version. Result: 11100110.

- **Two's Complement:** Flip the bits and add 1. Flip 00011001  $\rightarrow$  11100110. Add 1  $\rightarrow$  11100111.

### Binary Addition in Two's Complement or Unsigned

Addition in binary works exactly like in decimal: you add digits column by column from right to left and carry over when a column's sum is too large. We focus on two's complement and unsigned because its design makes arithmetic simple. As there is only a given number of bits, a carry out from the MSB is not included in the result.

### Overflow: When the Result Doesn't Fit

Sometimes, the result of an addition is too large to be represented by the given number of bits. This is called **overflow**. For Unsigned, overflow is indicated by a carry out from the MSB (yes, the one not included in the result). Two's complement overflow is more complicated:

- Adding two **positive** numbers results in a **negative** number.

- Adding two **negative** numbers results in a **positive** number.

- Adding two numbers with **different signs** can **NEVER** cause an overflow.

The hardware detects this with a clever trick involving the two most significant carries: the carry **into** the MSB column ( $C_{in}$ ) and the carry **out** of the MSB column ( $C_{out}$ ).

### Two's Complement Overflow Detection

Overflow occurs if and only if  $C_{in} \neq C_{out}$ . This is equivalent to checking if  $C_{in} \text{ XOR } C_{out} = 1$ .

**Why the XOR Trick Works:** Let's analyze the MSB column. The resulting sign bit is  $S_{out} = A_{msb} + B_{msb} + C_{in}$ .

- **Positive + Positive Overflow:** Here,  $A_{msb} = 0$  and  $B_{msb} = 0$ . For the result to be negative ( $S_{out} = 1$ ), a carry-in must have occurred:  $0+0+C_{in} = 1 \implies C_{in} = 1$ . This sum (1) does not produce a carry-out, so  $C_{out} = 0$ . Thus,  $C_{in} = 1$  and  $C_{out} = 0$ . They are different.

- **Negative + Negative Overflow:** Here,  $A_{msb} = 1$  and  $B_{msb} = 1$ . For the result to be positive ( $S_{out} = 0$ ), the sum must be  $1+1+C_{in} = 10_2$  or  $1+1+C_{in} = 11_2$ . To get  $S_{out} = 0$ , we must have  $1+1+C_{in} = 10_2$ , which means  $C_{in} = 0$ . This sum produces a carry-out, so  $C_{out} = 1$ . Thus,  $C_{in} = 0$  and  $C_{out} = 1$ . They are different.

In all non-overflow cases,  $C_{in}$  and  $C_{out}$  will be the same. This simple check is easy to implement in hardware.

## Bitwise Logical Operations

Beyond arithmetic, computers rely heavily on bitwise logical operations. Unlike an operation like addition which treats an 8-bit string as a single number (e.g., 25), bitwise operations treat it as a collection of 8 individual bits. Each bit in the first operand is matched with the bit in the corresponding position of the second operand, and the operation is performed on these pairs independently. What happens in one bit position has absolutely no effect on any other.

To formally define these operations, we use a **truth table**. A truth table is a straightforward chart that lists every possible combination of inputs for an operation and shows the resulting output for each case. For a two-input operation, there are four possible combinations: 0/0, 0/1, 1/0, and 1/1.

**NOT** The NOT operation is the simplest. It is a *unary* operator, meaning it acts on a single operand.

- **English Definition:** The NOT operation inverts or flips the input bit. If the input is 1, the output is 0. If the input is 0, the output is 1.

- **Example:**

```

NOT 10110001

-----

01001110

```

| A | NOT A |

|---|-------|

| 0 | 1     |

| 1 | 0     |

## AND

- **English Definition:** The AND operation outputs a 1 only if *both* of the input bits are 1. If either bit is a 0, the output is 0. This is useful for “masking” or clearing bits.

- **Example:** Let’s say we want to clear the upper 4 bits of a byte. We can AND it with the mask 00001111.

```

10110101

AND 00001111 (The Mask)

-----

00000101 (Result)

```

| A | B | A AND B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

## OR

- **English Definition:** The OR operation outputs a 1 if *at least one* of the input bits is 1. It only outputs 0 if both inputs are 0. This is useful for setting specific bits.

- **Example:** Let’s say we want to ensure the two most significant bits are set to 1. We can OR the value with the mask 11000000.

|                                             |            |  |  |  |  |  |  |

|---------------------------------------------|------------|--|--|--|--|--|--|

| 10110101                                    |            |  |  |  |  |  |  |

| OR 11000000                                 | (The Mask) |  |  |  |  |  |  |

| <hr style="border-top: 1px dashed black;"/> |            |  |  |  |  |  |  |

| 11110101                                    | (Result)   |  |  |  |  |  |  |

| A | B | A OR B |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

### XOR (Exclusive OR)

- **English Definition:** The XOR operation outputs a 1 only if the two input bits are *different*. If they are the same (both 0 or both 1), the output is 0. This is very useful for toggling or flipping bits.

- **Example:** If we XOR a value with a mask, the bits corresponding to a ‘1’ in the mask will be flipped, and the bits corresponding to a ‘0’ will be unchanged.

|                                             |                                        |  |  |  |  |  |  |

|---------------------------------------------|----------------------------------------|--|--|--|--|--|--|

| 10110101                                    |                                        |  |  |  |  |  |  |

| XOR 11110000                                | (The Mask)                             |  |  |  |  |  |  |

| <hr style="border-top: 1px dashed black;"/> |                                        |  |  |  |  |  |  |

| 01000101                                    | (Result: the first 4 bits are flipped) |  |  |  |  |  |  |

| A | B | A XOR B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

### Universal Gates and De Morgan's Laws

Two other critical logical operations are **NAND** (Not-AND, the result of an AND is negated) and **NOR** (Not-OR, the result of an OR is negated).

These two gates are special because they are **universal gates**. This means that any other logical function (AND, OR, NOT) can be constructed using *only* NAND gates, or *only* NOR gates. This is incredibly useful for manufacturing, as you can design a

| A | B | A NAND B | A NOR B |

|---|---|----------|---------|

| 0 | 0 | 1        | 1       |

| 0 | 1 | 1        | 0       |

| 1 | 0 | 1        | 0       |

| 1 | 1 | 0        | 0       |

complex chip using just one type of simple, repeated building block. The mathematical foundation for this property is provided by **De Morgan's Laws**.

Mathematically, using  $\cdot$  for AND,  $+$  for OR, and an overbar for NOT, the laws are stated as:

$$\overline{A \cdot B} = \bar{A} + \bar{B}$$

$$\overline{A + B} = \bar{A} \cdot \bar{B}$$

At first glance, this may seem abstract, but it's quite intuitive in plain English.

**First Law:**  $\overline{A \cdot B} = \bar{A} + \bar{B}$  In English: “Not (A and B) is the same as (Not A) or (Not B).”

- **Intuition:** Imagine a rule that says, “To get into the party, you must be on the list **AND** have an ID.” Failing this rule — i.e., *NOT* (on list AND have ID) — means one of two things is true: you are *NOT* on the list, **OR** you do *NOT* have an ID. You don't need to fail both conditions to be turned away. Failing just one is enough.

**Second Law:**  $\overline{A + B} = \bar{A} \cdot \bar{B}$  In English: “Not (A or B) is the same as (Not A) and (Not B).”

- **Intuition:** Imagine a different rule that says, “To get a discount, you must be a student **OR** a senior citizen.” Failing this rule — i.e., *NOT* (student OR senior) — means you must fail *both* conditions simultaneously. You must be *NOT* a student **AND** you must be *NOT* a senior citizen.

De Morgan's laws provide the formal method for converting between AND-based and OR-based logic, proving how a universal gate like NAND can be used to create any other logical function, forming the fundamental building blocks of digital circuits.

## Cheatsheet: Key Takeaways on Operations

- **Decimal to Binary:** For positive numbers, use repeated division by 2. For negative numbers, convert the absolute value first, then apply the rules for Sign & Mag, 1's Comp, or 2's Comp.

- **Binary to Decimal (Two's Comp):** If the MSB is 1, the number is negative. To find its value, flip all the bits, add 1, convert the result to decimal, and put a minus sign in front.

- **Overflow:** Occurs when the result of an addition is too large to fit. This happens only when adding numbers of the same sign and the result has a different sign for Two's Complement.

- **Overflow Detection (Hardware):** An overflow has occurred if and only if the carry-in to the MSB is different from the carry-out of the MSB ( $C_{in} \neq C_{out}$ ) for Two's Complement.

- **Bitwise Operations:**

- **AND** is often used to *clear* or *mask* bits (e.g., `xxxx & 1100 = xx00`).

- **OR** is often used to *set* bits (e.g., `xxxx | 0011 = xx11`).

- **XOR** is often used to *flip* or *toggle* bits (e.g., `xxxx ^ 0011` flips the last two bits).

- **Universal Gates:** NAND and NOR are universal because all other logic gates (AND, OR, NOT) can be constructed from them.

## Representing Fractional Numbers

So far, we have only dealt with integers. But the real world is full of fractional numbers, like the price of a coffee (\$3.75) or a mathematical constant like  $\pi$  (3.14159...). To represent these, we need to move beyond integer schemes and find a way to place a “point” within our binary numbers.

### Fixed-Point Representation

The most straightforward way to represent fractional numbers is the **fixed-point** method. The idea is simple: we decide that the binary point is located at a fixed, predetermined position within our bit string. This divides the bits into an integer part (to the left of the point) and a fractional part (to the right of the point).

Just as the weights to the left of the point are positive powers of two ( $2^0, 2^1, 2^2, \dots$ ), the weights to the right of the point are negative powers of two:  $2^{-1}(0.5)$ ,  $2^{-2}(0.25)$ ,  $2^{-3}(0.125)$ , and so on.

### Conversions with Fixed-Point Numbers

**Binary Fixed-Point to Decimal** To convert a fixed-point binary number to decimal, simply sum the weighted values of each part.

- **Example:** Convert the 8-bit fixed-point number 0110.1101 to decimal, assuming 4 bits for the integer and 4 for the fraction.

- **Integer Part:**  $0110 = (0 \times 2^3) + (1 \times 2^2) + (1 \times 2^1) + (0 \times 2^0) = 4 + 2 = 6$ .

- **Fractional Part:**  $.1101 = (1 \times 2^{-1}) + (1 \times 2^{-2}) + (0 \times 2^{-3}) + (1 \times 2^{-4}) = 0.5 + 0.25 + 0.0625 = 0.8125$ .

- **Total Value:**  $6 + 0.8125 = 6.8125$ .

**Decimal to Binary Fixed-Point** This is a two-step process: convert the integer part and the fractional part separately.

1. **Integer Part:** Convert using the familiar repeated division by 2.

2. **Fractional Part:** Convert using **repeated multiplication by 2**. Multiply the fraction by 2; the integer part of the result is the next binary digit. Repeat the process with the new fractional part until the fraction becomes 0 or you run out of bits.

- **Example:** Convert 10.625 to an 8-bit fixed-point representation with 4 integer and 4 fractional bits.

- **Integer Part:**  $10_{10} = 1010_2$ .

- **Fractional Part (0.625):**  $0.625 \times 2 = 1.25$ ;  $0.25 \times 2 = 0.5$ ;  $0.5 \times 2 = 1.0$ . The fractional part is  $.101$ .

- **Combine and Pad:** We combine the parts  $(1010.101)$  and pad the fractional part to 4 bits, giving us  $1010.1010$ .

### Negative Numbers and Arithmetic in Fixed-Point

Representing negative numbers in fixed-point is handled using the standard **two's complement** method, applied to the entire bit string as if the binary point wasn't there.

- **Example:** Find the representation of -2.5 using an 8-bit format (4 integer, 4 fractional bits).

1. Start with positive 2.5:  $2 = 10_2$ ,  $0.5 = .1_2$ . So, 2.5 is  $0010.1000$ .

2. Flip all the bits:  $1101.0111$ .

3. Add 1 to the least significant bit (LSB):  $1101.0111 + 0000.0001 = 1101.1000$ .

Thus,  $1101.1000$  represents -2.5.

A major advantage of this scheme is that arithmetic is incredibly simple. To add or subtract fixed-point numbers, you just line up the binary points and perform standard binary addition/subtraction on the entire string. The hardware is identical to what is used for integers, making fixed-point operations very fast and efficient.

### Pros and Cons of Fixed-Point

- **Pros:** Fixed-point representation is simple and fast. Arithmetic can be performed using the exact same hardware logic as for integers.

- **Cons:** The biggest drawback is its **limited dynamic range**. You cannot represent very large numbers and very small fractions simultaneously. The designer must make a permanent trade-off between **range** (number of integer bits) and **precision** (number of fractional bits). This system is inadequate for scientific applications that deal with both the astronomically large and the microscopically small.

### Floating-Point Representation

How can we represent both the mass of the sun ( $1.989 \times 10^{30}$  kg) and the mass of an electron ( $9.109 \times 10^{-31}$  kg) in the same number system? The solution is to adopt a format similar to scientific notation, where the decimal point can “float” to wherever it’s needed. This is the idea behind **floating-point representation**.

To ensure that floating-point numbers are handled consistently across all machines, the industry has adopted the **IEEE 754 standard**. We will focus on the most common 32-bit version, known as **single-precision** or **FP32**.

### The IEEE 754 FP32 Standard

An FP32 number is made of three components packed into a 32-bit string:

1. **Sign (S):** 1 bit. ‘0’ for positive, ‘1’ for negative.

2. **Exponent (E):** 8 bits. This determines the magnitude (how large or small the number is).

3. **Fraction (F)** (also called Mantissa or Significand): 23 bits. This determines the number’s actual digits (its precision).

These components are used in the following formula:

$$\text{Value} = (-1)^S \times (1.F) \times 2^{(E-\text{bias})}$$

Let’s break down the two tricky parts:

- **The Hidden Bit (1.F):** In binary scientific notation, a normalized number always starts with a ‘1’ (e.g.,  $1.011 \times 2^5$ ). Since this leading ‘1’ is always there, we don’t need to waste a bit storing it! This “hidden bit” gives us 24 bits of precision while only storing 23.

- **Biased Exponent (E - bias):** The 8-bit exponent field (E) can store values from 0 to 255. To represent both positive and negative exponents, the standard uses a **biased notation**. We subtract a fixed **bias** of **127** from the stored value E.

### Zero and Special Cases

As the hidden bit is always a one, the formula cannot represent zero! Zero uses a different formula and thus a special case. If  $E = 0$ , then the following formula is used:

$$\text{Value} = (-1)^S \times (0.F) \times 2^{(E-126)}$$

No more hidden bit means zero is possible; zero is represented by 32 zeros. There are other special cases, for example when  $E = 255$  (all ones), but this text does not cover them. For further reading, look at the IEEE 754 specification.

### Floating-Point Examples

Let’s walk through converting decimal numbers to FP32 format.

#### Example 1: 1.5

1. **Sign:** Positive  $\implies S = 0$ .

2. **Binary:**  $1.5_{10} = 1.1_2$ .

3. **Normalize:** The number is already in the form  $1.F$ . This is  $1.1 \times 2^0$ .

4. **Find Components:** The fraction **F** is ‘1’, padded to 23 bits. The exponent is ‘0’, so we solve  $E - 127 = 0 \implies E = 127 = 01111111_2$ .

5. **Assemble:**  $0 \mid 01111111 \mid 10000000000000000000000000000000$

#### Example 2: 764.0

1. **Sign:** Positive  $\implies S = 0$ .

2. **Binary:**  $764_{10} = 101111100_2$ .

3. **Normalize:** Move the point 9 places left:  $1.01111100 \times 2^9$ .

4. **Find Components:** **F** is ‘01111100’, padded. The exponent is ‘9’, so  $E - 127 = 9 \implies E = 136 = 10001000_2$ .

5. **Assemble:**  $0 \mid 10001000 \mid 01111100000000000000000000000000$

### Example 3: 18.547 (The Precision Problem)

1. **Sign:** Positive  $\implies S = 0$ .

2. **Binary:** The integer part is  $18 = 10010_2$ . The fractional part  $0.547$  is non-terminating in binary ( $0.10001\dots_2$ ).

3. **Normalize:**  $1.001010001\dots \times 2^4$ .

4. **Find Components:** The exponent is ‘4’, so  $E = 131 = 10000011_2$ . The fraction  $F$  is ‘ $001010001\dots$ ’. Since we only have 23 bits, we must truncate or round the infinite series. This is where **precision loss** occurs. The number stored is not exactly  $18.547$ , but a very close approximation.

### Other Floating-Point Formats

While we focus on FP32, you should be aware of other common formats.

Table 2.3: Common IEEE 754 Floating-Point Formats

| Name          | Total Bits | Sign | Exponent | Fraction | Bias    |

|---------------|------------|------|----------|----------|---------|

| FP32 (Single) | 32         | 1    | 8        | 23       | 127     |

| FP64 (Double) | 64         | 1    | 11       | 52       | 1023    |

| FP16 (Half)   | 16         | 1    | 5        | 10       | 15      |

| FP8 (Quarter) | 8          | 1    | 4 or 5   | 3 or 2   | 7 or 15 |

### Cheatsheet: Key Takeaways on Fractional Numbers

- **Fixed-Point:** Simple and fast because arithmetic is just integer arithmetic. Negative numbers use two’s complement. Its main con is a **limited dynamic range**.

- **Floating-Point:** Uses a form of scientific notation to represent a huge dynamic range. It is the standard for almost all non-integer calculations.

- **FP32 Formula:** Value  $= (-1)^S \times (1.F) \times 2^{(E-127)}$

- **FP32 Components:** It is composed of **1 Sign bit**, **8 Exponent bits**, and **23 Fraction bits**.

- **Key Concepts:** Remember the **hidden bit** (the implicit ‘1.’ before the fraction) and the **exponent bias** (127 for FP32).

- **Precision Loss:** Because the fraction part has a fixed number of bits, not all decimal numbers can be represented perfectly. This can lead to small rounding errors in calculations.

## Representing Text and Data

We've dedicated this chapter to representing different kinds of numbers, but what about text? When you type an essay or send a message, the computer isn't storing the shapes of the letters 'A', 'b', and 'c'. It is, of course, storing them as bits. The final piece of our puzzle is understanding the standard codes used to map characters to numbers.

### The ASCII Standard

The most foundational standard for representing text is **ASCII** (American Standard Code for Information Interchange). Developed in the 1960s, ASCII is a 7-bit encoding scheme, meaning it uses 7 bits to define  $2^7 = 128$  unique codes. Each code is mapped to a specific character.

- The character 'A' is assigned the decimal value 65 ( $01000001_2$ ).

- The character 'B' is assigned the decimal value 66 ( $01000010_2$ ).

- The character 'a' is assigned the decimal value 97 ( $01100001_2$ ).

- The digit '0' is assigned the decimal value 48 ( $00110000_2$ ).

Since computers typically operate on 8-bit bytes, the 8th bit was often set to '0' or used for special purposes.

The first 32 codes (0-31) and the last code (127) are non-printable **control characters**, which were originally used to control teletype machines. Many are still in use today, such as **Newline** (code 10), **Backspace** (code 8), and **Tab** (code 9). The remaining codes (32-126) represent printable characters, including the space character (code 32).

### A Brief Note on Unicode

ASCII's 128 characters are sufficient for English but fail to represent characters from other languages, let alone symbols and emojis. The modern solution is **Unicode**, a universal standard that defines over 149,000 characters. Common Unicode encodings like **UTF-8** and **UTF-16** can represent every character from every language. Importantly, the first 128 codes of Unicode are identical to the ASCII standard, making ASCII a direct subset of Unicode.

### Full ASCII Table (Codes 0-127)

#### A Human-Friendly Shorthand: Hexadecimal Notation

You will often see long binary numbers, especially memory addresses, written in a strange format like `0x7FFFAB42`. This is **hexadecimal** notation (often called "hex"), and it's important to understand what it is and why we use it.

**Hexadecimal is not a data representation used by the computer.** The computer's hardware only understands binary. Hexadecimal is a **human-friendly shorthand for binary**.

Table 2.4: ASCII Printable and Control Characters

| Dec | Char | Dec | Char | Dec | Char | Dec | Char |

|-----|------|-----|------|-----|------|-----|------|

| 0   | NUL  | 32  | SPC  | 64  | @    | 96  | ,    |

| 1   | SOH  | 33  | !    | 65  | A    | 97  | a    |

| 2   | STX  | 34  | "    | 66  | B    | 98  | b    |

| 3   | ETX  | 35  | #    | 67  | C    | 99  | c    |

| 4   | EOT  | 36  | \$   | 68  | D    | 100 | d    |

| 5   | ENQ  | 37  | %    | 69  | E    | 101 | e    |

| 6   | ACK  | 38  | &    | 70  | F    | 102 | f    |

| 7   | BEL  | 39  | ,    | 71  | G    | 103 | g    |

| 8   | BS   | 40  | (    | 72  | H    | 104 | h    |

| 9   | TAB  | 41  | )    | 73  | I    | 105 | i    |

| 10  | LF   | 42  | *    | 74  | J    | 106 | j    |

| 11  | VT   | 43  | +    | 75  | K    | 107 | k    |

| 12  | FF   | 44  | ,    | 76  | L    | 108 | l    |

| 13  | CR   | 45  | -    | 77  | M    | 109 | m    |

| 14  | SO   | 46  | .    | 78  | N    | 110 | n    |

| 15  | SI   | 47  | /    | 79  | O    | 111 | o    |

| 16  | DLE  | 48  | 0    | 80  | P    | 112 | p    |

| 17  | DC1  | 49  | 1    | 81  | Q    | 113 | q    |

| 18  | DC2  | 50  | 2    | 82  | R    | 114 | r    |

| 19  | DC3  | 51  | 3    | 83  | S    | 115 | s    |

| 20  | DC4  | 52  | 4    | 84  | T    | 116 | t    |

| 21  | NAK  | 53  | 5    | 85  | U    | 117 | u    |

| 22  | SYN  | 54  | 6    | 86  | V    | 118 | v    |

| 23  | ETB  | 55  | 7    | 87  | W    | 119 | w    |

| 24  | CAN  | 56  | 8    | 88  | X    | 120 | x    |

| 25  | EM   | 57  | 9    | 89  | Y    | 121 | y    |

| 26  | SUB  | 58  | :    | 90  | Z    | 122 | z    |

| 27  | ESC  | 59  | ;    | 91  | [    | 123 | {    |

| 28  | FS   | 60  | <    | 92  | \    | 124 | -    |

| 29  | GS   | 61  | =    | 93  | ]    | 125 | }    |

| 30  | RS   | 62  | >    | 94  | ^    | 126 | ~    |

| 31  | US   | 63  | ?    | 95  | _    | 127 | DEL  |

Hexadecimal is a base-16 number system. It uses the digits 0-9 and then the letters A-F to represent the values 10-15. The magic of hexadecimal is that  $16 = 2^4$ . This means that **every one hexadecimal digit corresponds perfectly to exactly four binary digits** (a nibble). This relationship allows for quick and easy conversion.

Table 2.5: Decimal, Hexadecimal, and Binary Equivalents

| Decimal | Hex | Binary | Decimal | Hex | Binary |

|---------|-----|--------|---------|-----|--------|

| 0       | 0   | 0000   | 8       | 8   | 1000   |

| 1       | 1   | 0001   | 9       | 9   | 1001   |

| 2       | 2   | 0010   | 10      | A   | 1010   |

| 3       | 3   | 0011   | 11      | B   | 1011   |

| 4       | 4   | 0100   | 12      | C   | 1100   |

| 5       | 5   | 0101   | 13      | D   | 1101   |

| 6       | 6   | 0110   | 14      | E   | 1110   |

| 7       | 7   | 0111   | 15      | F   | 1111   |

**Example 1: Binary to Hex** To convert a binary string to hex, group the bits in sets of four from right to left and replace each group with its hex equivalent.

- Binary: 1101 0101 1111 0010

- Grouped: 1101 0101 1111 0010

- Hex: D 5 F 2

It is much easier for a person to read and remember D5F2 than 1101010111110010.

**Example 2: Hex to Binary** To convert hex to binary, simply replace each hex digit with its 4-bit binary string. The prefix 0x is commonly used in programming languages to indicate that a number is in hexadecimal format.

- Hex: 0x1A7

- Expand: 1 A 7

- Binary: 0001 1010 0111

Hexadecimal is an essential tool for programmers because it provides a compact and less error-prone way to work with the raw binary data that computers actually use.

## Cheatsheet: Key Takeaways on Text and Data Notation

- **ASCII:** A 7-bit standard that maps characters (letters, symbols, numbers) to integer values. The first 128 characters are a subset of Unicode.

- **Unicode:** The modern, universal standard for representing text from all languages.

- **Hexadecimal (Base-16):** A **human-friendly shorthand** for representing binary data. It is not used by the computer's internal hardware.

- **The Golden Rule of Hex:** 1 hexadecimal digit always represents exactly 4 binary digits.

- **Common Notation:** The prefix 0x is used in code to signify that a number is hexadecimal.

# 3 Digital Logic

## Chapter 3: Digital Logic Structures

In the last chapter, we established that all information in a computer is represented by bits. But how does a machine physically store these bits and, more importantly, how does it compute with them? The answer lies in the hardware that underpins all of computing: digital logic structures. This chapter will take you on a journey from the simplest physical switch to the complex circuits that perform calculations.

### The Switch: Storing a Bit

At the most fundamental level, a computer is a collection of billions of tiny switches. Think of a simple light switch on your wall. It can be in one of two states: ON or OFF. There is no in-between. We can use this physical property as a direct analog for a bit:

- **OFF** represents a logical **0**.

- **ON** represents a logical **1**.

This is our first and most important abstraction: a physical state (the position of a switch) represents a logical value (a bit). Using this abstraction, it's clear we can *store* information. A bank of eight switches could be set in  $2^8 = 256$  different patterns, allowing it to store any 8-bit number.

But we want to do more than just store bits; we want to compute with them. To do that, we need a switch that can be controlled not by a human hand, but by an electrical signal. A switch that can be turned ON or OFF by another switch. This is the key that unlocks computation, and the device that makes it possible is the transistor.

#### Cheatsheet: The Switch Abstraction

- A physical switch has two states: ON and OFF.

- This provides a physical implementation for the two logical states of a bit: 1 and 0.

- The core idea of computation is to have switches that are controlled by other electrical signals (i.e., other switches), not by mechanical force.

## The Transistor: An Electrically Controlled Switch

The transistor is arguably the most important invention of the 20th century. It is the fundamental building block of all modern electronics. The first working point-contact transistor was demonstrated in 1947 by John Bardeen and Walter Brattain at Bell Labs, under the guidance of William Shockley. For this work, the three shared the 1956 Nobel Prize in Physics. (As a point of pride for our university, John Bardeen was an esteemed alumnus, earning both his bachelor's and master's degrees right here at the University of Wisconsin-Madison).

That first transistor was a bulky, discrete component. Technology has since evolved to the **MOSFET** (Metal-Oxide-Semiconductor Field-Effect Transistor), and specifically **CMOS** (Complementary MOS) technology, which is the workhorse of digital logic today. Modern processors now use incredible technologies like **FinFETs**, which are essentially 3D transistors, allowing engineers to pack billions of them onto a single chip.

### The Physics of a MOSFET

A MOSFET has three terminals: a **Source**, a **Drain**, and a **Gate**. The basic idea is that the Gate controls the flow of current between the Source and Drain. This is achieved by manipulating a semiconductor substrate (usually silicon).

Let's consider an **n-type MOSFET (nMOS)**. It's built on a p-type silicon substrate (meaning it has an excess of positive charge carriers, or "holes"). Within this substrate, two n-type regions (with an excess of negative charge carriers, or electrons) are created for the source and drain. Normally, no current can flow between them. However, the gate is separated from the substrate by a thin insulating layer of oxide. When a positive voltage (a logical 1) is applied to the gate, it creates a downward-pointing electric field. This field pushes the positive holes away from the area under the gate and attracts the minority-carrier electrons. A sufficient concentration of these electrons forms a conductive n-type "channel" between the source and drain, allowing current to flow. The switch is ON.

A **p-type MOSFET (pMOS)** is the complementary opposite. It's built on an n-type substrate with p-type source and drain regions. When a low or zero voltage (a logical 0) is applied to its gate, the resulting electric field attracts positive holes, forming a conductive p-type channel. This allows current to flow. A high voltage at the gate would disrupt this channel and turn the switch OFF.

### Circuit Rules and the Inverter

This complementary behavior is the key to CMOS design. We establish two main voltage levels: **VDD**, the power supply voltage representing logical 1, and **GND** (Ground), representing logical 0.

- **P-type transistors** are used to create a "pull-up" network that connects the output to **VDD (1)**. They are active when their gate is 0.

- **N-type transistors** are used to create a "pull-down" network that connects the output to **GND (0)**. They are active when their gate is 1.

A fundamental rule of CMOS design is that for any given input, the circuit must have a path to *either* VDD or GND, but **never both at the same time** (which would cause a short circuit) and never neither (which would leave the output floating).

Let's re-examine our first logic gate, the inverter, with this new terminology.

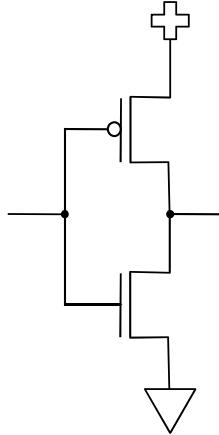

Figure 3.1: CMOS Inverter with VDD and GND

When Input = 1, the pull-down network (n-type) turns ON, connecting the Output to GND (0). The pull-up network (p-type) is OFF. When Input = 0, the pull-up network (p-type) turns ON, connecting the Output to VDD (1). The pull-down network is OFF. The output is always actively driven to a valid state.

#### Cheatsheet: The Transistor

- A transistor is an electrically controlled switch. The **Gate** controls the flow of current between the **Source** and **Drain**.

- **nMOS Transistor:** Gate = 1 → ON. Forms the **pull-down network** to connect the output to **GND (0)**.

- **pMOS Transistor:** Gate = 0 → ON. Forms the **pull-up network** to connect the output to **VDD (1)**.

- **CMOS Rule:** The pull-up and pull-down networks are complementary; only one is active at a time.

#### Building More Complex Gates

An inverter is useful, but to build a computer, we need more complex logic. By arranging transistors in clever ways, we can construct any logic gate we need. Let's look at the transistor-level implementation of the two universal gates: NAND and NOR.

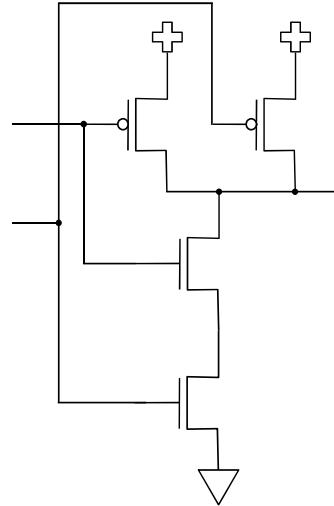

**NAND Gate (NOT-AND)** A 2-input NAND gate is constructed with two p-type transistors in parallel and two n-type transistors in series.

Figure 3.2: A 2-input NAND gate transistor diagram

The output will be connected to Ground (0) only if **both** n-type transistors turn on, which requires A AND B to both be 1. In all other cases, at least one of the p-type transistors will be on, connecting the output to Power (1).

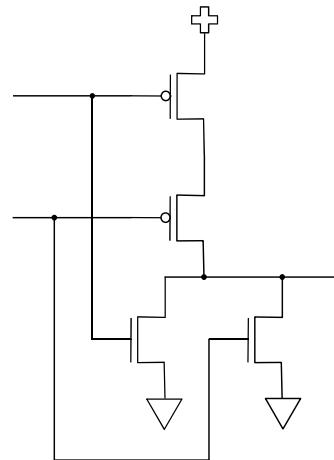

**NOR Gate (NOT-OR)** A 2-input NOR gate is constructed with two p-type transistors in series and two n-type transistors in parallel.

Figure 3.3: A 2-input NOR gate transistor diagram

The output will be connected to Ground (0) if **either** of the n-type transistors turns on, which requires A OR B to be 1. Only when both A and B are 0 will the p-type series be on, connecting the output to Power (1).

From these universal gates, we can create others. An AND gate is simply a NAND gate followed by an inverter. An OR gate is a NOR gate followed by an inverter.

**The Abstraction of Gate Symbols** Working at the transistor level is tedious. Just as we abstracted a physical switch to a logical bit, we can abstract these transistor configurations into clean, simple **logic gate symbols**. This allows us to design complex circuits without thinking about individual transistors.

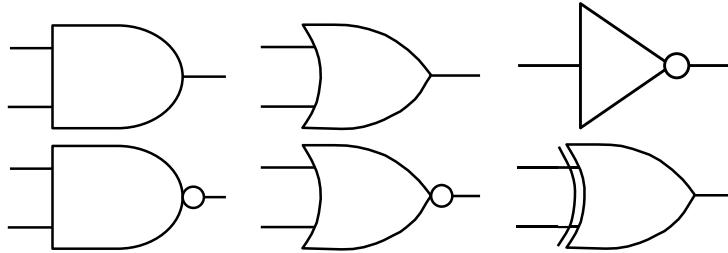

Figure 3.4: The standard logic gate symbols for AND, OR, NOT, NAND, NOR, and XOR respectively.

We have now seen two levels of our system: the physical implementation using transistors, and the logical abstraction of a gate. This is a powerful example of the "Big Idea" of abstraction from Chapter 1.

#### Cheatsheet: Logic Gates

- Complex gates like NAND and NOR are built from specific series and parallel combinations of n-type and p-type transistors.

- **NAND** and **NOR** are “universal gates” because any other logic function can be created from them.

- We use **logic gate symbols** as an abstraction to hide the underlying transistor-level complexity, allowing us to design more complex systems.

### Combinational Circuits: Datapath Components

Now that we have a toolbox of logic gates, we can start building functional circuits. The first type we'll examine is **combinational logic**. In a combinational circuit, the output is determined *only* by the current values of the inputs. These circuits have no memory of what happened before. Many essential "datapath" components of a processor are built from combinational logic.

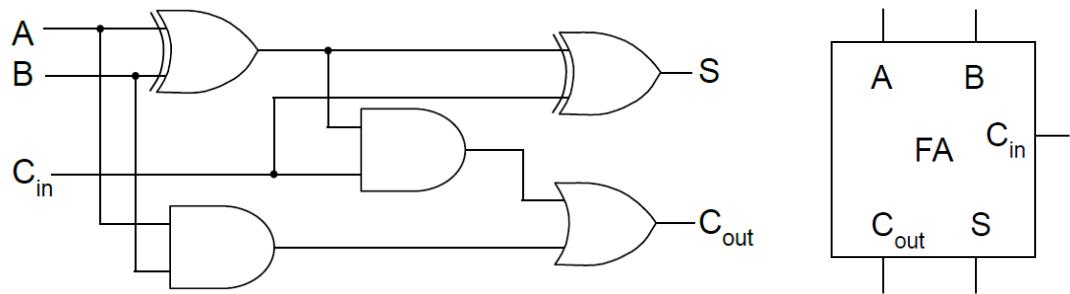

**Full Adder (FA)** A full adder is a circuit that adds three bits together: A, B, and a Carry-In ( $C_{in}$ ), producing a Sum (S) bit and a Carry-Out ( $C_{out}$ ) bit.

| Inputs |   |                 | Outputs          |   |

|--------|---|-----------------|------------------|---|

| A      | B | C <sub>in</sub> | C <sub>out</sub> | S |

| 0      | 0 | 0               | 0                | 0 |

| 0      | 0 | 1               | 0                | 1 |

| 0      | 1 | 0               | 0                | 1 |

| 0      | 1 | 1               | 1                | 0 |

| 1      | 0 | 0               | 0                | 1 |

| 1      | 0 | 1               | 1                | 0 |

| 1      | 1 | 0               | 1                | 0 |

| 1      | 1 | 1               | 1                | 1 |

Figure 3.5: Image of Full Adder gate-level implementation and FA block diagram

Once we have a full adder, we abstract it into a block. We can then chain these blocks together to create a multi-bit adder. A 4-bit adder is made by connecting four FA blocks, where the C<sub>out</sub> of one block becomes the C<sub>in</sub> of the next. This is called a ripple-carry adder.

Figure 3.6: Image of a 4-bit ripple-carry adder using FA blocks

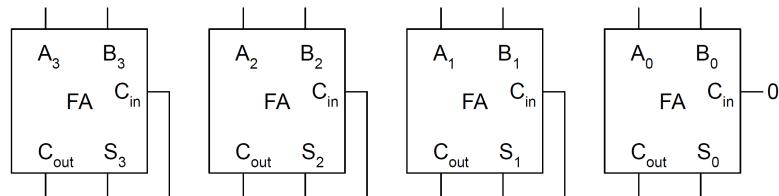

**Decoder** A decoder takes an n-bit input and asserts exactly one of its 2<sup>n</sup> output lines. For example, a 2-to-4 decoder takes a 2-bit input and selects one of four outputs.

| Inputs |       | Outputs |       |       |       |

|--------|-------|---------|-------|-------|-------|

| $I_1$  | $I_0$ | $D_3$   | $D_2$ | $D_1$ | $D_0$ |

| 0      | 0     | 0       | 0     | 0     | 1     |

| 0      | 1     | 0       | 0     | 1     | 0     |

| 1      | 0     | 0       | 1     | 0     | 0     |

| 1      | 1     | 1       | 0     | 0     | 0     |

Figure 3.7: Image of a 2-to-4 decoder implementation

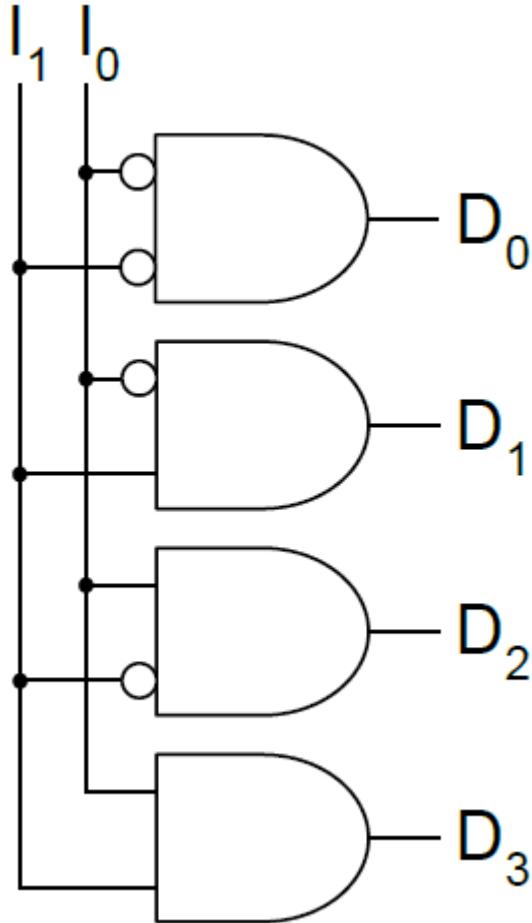

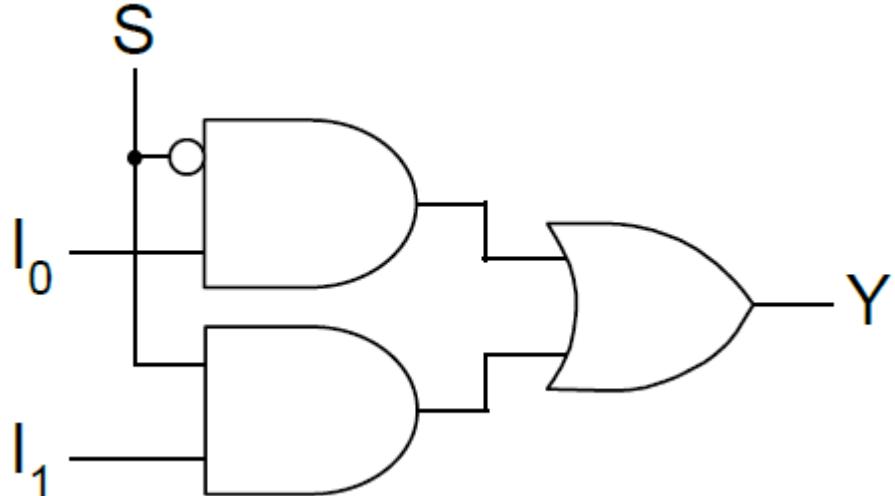

**Multiplexer (Mux)** A multiplexer (or “mux”) is a data selector. It has several data inputs, a set of select lines, and a single output. The select lines determine which one of the data inputs is passed to the output. The simplest is a 2-to-1 mux, which selects between two inputs,  $I_0$  and  $I_1$ , using a single select line,  $S$ .

| S | Output Y                   |

|---|----------------------------|

| 0 | I <sub>0</sub> is selected |

| 1 | I <sub>1</sub> is selected |

Image of 2-to-1 Mux implementation

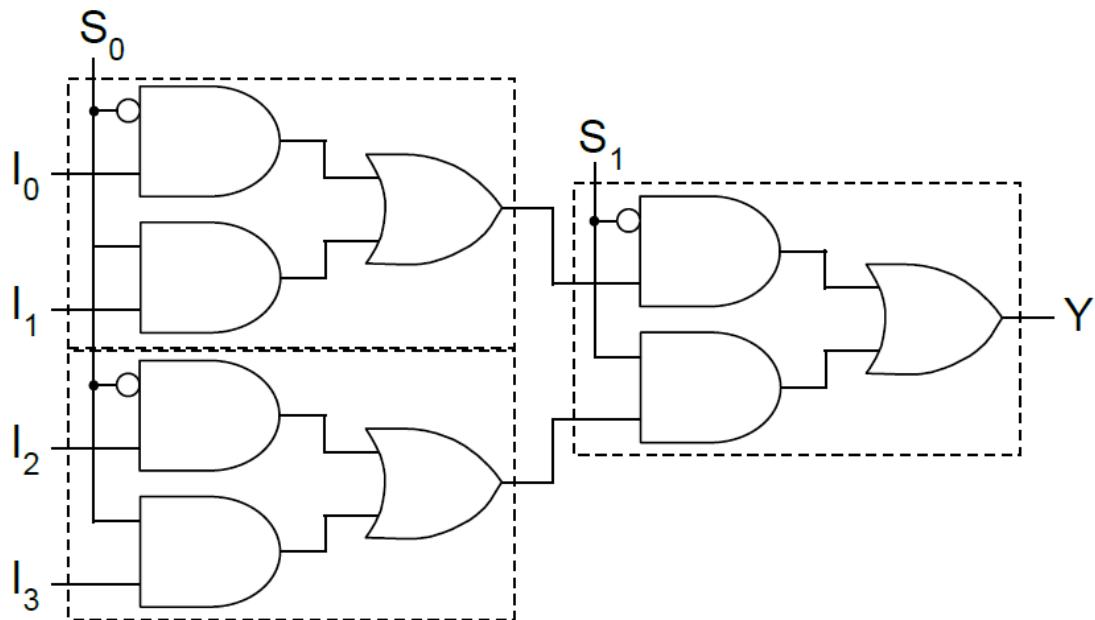

Like adders, muxes are modular. But how do we build larger muxes from smaller ones? Let's consider building a **4-to-1 mux**. This requires selecting one of four inputs (I<sub>0</sub>, I<sub>1</sub>, I<sub>2</sub>, I<sub>3</sub>), which means we will need two select lines (S<sub>1</sub>, S<sub>0</sub>), since  $2^2 = 4$ .

We can approach this hierarchically. Let the first select bit, S<sub>1</sub>, make a high-level choice: does it select from the first pair of inputs (I<sub>0</sub>, I<sub>1</sub>) or the second pair (I<sub>2</sub>, I<sub>3</sub>)? We can use two 2-to-1 muxes for this first "stage". The second select bit, S<sub>0</sub>, can then be used to pick the final winner from the outputs of that first stage. This requires a third 2-to-1 mux.

Image showing a 4-to-1 Mux built from three 2-to-1 Muxes

This pattern can be extended. To build an **8-to-1 mux**, which requires 3 select lines, we can combine two 4-to-1 muxes and one 2-to-1 mux. The two 4-to-1 muxes handle the eight inputs, and the 2-to-1 mux, controlled by the most significant select bit, chooses which of the 4-to-1 muxes' outputs gets passed to the final output. This hierarchical design is a core principle of digital engineering.

#### Cheatsheet: Combinational Circuits

- **Combinational Logic:** The output depends only on the current inputs. There is no memory.

- **Full Adder (FA):** Adds 3 bits ( $A, B, C_{in}$ ) and produces a Sum and a  $C_{out}$ . Multi-bit adders are built by chaining FAs.

- **Decoder:** Takes  $n$  inputs and activates one of  $2^n$  outputs. Used for selecting memory locations or instructions.

- **Multiplexer (Mux):** Uses select lines to route one of several data inputs to a single output. It's like a digital switch.

- **Hierarchical Design:** Complex components (like a 4-bit adder or an 8-to-1 mux) are built by combining simpler, repeated blocks.

## Sequential Circuits: Adding Memory

Until now, we have only discussed combinational circuits, where the output is purely a function of the current inputs. An AND gate's output doesn't depend on what its inputs were a moment ago. But to build a computer, we need circuits that can *remember* past values. We need memory.

This brings us to **sequential circuits**. In a sequential circuit, the output depends not only on the current inputs but also on the circuit's previous state. This ability to store a state is the fundamental property that enables everything from registers to RAM. The most basic element of memory is the latch.

### The S-R Latch: The Simplest Memory Cell

The simplest way to create a memory element is to use feedback, where the output of a gate is fed back into its input. The S-R Latch (Set-Reset Latch) is built from two cross-coupled NOR gates. It has two inputs, S (Set) and R (Reset), and two outputs, Q and its complement, Q'.

Image of an S-R Latch circuit using two NOR gates

Let's walk through its behavior:

- **Hold State (S=0, R=0):** This is the memory state. If Q is currently 1, the top NOR gate receives (0,0) from R and Q', outputting 1. If Q is 0, the top NOR gate receives (1,0) from R and Q', outputting 0. The feedback loop holds the current value of Q indefinitely.

- **Set State (S=1, R=0):** When S goes to 1, it forces the output of the bottom NOR gate (Q') to become 0. This 0 is fed to the top NOR gate along with R=0. The inputs (0,0) to the top NOR gate force its output (Q) to become 1. The latch is now "set" to 1.

- **Reset State ( $S=0, R=1$ ):** When R goes to 1, it forces the output of the top NOR gate ( $Q$ ) to become 0. This 0 is fed to the bottom NOR gate along with  $S=0$ . The inputs (0,0) to the bottom NOR gate force its output ( $Q'$ ) to become 1. The latch is now "reset" to 0.

- **Invalid State ( $S=1, R=1$ ):** This state is forbidden. It forces both  $Q$  and  $Q'$  to 0, which violates the rule that they must be complements. If S and R then return to 0 simultaneously, the final state of the latch is unpredictable.

Table 3.1: S-R Latch Characteristic Table

| S | R | $Q_{\text{next}}$ | Action        |

|---|---|-------------------|---------------|

| 0 | 0 | $Q$               | Hold (Memory) |

| 0 | 1 | 0                 | Reset         |

| 1 | 0 | 1                 | Set           |

| 1 | 1 | ?                 | Invalid       |

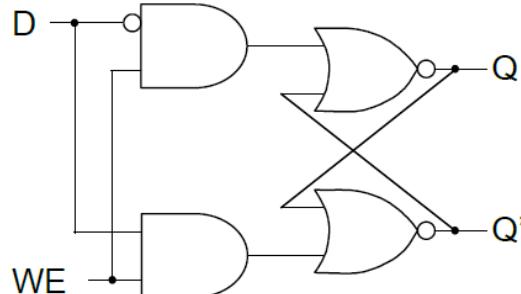

### The Gated D Latch: Controlling When to Write

The S-R latch is useful but has two issues: the invalid state and the fact that we need two inputs to control one output. We can solve both by creating a **Gated D Latch** (Data Latch). The goal is to have a circuit that says: "When I give the signal, store the value of this one data input, D."

We build it from an S-R latch, but add a control input, often called a clock (**CLK**) or Write Enable (**WE**).

Image of a Gated D Latch circuit diagram

The behavior is now much simpler:

- When **CLK = 0**, the latch is **opaque**. The AND gates are disabled, forcing S and R to 0. The internal S-R latch enters its "hold" state, ignoring any changes on the D input and preserving its stored value.

- When **CLK = 1**, the latch is **transparent**. The AND gates are enabled. If D=1, S becomes 1 and the latch is set. If D=0, S becomes 0 and R becomes 1 (because

### 3 Digital Logic

of the inverter), and the latch is reset. In this mode, the output Q simply follows the input D.

Table 3.2: Gated D Latch Characteristic Table

| CLK | D | Q <sub>next</sub> | Action            |

|-----|---|-------------------|-------------------|

| 0   | X | Q                 | Hold (Memory)     |

| 1   | 0 | 0                 | Reset (Follows D) |

| 1   | 1 | 1                 | Set (Follows D)   |

X = Don't Care

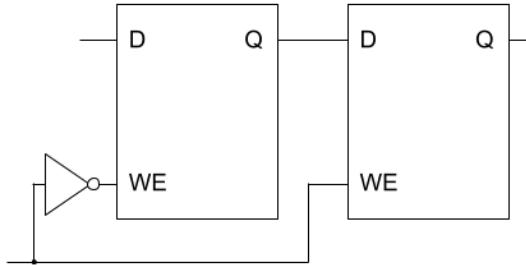

### The D Flip-Flop: Edge-Triggered Memory

The D Latch solves some problems, but its transparency can be an issue in larger circuits. If D changes while CLK is still high, the output will change too. This can lead to unpredictable behavior. We need a way to capture a value at a *precise instant* in time. This is the job of a **flip-flop**.

First, let's formally introduce the **Clock (CLK)** signal. In a modern computer, the clock is a continuous, oscillating electrical signal (a square wave) that synchronizes the actions of all circuits. It acts like a metronome for the entire processor. When you hear about a processor with a speed of 4.5 GHz, that means this clock signal oscillates 4.5 billion times per second! The critical moments for a flip-flop are the transitions of this signal: the **rising edge** (when it goes from 0 to 1) and the **falling edge** (when it goes from 1 to 0).

A **D Flip-Flop** is an **edge-triggered** device. It only changes its output at one of these precise moments (typically the rising edge). It is commonly built using two D latches in a master-slave configuration.

Image of a D Flip-Flop built from two D Latches (Master-Slave)

Here is how it achieves its edge-triggered behavior:

1. **When CLK is low (0):** The first latch (master) is transparent and captures the value from D. The second latch (slave) is opaque, holding the previous value and keeping the final output Q stable.

2. **On the RISING EDGE of CLK (0 → 1):** This is the magic instant. The master latch becomes opaque, locking in the value of D. Simultaneously, the slave

latch becomes transparent, allowing the value just captured by the master to pass through to the final output Q.

3. **When CLK is high (1):** The master latch remains opaque, ignoring any new changes on D. The slave latch remains transparent, but its input from the master is now stable. The final output Q is held constant.

The net effect is that the D flip-flop takes a "snapshot" of the D input at the exact moment of the rising clock edge and holds that value until the next rising edge. This predictable, synchronized behavior makes the D flip-flop the fundamental building block for registers, which store all the data being actively used by the processor.

#### Cheatsheet: Latches and Flip-Flops

- **Sequential vs. Combinational:** Sequential circuits have memory (**state**); Combinational circuits do not.

- **S-R Latch:** The most basic memory cell, built with cross-coupled gates. It has Set (S), Reset (R), and Hold states. S=1, R=1 is an invalid state.

- **D Latch:** A “transparent” or **level-triggered** memory element. When its CLK input is 1, the output Q follows the data input D. When CLK is 0, it holds its value.

- **D Flip-Flop:** An **edge-triggered** memory element. It captures the value of the D input only at a precise instant—the **rising edge** of the clock signal. This is the fundamental building block for processor registers.

#### Memory Organization: Register Files and RAM

A single flip-flop can store a single bit. To build a useful computer, we need to store thousands or even billions of bits. More importantly, we need a systematic way to access a specific piece of data from this vast collection. This is achieved by organizing our memory elements into a structured grid, as shown in the diagram below. This basic organization is the principle behind both small register files and large-scale RAM (Random Access Memory).

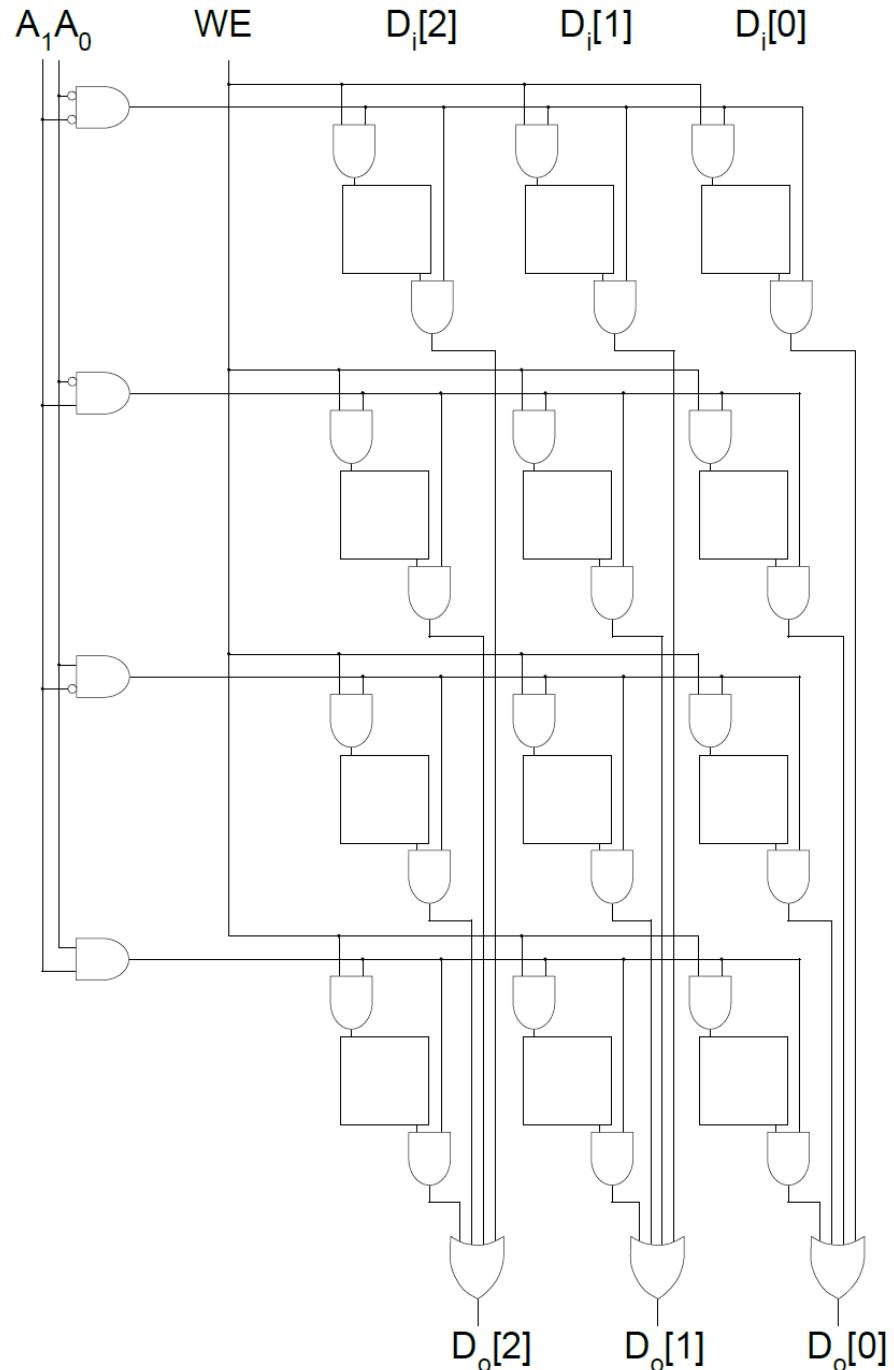

Figure 3.8: Diagram of a 4x3 Memory Array

The diagram shows a simple memory with 4 locations, where each location can store a 3-bit value. Let's break down how it works by examining its inputs and outputs.

## The Core Components of Memory

**Address Lines** How do we tell the memory *which* of the four locations we want to interact with? We use the **address lines**, labeled  $A[1:0]$  in the diagram. An address is a binary number that uniquely identifies a location. Since our address input is 2 bits wide, we can specify  $2^2 = 4$  unique locations (addresses 00, 01, 10, and 11).

On the left side of the diagram, these address lines feed into a **decoder**. The decoder's job is to take the binary address and activate a single "word line" corresponding to that address. For example, if the address is 10, the third word line from the top will be activated (set to 1) while all others remain 0.

**Data Lines** The data lines are the wires that carry the actual information being stored or retrieved. In this memory, the data is 3 bits wide.

- **Data In ( $D_i[2:0]$ )**: When we want to write to memory, we place the 3-bit value we want to store onto these input lines.

- **Data Out ( $D_o[2:0]$ )**: When we read from memory, the 3-bit value stored at the selected address appears on these output lines.

**Write Enable (WE)** The **Write Enable (WE)** is a crucial control signal that tells the memory whether to perform a read or a write operation.

- When **WE = 1**, the memory is in **write mode**. As you can see in the diagram, the 'WE' signal is ANDed with the output of the address decoder. This ensures that the clock/enable signal is only sent to the memory cells in the single, selected row, allowing the  $D_i$  values to be written into them.

- When **WE = 0**, the memory is in **read mode**. The write signal to all memory cells is disabled. Instead, the output logic at the bottom of the diagram is enabled.

The output logic itself is a set of large OR gates. The value from each cell in a column is ANDed with its corresponding word line. This means that only the data from the selected row will pass through the AND gates; the data from all other rows becomes 0. The OR gates then combine these results, effectively selecting the data from the one active row and passing it to the ' $D_o$ ' lines.

## Addressability and Address Space

This example allows us to define two critical terms for any memory system:

- **Addressability**: This refers to the size of the data, in bits, stored at each unique address. It is the "width" of the memory. In our diagram, each of the 4 locations holds 3 bits, so the **addressability is 3 bits**. Most modern computers are **byte-addressable**, meaning each unique address holds an 8-bit byte.

- **Address Space:** This is the total number of unique locations that the memory can store. It is determined by the number of address bits ( $N$ ). The address space is simply  $2^N$ . For our diagram with 2 address bits, the **address space is**  $2^2 = 4$  locations. A processor with 32 address lines can access an address space of  $2^{32}$  locations, which is 4 gigabytes (assuming byte-addressability).

#### Cheatsheet: Memory Organization

- **Memory** is a grid of storage cells (latches or flip-flops) organized into addressable locations.

- The **Address Lines** are the input that selects *which* location to read from or write to.

- The **Data Lines** carry the actual data being written ( $D_{in}$ ) or read ( $D_{out}$ ).

- The **Write Enable (WE)** control line specifies the operation: read ( $WE=0$ ) or write ( $WE=1$ ).

- **Addressability:** The number of bits stored in each location (the memory "width"). Common addressability is 8 bits (a byte).

- **Address Space:** The total number of unique locations. For a memory with  $N$  address lines, the address space is  $2^N$ .

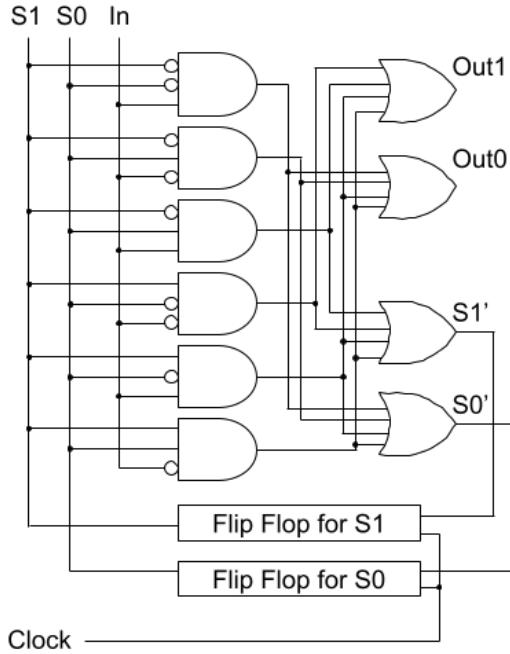

## The Finite State Machine: Circuits with a Purpose

So far, we have seen two types of circuits: combinational logic (like an adder) whose output depends only on the current inputs, and memory elements (like a flip-flop) that simply store a value. What happens when we combine them? We get a circuit that can remember its past and make decisions based on that memory. This powerful concept is formalized as a **Finite State Machine**, or **FSM**.

An FSM is a model of computation that can be in one of a finite number of *states*. It moves between these states in response to external *inputs*. A great analogy is a simple traffic light controller at an intersection. It can be in a state like "North-South Green" or "East-West Green." An input, such as a timer expiring, causes it to *transition* to a new state, like "North-South Yellow." The FSM remembers which direction has the green light and follows a strict set of rules to cycle through its states. It's a circuit with a memory and a purpose.

## The Language of State Machines

We describe FSMs visually using a **state diagram**. This diagram has three key components:

- **States:** Represented by circles. A state is a snapshot of the system's history. The machine can only be in one state at any given time.

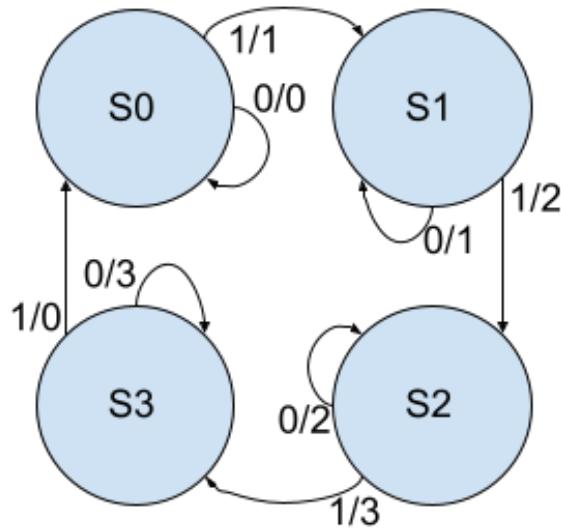

Figure 3.9: State diagram for a modulo 4 counter that outputs its current count each input.

- **Transitions:** Represented by arrows between states. A transition is the move from one state to another.

- **Labels:** Each transition arrow has a label in the format **Input / Output**. The *input* is the condition that must be true for this transition to occur. The *output* is the action or value produced when this transition is taken.

### Examples of Finite State Machines

The world is full of processes that can be modeled as FSMs. Thinking in terms of states, inputs, and transitions is a powerful problem-solving skill.

- **A Day in the Life of a Cat:** A cat's life can be modeled as a simple FSM.

- **States:** Sleeping, Eating, Playing.

- **Inputs:** 'owner appears', 'bowl is full', 'sees toy', 'gets tired'.

- **Example Transition:** If the cat is in the **Sleeping** state and the input 'owner appears' occurs, it transitions to the **Playing** state and produces the output 'Purr'.

- **A Basketball Game:** The flow of a basketball game follows FSM rules.

- **States:** Team A Possession, Team B Possession, Free Throws, Timeout.

- **Inputs:** 'made basket', 'defensive rebound', 'foul', 'violation'.

- **Example Transition:** If the game is in the Team A Possession state and the input ‘made basket’ occurs, it transitions to the Team B Possession state and the output is ‘add 2 points to Team A’s score’.

- **An Automatic Door:** The controller for a supermarket door is a classic FSM.