|

gem5

|

|

gem5

|

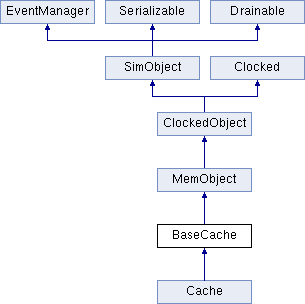

A basic cache interface. More...

#include <base.hh>

Classes | |

| class | CacheMasterPort |

| A cache master port is used for the memory-side port of the cache, and in addition to the basic timing port that only sends response packets through a transmit list, it also offers the ability to schedule and send request packets (requests & writebacks). More... | |

| class | CacheSlavePort |

| A cache slave port is used for the CPU-side port of the cache, and it is basically a simple timing port that uses a transmit list for responses to the CPU (or connected master). More... | |

Public Types | |

| enum | BlockedCause { Blocked_NoMSHRs = MSHRQueue_MSHRs, Blocked_NoWBBuffers = MSHRQueue_WriteBuffer, Blocked_NoTargets, NUM_BLOCKED_CAUSES } |

| Reasons for caches to be blocked. More... | |

Public Types inherited from MemObject Public Types inherited from MemObject | |

| typedef MemObjectParams | Params |

Public Types inherited from ClockedObject Public Types inherited from ClockedObject | |

| typedef ClockedObjectParams | Params |

| Parameters of ClockedObject. More... | |

Public Types inherited from SimObject Public Types inherited from SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| virtual void | regStats () |

| Register stats for this object. More... | |

| BaseCache (const BaseCacheParams *p, unsigned blk_size) | |

| ~BaseCache () | |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| virtual BaseMasterPort & | getMasterPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a master port with a given name and index. More... | |

| virtual BaseSlavePort & | getSlavePort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a slave port with a given name and index. More... | |

| unsigned | getBlockSize () const |

| Query block size of a cache. More... | |

| const AddrRangeList & | getAddrRanges () const |

| MSHR * | allocateMissBuffer (PacketPtr pkt, Tick time, bool sched_send=true) |

| void | allocateWriteBuffer (PacketPtr pkt, Tick time) |

| bool | isBlocked () const |

| Returns true if the cache is blocked for accesses. More... | |

| void | setBlocked (BlockedCause cause) |

| Marks the access path of the cache as blocked for the given cause. More... | |

| void | clearBlocked (BlockedCause cause) |

| Marks the cache as unblocked for the given cause. More... | |

| void | schedMemSideSendEvent (Tick time) |

| Schedule a send event for the memory-side port. More... | |

| virtual bool | inCache (Addr addr, bool is_secure) const =0 |

| virtual bool | inMissQueue (Addr addr, bool is_secure) const =0 |

| void | incMissCount (PacketPtr pkt) |

| void | incHitCount (PacketPtr pkt) |

Public Member Functions inherited from MemObject Public Member Functions inherited from MemObject | |

| const Params * | params () const |

| MemObject (const Params *params) | |

Public Member Functions inherited from ClockedObject Public Member Functions inherited from ClockedObject | |

| ClockedObject (const ClockedObjectParams *p) | |

| const Params * | params () const |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

| Enums::PwrState | pwrState () const |

| std::string | pwrStateName () const |

| std::vector< double > | pwrStateWeights () const |

| Returns the percentage residency for each power state. More... | |

| void | computeStats () |

| Record stats values like state residency by computing the time difference from previous update. More... | |

| void | pwrState (Enums::PwrState) |

| void | regStats () override |

| Register statistics for this object. More... | |

Public Member Functions inherited from SimObject Public Member Functions inherited from SimObject | |

| const Params * | params () const |

| SimObject (const Params *_params) | |

| virtual | ~SimObject () |

| virtual const std::string | name () const |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| virtual void | resetStats () |

| Reset statistics associated with this object. More... | |

| virtual void | regProbePoints () |

| Register probe points for this object. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from EventManager Public Member Functions inherited from EventManager | |

| EventManager (EventManager &em) | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick)-1) |

| void | setCurTick (Tick newVal) |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from Drainable Public Member Functions inherited from Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Public Member Functions inherited from Clocked Public Member Functions inherited from Clocked | |

| void | updateClockPeriod () const |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Public Attributes | |

| System * | system |

| System we are currently operating in. More... | |

| Stats::Vector | hits [MemCmd::NUM_MEM_CMDS] |

| Number of hits per thread for each type of command. More... | |

| Stats::Formula | demandHits |

| Number of hits for demand accesses. More... | |

| Stats::Formula | overallHits |

| Number of hit for all accesses. More... | |

| Stats::Vector | misses [MemCmd::NUM_MEM_CMDS] |

| Number of misses per thread for each type of command. More... | |

| Stats::Formula | demandMisses |

| Number of misses for demand accesses. More... | |

| Stats::Formula | overallMisses |

| Number of misses for all accesses. More... | |

| Stats::Vector | missLatency [MemCmd::NUM_MEM_CMDS] |

| Total number of cycles per thread/command spent waiting for a miss. More... | |

| Stats::Formula | demandMissLatency |

| Total number of cycles spent waiting for demand misses. More... | |

| Stats::Formula | overallMissLatency |

| Total number of cycles spent waiting for all misses. More... | |

| Stats::Formula | accesses [MemCmd::NUM_MEM_CMDS] |

| The number of accesses per command and thread. More... | |

| Stats::Formula | demandAccesses |

| The number of demand accesses. More... | |

| Stats::Formula | overallAccesses |

| The number of overall accesses. More... | |

| Stats::Formula | missRate [MemCmd::NUM_MEM_CMDS] |

| The miss rate per command and thread. More... | |

| Stats::Formula | demandMissRate |

| The miss rate of all demand accesses. More... | |

| Stats::Formula | overallMissRate |

| The miss rate for all accesses. More... | |

| Stats::Formula | avgMissLatency [MemCmd::NUM_MEM_CMDS] |

| The average miss latency per command and thread. More... | |

| Stats::Formula | demandAvgMissLatency |

| The average miss latency for demand misses. More... | |

| Stats::Formula | overallAvgMissLatency |

| The average miss latency for all misses. More... | |

| Stats::Vector | blocked_cycles |

| The total number of cycles blocked for each blocked cause. More... | |

| Stats::Vector | blocked_causes |

| The number of times this cache blocked for each blocked cause. More... | |

| Stats::Formula | avg_blocked |

| The average number of cycles blocked for each blocked cause. More... | |

| Stats::Scalar | unusedPrefetches |

| The number of times a HW-prefetched block is evicted w/o reference. More... | |

| Stats::Vector | writebacks |

| Number of blocks written back per thread. More... | |

| Stats::Vector | mshr_hits [MemCmd::NUM_MEM_CMDS] |

| Number of misses that hit in the MSHRs per command and thread. More... | |

| Stats::Formula | demandMshrHits |

| Demand misses that hit in the MSHRs. More... | |

| Stats::Formula | overallMshrHits |

| Total number of misses that hit in the MSHRs. More... | |

| Stats::Vector | mshr_misses [MemCmd::NUM_MEM_CMDS] |

| Number of misses that miss in the MSHRs, per command and thread. More... | |

| Stats::Formula | demandMshrMisses |

| Demand misses that miss in the MSHRs. More... | |

| Stats::Formula | overallMshrMisses |

| Total number of misses that miss in the MSHRs. More... | |

| Stats::Vector | mshr_uncacheable [MemCmd::NUM_MEM_CMDS] |

| Number of misses that miss in the MSHRs, per command and thread. More... | |

| Stats::Formula | overallMshrUncacheable |

| Total number of misses that miss in the MSHRs. More... | |

| Stats::Vector | mshr_miss_latency [MemCmd::NUM_MEM_CMDS] |

| Total cycle latency of each MSHR miss, per command and thread. More... | |

| Stats::Formula | demandMshrMissLatency |

| Total cycle latency of demand MSHR misses. More... | |

| Stats::Formula | overallMshrMissLatency |

| Total cycle latency of overall MSHR misses. More... | |

| Stats::Vector | mshr_uncacheable_lat [MemCmd::NUM_MEM_CMDS] |

| Total cycle latency of each MSHR miss, per command and thread. More... | |

| Stats::Formula | overallMshrUncacheableLatency |

| Total cycle latency of overall MSHR misses. More... | |

| Stats::Formula | mshrMissRate [MemCmd::NUM_MEM_CMDS] |

| The miss rate in the MSHRs pre command and thread. More... | |

| Stats::Formula | demandMshrMissRate |

| The demand miss rate in the MSHRs. More... | |

| Stats::Formula | overallMshrMissRate |

| The overall miss rate in the MSHRs. More... | |

| Stats::Formula | avgMshrMissLatency [MemCmd::NUM_MEM_CMDS] |

| The average latency of an MSHR miss, per command and thread. More... | |

| Stats::Formula | demandAvgMshrMissLatency |

| The average latency of a demand MSHR miss. More... | |

| Stats::Formula | overallAvgMshrMissLatency |

| The average overall latency of an MSHR miss. More... | |

| Stats::Formula | avgMshrUncacheableLatency [MemCmd::NUM_MEM_CMDS] |

| The average latency of an MSHR miss, per command and thread. More... | |

| Stats::Formula | overallAvgMshrUncacheableLatency |

| The average overall latency of an MSHR miss. More... | |

Protected Types | |

| enum | MSHRQueueIndex { MSHRQueue_MSHRs, MSHRQueue_WriteBuffer } |

| Indexes to enumerate the MSHR queues. More... | |

Protected Member Functions | |

| void | markInService (MSHR *mshr, bool pending_modified_resp) |

| Mark a request as in service (sent downstream in the memory system), effectively making this MSHR the ordering point. More... | |

| void | markInService (WriteQueueEntry *entry) |

| virtual bool | allocOnFill (MemCmd cmd) const =0 |

| Determine if we should allocate on a fill or not. More... | |

| virtual void | memWriteback ()=0 |

| Write back dirty blocks in the cache using functional accesses. More... | |

| virtual void | memInvalidate ()=0 |

| Invalidates all blocks in the cache. More... | |

| virtual bool | isDirty () const =0 |

| Determine if there are any dirty blocks in the cache. More... | |

| bool | inRange (Addr addr) const |

| Determine if an address is in the ranges covered by this cache. More... | |

Protected Member Functions inherited from Drainable Protected Member Functions inherited from Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. More... | |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from Clocked Protected Member Functions inherited from Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

Protected Attributes | |

| CacheSlavePort * | cpuSidePort |

| CacheMasterPort * | memSidePort |

| MSHRQueue | mshrQueue |

| Miss status registers. More... | |

| WriteQueue | writeBuffer |

| Write/writeback buffer. More... | |

| const unsigned | blkSize |

| Block size of this cache. More... | |

| const Cycles | lookupLatency |

| The latency of tag lookup of a cache. More... | |

| const Cycles | dataLatency |

| The latency of data access of a cache. More... | |

| const Cycles | forwardLatency |

| This is the forward latency of the cache. More... | |

| const Cycles | fillLatency |

| The latency to fill a cache block. More... | |

| const Cycles | responseLatency |

| The latency of sending reponse to its upper level cache/core on a linefill. More... | |

| const int | numTarget |

| The number of targets for each MSHR. More... | |

| bool | forwardSnoops |

| Do we forward snoops from mem side port through to cpu side port? More... | |

| const bool | isReadOnly |

| Is this cache read only, for example the instruction cache, or table-walker cache. More... | |

| uint8_t | blocked |

| Bit vector of the blocking reasons for the access path. More... | |

| uint64_t | order |

| Increasing order number assigned to each incoming request. More... | |

| Cycles | blockedCycle |

| Stores time the cache blocked for statistics. More... | |

| MSHR * | noTargetMSHR |

| Pointer to the MSHR that has no targets. More... | |

| Counter | missCount |

| The number of misses to trigger an exit event. More... | |

| const AddrRangeList | addrRanges |

| The address range to which the cache responds on the CPU side. More... | |

Protected Attributes inherited from ClockedObject Protected Attributes inherited from ClockedObject | |

| Enums::PwrState | _currPwrState |

| To keep track of the current power state. More... | |

| Tick | prvEvalTick |

| Stats::Scalar | numPwrStateTransitions |

| Stats::Distribution | pwrStateClkGateDist |

| Stats::Vector | pwrStateResidencyTicks |

Protected Attributes inherited from SimObject Protected Attributes inherited from SimObject | |

| const SimObjectParams * | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from EventManager Protected Attributes inherited from EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

Additional Inherited Members | |

Static Public Member Functions inherited from SimObject Static Public Member Functions inherited from SimObject | |

| static void | serializeAll (CheckpointOut &cp) |

| Serialize all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Get the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| static void | unserializeGlobals (CheckpointIn &cp) |

Static Public Attributes inherited from Serializable Static Public Attributes inherited from Serializable | |

| static int | ckptCount = 0 |

| static int | ckptMaxCount = 0 |

| static int | ckptPrevCount = -1 |

A basic cache interface.

Implements some common functions for speed.

|

protected |

| BaseCache::BaseCache | ( | const BaseCacheParams * | p, |

| unsigned | blk_size | ||

| ) |

Definition at line 489 of file base.hh.

References MSHRQueue::allocate(), allocOnFill(), blkSize, Packet::getBlockAddr(), Queue< Entry >::isFull(), mshrQueue, MSHRQueue_MSHRs, order, schedMemSideSendEvent(), and setBlocked().

Referenced by Cache::getNextQueueEntry(), and Cache::recvTimingReq().

Definition at line 507 of file base.hh.

References WriteQueue::allocate(), blkSize, MemCmd::CleanEvict, Packet::cmd, DPRINTF, Queue< Entry >::findMatch(), Packet::getBlockAddr(), QueueEntry::inService, Queue< Entry >::isFull(), Packet::isSecure(), Packet::isWrite(), MSHRQueue_WriteBuffer, order, Packet::print(), schedMemSideSendEvent(), setBlocked(), and writeBuffer.

Referenced by Cache::doWritebacks(), Cache::recvTimingReq(), and Cache::recvTimingResp().

|

protectedpure virtual |

Determine if we should allocate on a fill or not.

Implemented in Cache.

Referenced by allocateMissBuffer().

|

inline |

Marks the cache as unblocked for the given cause.

This also clears the blocked flags in the appropriate interfaces.

| cause | The newly unblocked cause. |

Definition at line 562 of file base.hh.

References blocked, blocked_cycles, blockedCycle, BaseCache::CacheSlavePort::clearBlocked(), cpuSidePort, Clocked::curCycle(), and DPRINTF.

Referenced by markInService(), Cache::recvTimingResp(), and Cache::sendMSHRQueuePacket().

|

inline |

Definition at line 487 of file base.hh.

References addrRanges.

|

inline |

Query block size of a cache.

Definition at line 482 of file base.hh.

References blkSize.

Referenced by BasePrefetcher::setCache().

|

virtual |

Get a master port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic base master port.

| if_name | Port name |

| idx | Index in the case of a VectorPort |

Reimplemented from MemObject.

Definition at line 147 of file base.cc.

References MemObject::getMasterPort(), and memSidePort.

|

virtual |

Get a slave port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic base master port.

| if_name | Port name |

| idx | Index in the case of a VectorPort |

Reimplemented from MemObject.

Definition at line 157 of file base.cc.

References cpuSidePort, and MemObject::getSlavePort().

|

pure virtual |

Implemented in Cache.

Referenced by BasePrefetcher::inCache().

|

inline |

Definition at line 601 of file base.hh.

References Packet::cmdToIndex(), hits, Request::masterId(), System::maxMasters(), Packet::req, and system.

Referenced by Cache::access().

|

inline |

Definition at line 590 of file base.hh.

References Packet::cmdToIndex(), exitSimLoop(), Request::incAccessDepth(), Request::masterId(), System::maxMasters(), missCount, misses, Packet::req, and system.

Referenced by Cache::access().

|

virtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from SimObject.

Definition at line 138 of file base.cc.

References cpuSidePort, fatal, forwardSnoops, BaseMasterPort::isConnected(), BaseSlavePort::isConnected(), SlavePort::isSnooping(), memSidePort, SimObject::name(), and SlavePort::sendRangeChange().

|

pure virtual |

Implemented in Cache.

Referenced by BasePrefetcher::inMissQueue().

|

protected |

Determine if an address is in the ranges covered by this cache.

This is useful to filter snoops.

| addr | Address to check against |

Definition at line 167 of file base.cc.

References addrRanges, and MipsISA::r.

Referenced by Cache::recvAtomicSnoop(), and Cache::recvTimingSnoopReq().

|

inline |

|

protectedpure virtual |

Determine if there are any dirty blocks in the cache.

Implemented in Cache.

|

inlineprotected |

Mark a request as in service (sent downstream in the memory system), effectively making this MSHR the ordering point.

Definition at line 200 of file base.hh.

References Blocked_NoMSHRs, clearBlocked(), Queue< Entry >::isFull(), MSHRQueue::markInService(), and mshrQueue.

Referenced by Cache::access(), Cache::recvTimingSnoopReq(), Cache::sendMSHRQueuePacket(), and Cache::sendWriteQueuePacket().

|

inlineprotected |

Definition at line 210 of file base.hh.

References Blocked_NoWBBuffers, clearBlocked(), Queue< Entry >::isFull(), WriteQueue::markInService(), and writeBuffer.

|

protectedpure virtual |

|

protectedpure virtual |

|

virtual |

Register stats for this object.

Reimplemented from SimObject.

Reimplemented in Cache.

Definition at line 178 of file base.cc.

References accesses, avg_blocked, avgMissLatency, avgMshrMissLatency, avgMshrUncacheableLatency, blocked_causes, blocked_cycles, Blocked_NoMSHRs, Blocked_NoTargets, demandAccesses, demandAvgMissLatency, demandAvgMshrMissLatency, demandHits, demandMisses, demandMissLatency, demandMissRate, demandMshrHits, demandMshrMisses, demandMshrMissLatency, demandMshrMissRate, Stats::DataWrap< Derived, InfoProxyType >::desc(), Stats::DataWrap< Derived, InfoProxyType >::flags(), System::getMasterName(), hits, ArmISA::i, Stats::VectorBase< Derived, Stor >::init(), System::maxMasters(), misses, missLatency, missRate, mshr_hits, mshr_miss_latency, mshr_misses, mshr_uncacheable, mshr_uncacheable_lat, mshrMissRate, SimObject::name(), Stats::DataWrap< Derived, InfoProxyType >::name(), Stats::nonan, Stats::nozero, NUM_BLOCKED_CAUSES, MemCmd::NUM_MEM_CMDS, overallAccesses, overallAvgMissLatency, overallAvgMshrMissLatency, overallAvgMshrUncacheableLatency, overallHits, overallMisses, overallMissLatency, overallMissRate, overallMshrHits, overallMshrMisses, overallMshrMissLatency, overallMshrMissRate, overallMshrUncacheable, overallMshrUncacheableLatency, ClockedObject::regStats(), Stats::DataWrapVec< Derived, InfoProxyType >::subname(), SUM_DEMAND, SUM_NON_DEMAND, system, MemCmd::toString(), Stats::total, unusedPrefetches, and writebacks.

Referenced by Cache::regStats().

|

inline |

Schedule a send event for the memory-side port.

If already scheduled, this may reschedule the event at an earlier time. When the specified time is reached, the port is free to send either a response, a request, or a prefetch request.

| time | The time when to attempt sending a packet. |

Definition at line 581 of file base.hh.

References memSidePort, and BaseCache::CacheMasterPort::schedSendEvent().

Referenced by allocateMissBuffer(), allocateWriteBuffer(), Cache::recvTimingReq(), and Cache::recvTimingResp().

|

inline |

Marks the access path of the cache as blocked for the given cause.

This also sets the blocked flag in the slave interface.

| cause | The reason for the cache blocking. |

Definition at line 543 of file base.hh.

References blocked, blocked_causes, blockedCycle, cpuSidePort, Clocked::curCycle(), DPRINTF, and BaseCache::CacheSlavePort::setBlocked().

Referenced by allocateMissBuffer(), allocateWriteBuffer(), and Cache::recvTimingReq().

|

protected |

The address range to which the cache responds on the CPU side.

Normally this is all possible memory addresses.

Definition at line 325 of file base.hh.

Referenced by getAddrRanges(), and inRange().

|

protected |

Block size of this cache.

Definition at line 259 of file base.hh.

Referenced by Cache::access(), allocateMissBuffer(), allocateWriteBuffer(), Cache::Cache(), Cache::cleanEvictBlk(), Cache::createMissPacket(), Cache::doTimingSupplyResponse(), Cache::functionalAccess(), getBlockSize(), Cache::getNextQueueEntry(), Cache::handleFill(), Cache::handleSnoop(), Cache::promoteWholeLineWrites(), Cache::recvTimingReq(), Cache::recvTimingResp(), Cache::recvTimingSnoopReq(), Cache::satisfyRequest(), Cache::writebackBlk(), and Cache::writebackVisitor().

|

protected |

Bit vector of the blocking reasons for the access path.

Definition at line 308 of file base.hh.

Referenced by BaseCache::CacheSlavePort::clearBlocked(), clearBlocked(), isBlocked(), Cache::CpuSidePort::recvTimingReq(), and setBlocked().

|

protected |

Stores time the cache blocked for statistics.

Definition at line 314 of file base.hh.

Referenced by clearBlocked(), and setBlocked().

|

protected |

Definition at line 185 of file base.hh.

Referenced by Cache::Cache(), clearBlocked(), Cache::functionalAccess(), getSlavePort(), Cache::handleSnoop(), Cache::handleUncacheableWriteResp(), init(), Cache::isCachedAbove(), Cache::recvTimingReq(), Cache::recvTimingResp(), Cache::sendMSHRQueuePacket(), setBlocked(), and Cache::~Cache().

|

protected |

|

protected |

The latency to fill a cache block.

Definition at line 281 of file base.hh.

Referenced by Cache::handleFill().

|

protected |

This is the forward latency of the cache.

It occurs when there is a cache miss and a request is forwarded downstream, in particular an outbound miss.

Definition at line 278 of file base.hh.

Referenced by Cache::doTimingSupplyResponse(), Cache::recvTimingReq(), Cache::recvTimingResp(), and Cache::recvTimingSnoopResp().

|

protected |

Do we forward snoops from mem side port through to cpu side port?

Definition at line 294 of file base.hh.

Referenced by Cache::handleSnoop(), init(), Cache::isCachedAbove(), and Cache::sendMSHRQueuePacket().

|

protected |

Is this cache read only, for example the instruction cache, or table-walker cache.

A cache that is read only should never see any writes, and should never get any dirty data (and hence never have to do any writebacks).

Definition at line 302 of file base.hh.

Referenced by Cache::access(), Cache::createMissPacket(), Cache::handleFill(), Cache::handleSnoop(), and Cache::writebackBlk().

|

protected |

The latency of tag lookup of a cache.

It occurs when there is an access to the cache.

Definition at line 265 of file base.hh.

Referenced by Cache::access(), Cache::recvAtomic(), Cache::recvAtomicSnoop(), Cache::recvTimingReq(), and Cache::recvTimingSnoopReq().

|

protected |

Definition at line 186 of file base.hh.

Referenced by Cache::Cache(), Cache::doTimingSupplyResponse(), Cache::doWritebacksAtomic(), Cache::functionalAccess(), getMasterPort(), init(), Cache::recvAtomic(), Cache::recvTimingReq(), Cache::recvTimingSnoopResp(), schedMemSideSendEvent(), Cache::sendMSHRQueuePacket(), Cache::sendWriteQueuePacket(), Cache::writebackVisitor(), and Cache::~Cache().

|

protected |

The number of misses to trigger an exit event.

Definition at line 320 of file base.hh.

Referenced by incMissCount().

|

protected |

Miss status registers.

Definition at line 191 of file base.hh.

Referenced by Cache::access(), Cache::allocateBlock(), allocateMissBuffer(), Cache::functionalAccess(), Cache::getNextQueueEntry(), Cache::inMissQueue(), markInService(), Cache::nextQueueReadyTime(), Cache::outstandingMisses(), Cache::recvTimingReq(), Cache::recvTimingResp(), Cache::recvTimingSnoopReq(), and Cache::sendMSHRQueuePacket().

|

protected |

Pointer to the MSHR that has no targets.

Definition at line 317 of file base.hh.

Referenced by Cache::recvTimingReq(), and Cache::recvTimingResp().

|

protected |

The number of targets for each MSHR.

Definition at line 291 of file base.hh.

Referenced by Cache::recvTimingReq(), and Cache::recvTimingSnoopReq().

|

protected |

Increasing order number assigned to each incoming request.

Definition at line 311 of file base.hh.

Referenced by allocateMissBuffer(), allocateWriteBuffer(), Cache::recvTimingReq(), and Cache::recvTimingSnoopReq().

|

protected |

The latency of sending reponse to its upper level cache/core on a linefill.

The responseLatency parameter captures this latency.

Definition at line 288 of file base.hh.

Referenced by Cache::handleUncacheableWriteResp(), and Cache::recvTimingResp().

| System* BaseCache::system |

System we are currently operating in.

Definition at line 329 of file base.hh.

Referenced by Cache::functionalAccess(), Cache::getNextQueueEntry(), incHitCount(), incMissCount(), BaseSetAssoc::insertBlock(), BaseSetAssoc::invalidate(), Cache::recvAtomic(), Cache::recvAtomicSnoop(), Cache::recvTimingReq(), Cache::recvTimingResp(), Cache::recvTimingSnoopReq(), Cache::recvTimingSnoopResp(), BaseTags::regStats(), and regStats().

|

protected |

Write/writeback buffer.

Definition at line 194 of file base.hh.

Referenced by Cache::access(), allocateWriteBuffer(), Cache::functionalAccess(), Cache::getNextQueueEntry(), Cache::handleFill(), markInService(), Cache::nextQueueReadyTime(), and Cache::recvTimingSnoopReq().