|

gem5

|

|

gem5

|

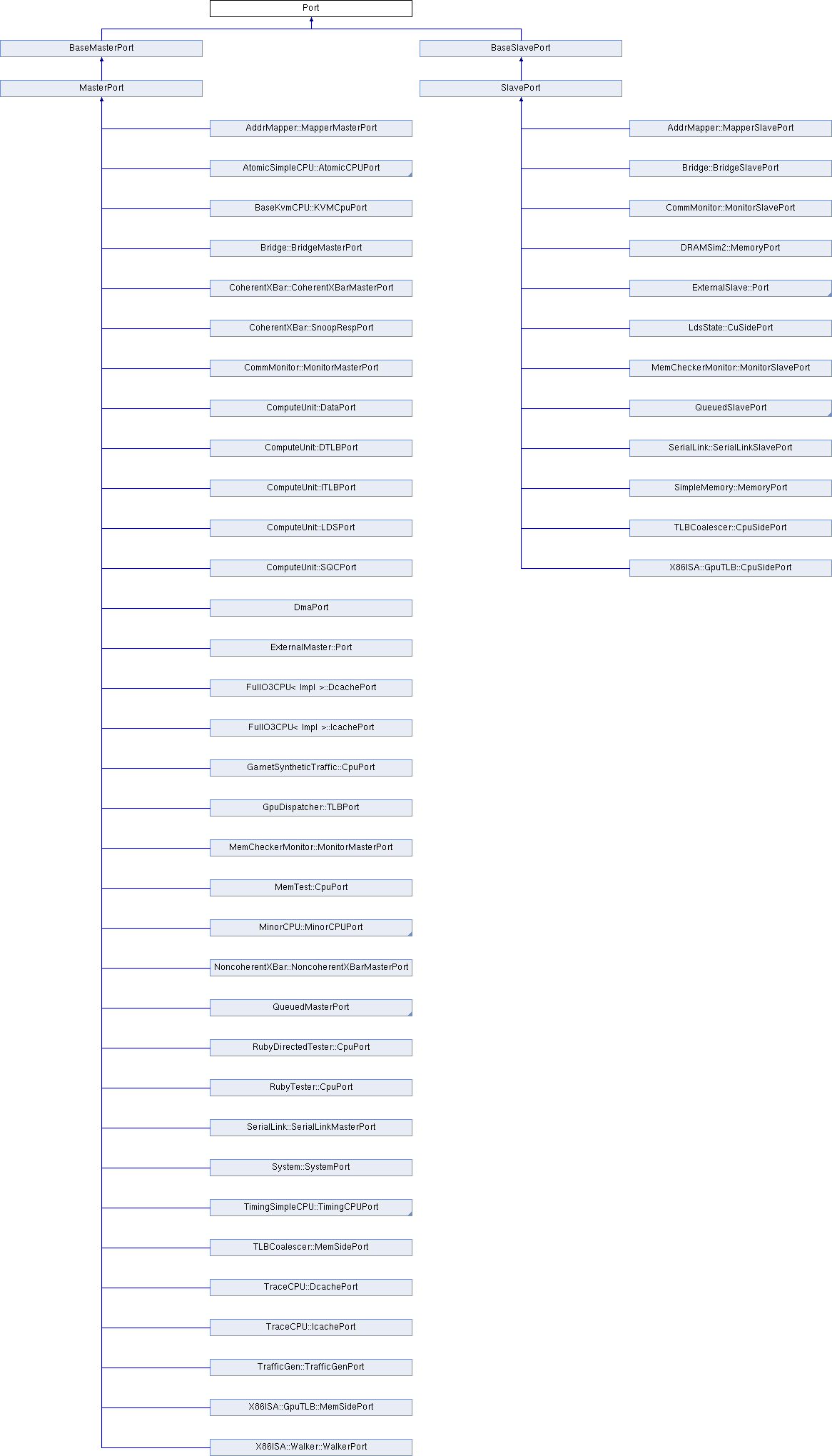

Ports are used to interface memory objects to each other. More...

#include <port.hh>

Public Member Functions | |

| const std::string | name () const |

| Return port name (for DPRINTF). More... | |

| PortID | getId () const |

| Get the port id. More... | |

Protected Member Functions | |

| Port (const std::string &_name, MemObject &_owner, PortID _id) | |

| Abstract base class for ports. More... | |

| virtual | ~Port () |

| Virtual destructor due to inheritance. More... | |

Protected Attributes | |

| const PortID | id |

| A numeric identifier to distinguish ports in a vector, and set to InvalidPortID in case this port is not part of a vector. More... | |

| MemObject & | owner |

| A reference to the MemObject that owns this port. More... | |

Private Attributes | |

| std::string | portName |

| Descriptive name (for DPRINTF output) More... | |

Ports are used to interface memory objects to each other.

A port is either a master or a slave and the connected peer is always of the opposite role. Each port has a name, an owner, and an identifier.

|

protectedvirtual |

Virtual destructor due to inheritance.

Reimplemented in ExternalMaster::Port, and ExternalSlave::Port.

|

inline |

Get the port id.

Definition at line 102 of file port.hh.

References id.

Referenced by SnoopFilter::portToMask().

|

inline |

Return port name (for DPRINTF).

Definition at line 99 of file port.hh.

References portName.

Referenced by MasterPort::bind(), BaseSlavePort::getMasterPort(), BaseMasterPort::getSlavePort(), SnoopFilter::lookupRequest(), ReqPacketQueue::name(), SnoopRespPacketQueue::name(), RespPacketQueue::name(), MessageSlavePort::recvAtomic(), MasterPort::recvAtomicSnoop(), MasterPort::recvFunctionalSnoop(), RubyDirectedTester::CpuPort::recvReqRetry(), RubyTester::CpuPort::recvReqRetry(), MasterPort::recvRetrySnoopResp(), HMCController::recvTimingReq(), NoncoherentXBar::recvTimingReq(), CoherentXBar::recvTimingReq(), NoncoherentXBar::recvTimingResp(), CoherentXBar::recvTimingResp(), MasterPort::recvTimingSnoopReq(), CoherentXBar::recvTimingSnoopResp(), SlavePort::recvTimingSnoopResp(), SlavePort::sendRangeChange(), MasterPort::unbind(), SnoopFilter::updateResponse(), SnoopFilter::updateSnoopForward(), and SnoopFilter::updateSnoopResponse().

|

protected |

|

protected |

A reference to the MemObject that owns this port.

Definition at line 80 of file port.hh.

Referenced by AtomicSimpleCPU::AtomicCPUDPort::recvAtomicSnoop(), and BaseCache::CacheSlavePort::setBlocked().

|

private |