|

gem5

|

|

gem5

|

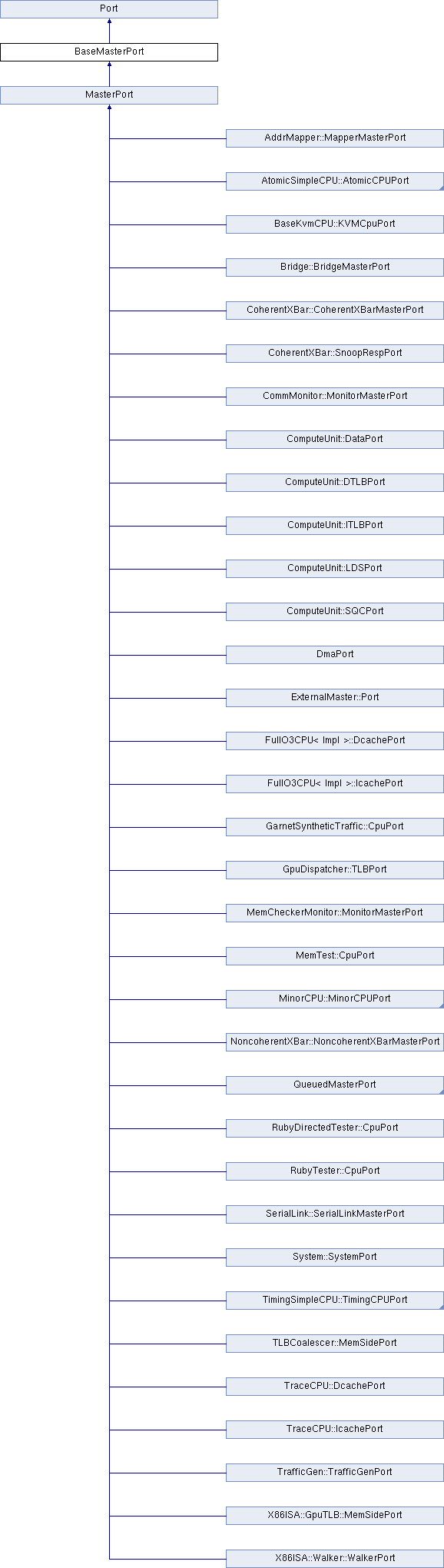

A BaseMasterPort is a protocol-agnostic master port, responsible only for the structural connection to a slave port. More...

#include <port.hh>

Public Member Functions | |

| virtual void | bind (BaseSlavePort &slave_port)=0 |

| virtual void | unbind ()=0 |

| BaseSlavePort & | getSlavePort () const |

| bool | isConnected () const |

Public Member Functions inherited from Port Public Member Functions inherited from Port | |

| const std::string | name () const |

| Return port name (for DPRINTF). More... | |

| PortID | getId () const |

| Get the port id. More... | |

Protected Member Functions | |

| BaseMasterPort (const std::string &name, MemObject *owner, PortID id=InvalidPortID) | |

| virtual | ~BaseMasterPort () |

Protected Member Functions inherited from Port Protected Member Functions inherited from Port | |

| Port (const std::string &_name, MemObject &_owner, PortID _id) | |

| Abstract base class for ports. More... | |

| virtual | ~Port () |

| Virtual destructor due to inheritance. More... | |

Protected Attributes | |

| BaseSlavePort * | _baseSlavePort |

Protected Attributes inherited from Port Protected Attributes inherited from Port | |

| const PortID | id |

| A numeric identifier to distinguish ports in a vector, and set to InvalidPortID in case this port is not part of a vector. More... | |

| MemObject & | owner |

| A reference to the MemObject that owns this port. More... | |

A BaseMasterPort is a protocol-agnostic master port, responsible only for the structural connection to a slave port.

The final master port that inherits from the base class must override the bind member function for the specific slave port class.

|

protected |

|

pure virtual |

Implemented in MasterPort.

Referenced by CxxConfigManager::bindPort(), and connectPorts().

| BaseSlavePort & BaseMasterPort::getSlavePort | ( | ) | const |

Definition at line 74 of file port.cc.

References _baseSlavePort, Port::name(), and panic.

| bool BaseMasterPort::isConnected | ( | ) | const |

Definition at line 84 of file port.cc.

References _baseSlavePort.

Referenced by CxxConfigManager::bindPort(), AddrMapper::init(), MemCheckerMonitor::init(), CommMonitor::init(), System::init(), X86ISA::IntDevice::init(), ExternalMaster::init(), DmaDevice::init(), TrafficGen::init(), SerialLink::init(), Bridge::init(), and BaseCache::init().

|

pure virtual |

Implemented in MasterPort.

|

protected |

Definition at line 120 of file port.hh.

Referenced by MasterPort::bind(), getSlavePort(), isConnected(), and MasterPort::unbind().