|

gem5

|

|

gem5

|

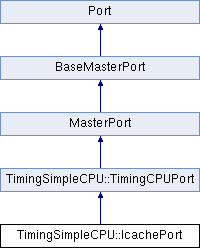

Classes | |

| struct | ITickEvent |

Public Member Functions | |

| IcachePort (TimingSimpleCPU *_cpu) | |

Public Member Functions inherited from TimingSimpleCPU::TimingCPUPort Public Member Functions inherited from TimingSimpleCPU::TimingCPUPort | |

| TimingCPUPort (const std::string &_name, TimingSimpleCPU *_cpu) | |

Public Member Functions inherited from MasterPort Public Member Functions inherited from MasterPort | |

| MasterPort (const std::string &name, MemObject *owner, PortID id=InvalidPortID) | |

| Master port. More... | |

| virtual | ~MasterPort () |

| void | bind (BaseSlavePort &slave_port) |

| Bind this master port to a slave port. More... | |

| void | unbind () |

| Unbind this master port and the associated slave port. More... | |

| Tick | sendAtomic (PacketPtr pkt) |

| Send an atomic request packet, where the data is moved and the state is updated in zero time, without interleaving with other memory accesses. More... | |

| void | sendFunctional (PacketPtr pkt) |

| Send a functional request packet, where the data is instantly updated everywhere in the memory system, without affecting the current state of any block or moving the block. More... | |

| bool | sendTimingReq (PacketPtr pkt) |

| Attempt to send a timing request to the slave port by calling its corresponding receive function. More... | |

| bool | sendTimingSnoopResp (PacketPtr pkt) |

| Attempt to send a timing snoop response packet to the slave port by calling its corresponding receive function. More... | |

| virtual void | sendRetryResp () |

| Send a retry to the slave port that previously attempted a sendTimingResp to this master port and failed. More... | |

| virtual bool | isSnooping () const |

| Determine if this master port is snooping or not. More... | |

| AddrRangeList | getAddrRanges () const |

| Get the address ranges of the connected slave port. More... | |

| void | printAddr (Addr a) |

| Inject a PrintReq for the given address to print the state of that address throughout the memory system. More... | |

Public Member Functions inherited from BaseMasterPort Public Member Functions inherited from BaseMasterPort | |

| BaseSlavePort & | getSlavePort () const |

| bool | isConnected () const |

Public Member Functions inherited from Port Public Member Functions inherited from Port | |

| const std::string | name () const |

| Return port name (for DPRINTF). More... | |

| PortID | getId () const |

| Get the port id. More... | |

Protected Member Functions | |

| virtual bool | recvTimingResp (PacketPtr pkt) |

| Receive a timing response from the slave port. More... | |

| virtual void | recvReqRetry () |

| Called by the slave port if sendTimingReq was called on this master port (causing recvTimingReq to be called on the slave port) and was unsuccesful. More... | |

Protected Member Functions inherited from MasterPort Protected Member Functions inherited from MasterPort | |

| virtual Tick | recvAtomicSnoop (PacketPtr pkt) |

| Receive an atomic snoop request packet from the slave port. More... | |

| virtual void | recvFunctionalSnoop (PacketPtr pkt) |

| Receive a functional snoop request packet from the slave port. More... | |

| virtual void | recvTimingSnoopReq (PacketPtr pkt) |

| Receive a timing snoop request from the slave port. More... | |

| virtual void | recvRetrySnoopResp () |

| Called by the slave port if sendTimingSnoopResp was called on this master port (causing recvTimingSnoopResp to be called on the slave port) and was unsuccesful. More... | |

| virtual void | recvRangeChange () |

| Called to receive an address range change from the peer slave port. More... | |

Protected Member Functions inherited from BaseMasterPort Protected Member Functions inherited from BaseMasterPort | |

| BaseMasterPort (const std::string &name, MemObject *owner, PortID id=InvalidPortID) | |

| virtual | ~BaseMasterPort () |

Protected Member Functions inherited from Port Protected Member Functions inherited from Port | |

| Port (const std::string &_name, MemObject &_owner, PortID _id) | |

| Abstract base class for ports. More... | |

| virtual | ~Port () |

| Virtual destructor due to inheritance. More... | |

Protected Attributes | |

| ITickEvent | tickEvent |

Protected Attributes inherited from TimingSimpleCPU::TimingCPUPort Protected Attributes inherited from TimingSimpleCPU::TimingCPUPort | |

| TimingSimpleCPU * | cpu |

| EventWrapper< MasterPort,&MasterPort::sendRetryResp > | retryRespEvent |

Protected Attributes inherited from BaseMasterPort Protected Attributes inherited from BaseMasterPort | |

| BaseSlavePort * | _baseSlavePort |

Protected Attributes inherited from Port Protected Attributes inherited from Port | |

| const PortID | id |

| A numeric identifier to distinguish ports in a vector, and set to InvalidPortID in case this port is not part of a vector. More... | |

| MemObject & | owner |

| A reference to the MemObject that owns this port. More... | |

|

inline |

|

protectedvirtual |

Called by the slave port if sendTimingReq was called on this master port (causing recvTimingReq to be called on the slave port) and was unsuccesful.

Implements MasterPort.

Definition at line 793 of file timing.cc.

References BaseSimpleCPU::_status, TimingSimpleCPU::TimingCPUPort::cpu, BaseSimpleCPU::IcacheRetry, BaseSimpleCPU::IcacheWaitResponse, TimingSimpleCPU::ifetch_pkt, and MasterPort::sendTimingReq().

|

protectedvirtual |

Receive a timing response from the slave port.

Implements MasterPort.

Definition at line 780 of file timing.cc.

References TimingSimpleCPU::TimingCPUPort::cpu, DPRINTF, Packet::getAddr(), TimingSimpleCPU::TimingCPUPort::TickEvent::schedule(), Event::scheduled(), and tickEvent.

|

protected |

Definition at line 206 of file timing.hh.

Referenced by recvTimingResp(), and TimingSimpleCPU::DcachePort::recvTimingResp().