|

gem5

|

|

gem5

|

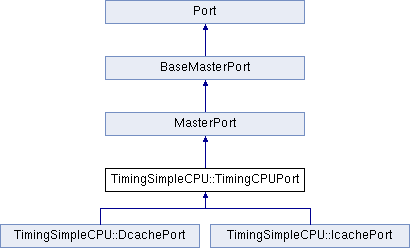

A TimingCPUPort overrides the default behaviour of the recvTiming and recvRetry and implements events for the scheduling of handling of incoming packets in the following cycle. More...

Classes | |

| struct | TickEvent |

Public Member Functions | |

| TimingCPUPort (const std::string &_name, TimingSimpleCPU *_cpu) | |

Public Member Functions inherited from MasterPort Public Member Functions inherited from MasterPort | |

| MasterPort (const std::string &name, MemObject *owner, PortID id=InvalidPortID) | |

| Master port. More... | |

| virtual | ~MasterPort () |

| void | bind (BaseSlavePort &slave_port) |

| Bind this master port to a slave port. More... | |

| void | unbind () |

| Unbind this master port and the associated slave port. More... | |

| Tick | sendAtomic (PacketPtr pkt) |

| Send an atomic request packet, where the data is moved and the state is updated in zero time, without interleaving with other memory accesses. More... | |

| void | sendFunctional (PacketPtr pkt) |

| Send a functional request packet, where the data is instantly updated everywhere in the memory system, without affecting the current state of any block or moving the block. More... | |

| bool | sendTimingReq (PacketPtr pkt) |

| Attempt to send a timing request to the slave port by calling its corresponding receive function. More... | |

| bool | sendTimingSnoopResp (PacketPtr pkt) |

| Attempt to send a timing snoop response packet to the slave port by calling its corresponding receive function. More... | |

| virtual void | sendRetryResp () |

| Send a retry to the slave port that previously attempted a sendTimingResp to this master port and failed. More... | |

| virtual bool | isSnooping () const |

| Determine if this master port is snooping or not. More... | |

| AddrRangeList | getAddrRanges () const |

| Get the address ranges of the connected slave port. More... | |

| void | printAddr (Addr a) |

| Inject a PrintReq for the given address to print the state of that address throughout the memory system. More... | |

Public Member Functions inherited from BaseMasterPort Public Member Functions inherited from BaseMasterPort | |

| BaseSlavePort & | getSlavePort () const |

| bool | isConnected () const |

Public Member Functions inherited from Port Public Member Functions inherited from Port | |

| const std::string | name () const |

| Return port name (for DPRINTF). More... | |

| PortID | getId () const |

| Get the port id. More... | |

Protected Attributes | |

| TimingSimpleCPU * | cpu |

| EventWrapper< MasterPort,&MasterPort::sendRetryResp > | retryRespEvent |

Protected Attributes inherited from BaseMasterPort Protected Attributes inherited from BaseMasterPort | |

| BaseSlavePort * | _baseSlavePort |

Protected Attributes inherited from Port Protected Attributes inherited from Port | |

| const PortID | id |

| A numeric identifier to distinguish ports in a vector, and set to InvalidPortID in case this port is not part of a vector. More... | |

| MemObject & | owner |

| A reference to the MemObject that owns this port. More... | |

Additional Inherited Members | |

Protected Member Functions inherited from MasterPort Protected Member Functions inherited from MasterPort | |

| virtual Tick | recvAtomicSnoop (PacketPtr pkt) |

| Receive an atomic snoop request packet from the slave port. More... | |

| virtual void | recvFunctionalSnoop (PacketPtr pkt) |

| Receive a functional snoop request packet from the slave port. More... | |

| virtual bool | recvTimingResp (PacketPtr pkt)=0 |

| Receive a timing response from the slave port. More... | |

| virtual void | recvTimingSnoopReq (PacketPtr pkt) |

| Receive a timing snoop request from the slave port. More... | |

| virtual void | recvReqRetry ()=0 |

| Called by the slave port if sendTimingReq was called on this master port (causing recvTimingReq to be called on the slave port) and was unsuccesful. More... | |

| virtual void | recvRetrySnoopResp () |

| Called by the slave port if sendTimingSnoopResp was called on this master port (causing recvTimingSnoopResp to be called on the slave port) and was unsuccesful. More... | |

| virtual void | recvRangeChange () |

| Called to receive an address range change from the peer slave port. More... | |

Protected Member Functions inherited from BaseMasterPort Protected Member Functions inherited from BaseMasterPort | |

| BaseMasterPort (const std::string &name, MemObject *owner, PortID id=InvalidPortID) | |

| virtual | ~BaseMasterPort () |

Protected Member Functions inherited from Port Protected Member Functions inherited from Port | |

| Port (const std::string &_name, MemObject &_owner, PortID _id) | |

| Abstract base class for ports. More... | |

| virtual | ~Port () |

| Virtual destructor due to inheritance. More... | |

A TimingCPUPort overrides the default behaviour of the recvTiming and recvRetry and implements events for the scheduling of handling of incoming packets in the following cycle.

|

inline |

|

protected |

Definition at line 167 of file timing.hh.

Referenced by TimingSimpleCPU::DcachePort::DcachePort(), TimingSimpleCPU::DcachePort::DTickEvent::process(), TimingSimpleCPU::DcachePort::recvFunctionalSnoop(), TimingSimpleCPU::IcachePort::recvReqRetry(), TimingSimpleCPU::DcachePort::recvReqRetry(), TimingSimpleCPU::IcachePort::recvTimingResp(), TimingSimpleCPU::DcachePort::recvTimingResp(), and TimingSimpleCPU::DcachePort::recvTimingSnoopReq().

|

protected |

Definition at line 179 of file timing.hh.

Referenced by TimingSimpleCPU::DcachePort::recvTimingResp().