|

gem5

|

|

gem5

|

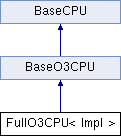

FullO3CPU class, has each of the stages (fetch through commit) within it, as well as all of the time buffers between stages. More...

#include <cpu.hh>

Classes | |

| class | DcachePort |

| DcachePort class for the load/store queue. More... | |

| class | IcachePort |

| IcachePort class for instruction fetch. More... | |

| class | TickEvent |

Public Types | |

| enum | Status { Running, Idle, Halted, Blocked, SwitchedOut } |

| enum | StageIdx { FetchIdx, DecodeIdx, RenameIdx, IEWIdx, CommitIdx, NumStages } |

| Enum to give each stage a specific index, so when calling activateStage() or deactivateStage(), they can specify which stage is being activated/deactivated. More... | |

| typedef Impl::CPUPol | CPUPolicy |

| typedef Impl::DynInstPtr | DynInstPtr |

| typedef Impl::O3CPU | O3CPU |

| typedef O3ThreadState< Impl > | ImplState |

| typedef O3ThreadState< Impl > | Thread |

| typedef std::list< DynInstPtr > ::iterator | ListIt |

| typedef CPUPolicy::TimeStruct | TimeStruct |

| Typedefs from the Impl to get the structs that each of the time buffers should use. More... | |

| typedef CPUPolicy::FetchStruct | FetchStruct |

| typedef CPUPolicy::DecodeStruct | DecodeStruct |

| typedef CPUPolicy::RenameStruct | RenameStruct |

| typedef CPUPolicy::IEWStruct | IEWStruct |

Public Member Functions | |

| FullO3CPU (DerivO3CPUParams *params) | |

| Constructs a CPU with the given parameters. More... | |

| ~FullO3CPU () | |

| Destructor. More... | |

| void | regStats () override |

| Registers statistics. More... | |

| void | regProbePoints () override |

| Register probe points. More... | |

| void | demapPage (Addr vaddr, uint64_t asn) |

| void | demapInstPage (Addr vaddr, uint64_t asn) |

| void | demapDataPage (Addr vaddr, uint64_t asn) |

| void | tick () |

| Ticks CPU, calling tick() on each stage, and checking the overall activity to see if the CPU should deschedule itself. More... | |

| void | init () override |

| Initialize the CPU. More... | |

| void | startup () override |

| int | numActiveThreads () |

| Returns the Number of Active Threads in the CPU. More... | |

| void | activateThread (ThreadID tid) |

| Add Thread to Active Threads List. More... | |

| void | deactivateThread (ThreadID tid) |

| Remove Thread from Active Threads List. More... | |

| void | insertThread (ThreadID tid) |

| Setup CPU to insert a thread's context. More... | |

| void | removeThread (ThreadID tid) |

| Remove all of a thread's context from CPU. More... | |

| Counter | totalInsts () const override |

| Count the Total Instructions Committed in the CPU. More... | |

| Counter | totalOps () const override |

| Count the Total Ops (including micro ops) committed in the CPU. More... | |

| void | activateContext (ThreadID tid) override |

| Add Thread to Active Threads List. More... | |

| void | suspendContext (ThreadID tid) override |

| Remove Thread from Active Threads List. More... | |

| void | haltContext (ThreadID tid) override |

| Remove Thread from Active Threads List && Remove Thread Context from CPU. More... | |

| void | updateThreadPriority () |

| Update The Order In Which We Process Threads. More... | |

| bool | isDraining () const |

| Is the CPU draining? More... | |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| void | unserializeThread (CheckpointIn &cp, ThreadID tid) override |

| void | syscall (int64_t callnum, ThreadID tid, Fault *fault) |

| Executes a syscall. More... | |

| DrainState | drain () override |

| Starts draining the CPU's pipeline of all instructions in order to stop all memory accesses. More... | |

| void | drainResume () override |

| Resumes execution after a drain. More... | |

| void | commitDrained (ThreadID tid) |

| Commit has reached a safe point to drain a thread. More... | |

| void | switchOut () override |

| Switches out this CPU. More... | |

| void | takeOverFrom (BaseCPU *oldCPU) override |

| Takes over from another CPU. More... | |

| void | verifyMemoryMode () const override |

| InstSeqNum | getAndIncrementInstSeq () |

| Get the current instruction sequence number, and increment it. More... | |

| void | trap (const Fault &fault, ThreadID tid, const StaticInstPtr &inst) |

| Traps to handle given fault. More... | |

| Fault | hwrei (ThreadID tid) |

| HW return from error interrupt. More... | |

| bool | simPalCheck (int palFunc, ThreadID tid) |

| Fault | getInterrupts () |

| Returns the Fault for any valid interrupt. More... | |

| void | processInterrupts (const Fault &interrupt) |

| Processes any an interrupt fault. More... | |

| void | halt () |

| Halts the CPU. More... | |

| TheISA::MiscReg | readMiscRegNoEffect (int misc_reg, ThreadID tid) const |

| Register accessors. More... | |

| TheISA::MiscReg | readMiscReg (int misc_reg, ThreadID tid) |

| Reads a misc. More... | |

| void | setMiscRegNoEffect (int misc_reg, const TheISA::MiscReg &val, ThreadID tid) |

| Sets a miscellaneous register. More... | |

| void | setMiscReg (int misc_reg, const TheISA::MiscReg &val, ThreadID tid) |

| Sets a misc. More... | |

| uint64_t | readIntReg (int reg_idx) |

| TheISA::FloatReg | readFloatReg (int reg_idx) |

| TheISA::FloatRegBits | readFloatRegBits (int reg_idx) |

| TheISA::CCReg | readCCReg (int reg_idx) |

| void | setIntReg (int reg_idx, uint64_t val) |

| void | setFloatReg (int reg_idx, TheISA::FloatReg val) |

| void | setFloatRegBits (int reg_idx, TheISA::FloatRegBits val) |

| void | setCCReg (int reg_idx, TheISA::CCReg val) |

| uint64_t | readArchIntReg (int reg_idx, ThreadID tid) |

| float | readArchFloatReg (int reg_idx, ThreadID tid) |

| uint64_t | readArchFloatRegInt (int reg_idx, ThreadID tid) |

| TheISA::CCReg | readArchCCReg (int reg_idx, ThreadID tid) |

| void | setArchIntReg (int reg_idx, uint64_t val, ThreadID tid) |

| Architectural register accessors. More... | |

| void | setArchFloatReg (int reg_idx, float val, ThreadID tid) |

| void | setArchFloatRegInt (int reg_idx, uint64_t val, ThreadID tid) |

| void | setArchCCReg (int reg_idx, TheISA::CCReg val, ThreadID tid) |

| void | pcState (const TheISA::PCState &newPCState, ThreadID tid) |

| Sets the commit PC state of a specific thread. More... | |

| TheISA::PCState | pcState (ThreadID tid) |

| Reads the commit PC state of a specific thread. More... | |

| Addr | instAddr (ThreadID tid) |

| Reads the commit PC of a specific thread. More... | |

| MicroPC | microPC (ThreadID tid) |

| Reads the commit micro PC of a specific thread. More... | |

| Addr | nextInstAddr (ThreadID tid) |

| Reads the next PC of a specific thread. More... | |

| void | squashFromTC (ThreadID tid) |

| Initiates a squash of all in-flight instructions for a given thread. More... | |

| ListIt | addInst (DynInstPtr &inst) |

| Function to add instruction onto the head of the list of the instructions. More... | |

| void | instDone (ThreadID tid, DynInstPtr &inst) |

| Function to tell the CPU that an instruction has completed. More... | |

| void | removeFrontInst (DynInstPtr &inst) |

| Remove an instruction from the front end of the list. More... | |

| void | removeInstsNotInROB (ThreadID tid) |

| Remove all instructions that are not currently in the ROB. More... | |

| void | removeInstsUntil (const InstSeqNum &seq_num, ThreadID tid) |

| Remove all instructions younger than the given sequence number. More... | |

| void | squashInstIt (const ListIt &instIt, ThreadID tid) |

| Removes the instruction pointed to by the iterator. More... | |

| void | cleanUpRemovedInsts () |

| Cleans up all instructions on the remove list. More... | |

| void | dumpInsts () |

| Debug function to print all instructions on the list. More... | |

| void | activityThisCycle () |

| Records that there was time buffer activity this cycle. More... | |

| void | activateStage (const StageIdx idx) |

| Changes a stage's status to active within the activity recorder. More... | |

| void | deactivateStage (const StageIdx idx) |

| Changes a stage's status to inactive within the activity recorder. More... | |

| void | wakeCPU () |

| Wakes the CPU, rescheduling the CPU if it's not already active. More... | |

| virtual void | wakeup (ThreadID tid) override |

| ThreadID | getFreeTid () |

| Gets a free thread id. More... | |

| ThreadContext * | tcBase (ThreadID tid) |

| Returns a pointer to a thread context. More... | |

| Fault | read (RequestPtr &req, RequestPtr &sreqLow, RequestPtr &sreqHigh, int load_idx) |

| CPU read function, forwards read to LSQ. More... | |

| Fault | write (RequestPtr &req, RequestPtr &sreqLow, RequestPtr &sreqHigh, uint8_t *data, int store_idx) |

| CPU write function, forwards write to LSQ. More... | |

| MasterPort & | getInstPort () override |

| Used by the fetch unit to get a hold of the instruction port. More... | |

| MasterPort & | getDataPort () override |

| Get the dcache port (used to find block size for translations). More... | |

Public Member Functions inherited from BaseO3CPU Public Member Functions inherited from BaseO3CPU | |

| BaseO3CPU (BaseCPUParams *params) | |

| void | regStats () |

Public Attributes | |

| TheISA::TLB * | itb |

| TheISA::TLB * | dtb |

| Status | _status |

| Overall CPU status. More... | |

| ProbePointArg< PacketPtr > * | ppInstAccessComplete |

| ProbePointArg< std::pair < DynInstPtr, PacketPtr > > * | ppDataAccessComplete |

| int | instcount |

| Count of total number of dynamic instructions in flight. More... | |

| std::list< DynInstPtr > | instList |

| List of all the instructions in flight. More... | |

| std::queue< ListIt > | removeList |

| List of all the instructions that will be removed at the end of this cycle. More... | |

| bool | removeInstsThisCycle |

| Records if instructions need to be removed this cycle due to being retired or squashed. More... | |

| TimeBuffer< TimeStruct > | timeBuffer |

| The main time buffer to do backwards communication. More... | |

| TimeBuffer< FetchStruct > | fetchQueue |

| The fetch stage's instruction queue. More... | |

| TimeBuffer< DecodeStruct > | decodeQueue |

| The decode stage's instruction queue. More... | |

| TimeBuffer< RenameStruct > | renameQueue |

| The rename stage's instruction queue. More... | |

| TimeBuffer< IEWStruct > | iewQueue |

| The IEW stage's instruction queue. More... | |

| InstSeqNum | globalSeqNum |

| The global sequence number counter. More... | |

| Checker< Impl > * | checker |

| Pointer to the checker, which can dynamically verify instruction results at run time. More... | |

| System * | system |

| Pointer to the system. More... | |

| std::vector< Thread * > | thread |

| Pointers to all of the threads in the CPU. More... | |

| std::list< int > | cpuWaitList |

| Threads Scheduled to Enter CPU. More... | |

| Cycles | lastRunningCycle |

| The cycle that the CPU was last running, used for statistics. More... | |

| Tick | lastActivatedCycle |

| The cycle that the CPU was last activated by a new thread. More... | |

| std::map< ThreadID, unsigned > | threadMap |

| Mapping for system thread id to cpu id. More... | |

| std::vector< ThreadID > | tids |

| Available thread ids in the cpu. More... | |

| Stats::Scalar | timesIdled |

| Stat for total number of times the CPU is descheduled. More... | |

| Stats::Scalar | idleCycles |

| Stat for total number of cycles the CPU spends descheduled. More... | |

| Stats::Scalar | quiesceCycles |

| Stat for total number of cycles the CPU spends descheduled due to a quiesce operation or waiting for an interrupt. More... | |

| Stats::Vector | committedInsts |

| Stat for the number of committed instructions per thread. More... | |

| Stats::Vector | committedOps |

| Stat for the number of committed ops (including micro ops) per thread. More... | |

| Stats::Formula | cpi |

| Stat for the CPI per thread. More... | |

| Stats::Formula | totalCpi |

| Stat for the total CPI. More... | |

| Stats::Formula | ipc |

| Stat for the IPC per thread. More... | |

| Stats::Formula | totalIpc |

| Stat for the total IPC. More... | |

| Stats::Scalar | intRegfileReads |

| Stats::Scalar | intRegfileWrites |

| Stats::Scalar | fpRegfileReads |

| Stats::Scalar | fpRegfileWrites |

| Stats::Scalar | ccRegfileReads |

| Stats::Scalar | ccRegfileWrites |

| Stats::Scalar | miscRegfileReads |

| Stats::Scalar | miscRegfileWrites |

Protected Attributes | |

| CPUPolicy::Fetch | fetch |

| The fetch stage. More... | |

| CPUPolicy::Decode | decode |

| The decode stage. More... | |

| CPUPolicy::Rename | rename |

| The dispatch stage. More... | |

| CPUPolicy::IEW | iew |

| The issue/execute/writeback stages. More... | |

| CPUPolicy::Commit | commit |

| The commit stage. More... | |

| PhysRegFile | regFile |

| The register file. More... | |

| CPUPolicy::FreeList | freeList |

| The free list. More... | |

| CPUPolicy::RenameMap | renameMap [Impl::MaxThreads] |

| The rename map. More... | |

| CPUPolicy::RenameMap | commitRenameMap [Impl::MaxThreads] |

| The commit rename map. More... | |

| CPUPolicy::ROB | rob |

| The re-order buffer. More... | |

| std::list< ThreadID > | activeThreads |

| Active Threads List. More... | |

| Scoreboard | scoreboard |

| Integer Register Scoreboard. More... | |

| std::vector< TheISA::ISA * > | isa |

| IcachePort | icachePort |

| Instruction port. More... | |

| DcachePort | dcachePort |

| Data port. More... | |

Private Member Functions | |

| void | scheduleTickEvent (Cycles delay) |

| Schedule tick event, regardless of its current state. More... | |

| void | unscheduleTickEvent () |

| Unschedule tick event, regardless of its current state. More... | |

| bool | tryDrain () |

| Check if the pipeline has drained and signal drain done. More... | |

| void | drainSanityCheck () const |

| Perform sanity checks after a drain. More... | |

| bool | isDrained () const |

| Check if a system is in a drained state. More... | |

Private Attributes | |

| TickEvent | tickEvent |

| The tick event used for scheduling CPU ticks. More... | |

| ActivityRecorder | activityRec |

| The activity recorder; used to tell if the CPU has any activity remaining or if it can go to idle and deschedule itself. More... | |

Friends | |

| class | O3ThreadContext< Impl > |

Additional Inherited Members | |

Static Public Member Functions inherited from BaseCPU Static Public Member Functions inherited from BaseCPU | |

| static int | numSimulatedInsts () |

| static int | numSimulatedOps () |

| static void | wakeup (ThreadID tid) |

FullO3CPU class, has each of the stages (fetch through commit) within it, as well as all of the time buffers between stages.

The tick() function for the CPU is defined here.

| typedef CPUPolicy::DecodeStruct FullO3CPU< Impl >::DecodeStruct |

| typedef Impl::DynInstPtr FullO3CPU< Impl >::DynInstPtr |

| typedef CPUPolicy::FetchStruct FullO3CPU< Impl >::FetchStruct |

| typedef O3ThreadState<Impl> FullO3CPU< Impl >::ImplState |

| typedef std::list<DynInstPtr>::iterator FullO3CPU< Impl >::ListIt |

| typedef CPUPolicy::RenameStruct FullO3CPU< Impl >::RenameStruct |

| typedef O3ThreadState<Impl> FullO3CPU< Impl >::Thread |

| typedef CPUPolicy::TimeStruct FullO3CPU< Impl >::TimeStruct |

| enum FullO3CPU::StageIdx |

Enum to give each stage a specific index, so when calling activateStage() or deactivateStage(), they can specify which stage is being activated/deactivated.

| Enumerator | |

|---|---|

| FetchIdx | |

| DecodeIdx | |

| RenameIdx | |

| IEWIdx | |

| CommitIdx | |

| NumStages | |

| enum FullO3CPU::Status |

Constructs a CPU with the given parameters.

Definition at line 159 of file cpu.cc.

References FullO3CPU< Impl >::_status, FullO3CPU< Impl >::activeThreads, FullO3CPU< Impl >::checker, FullO3CPU< Impl >::commit, FullO3CPU< Impl >::commitRenameMap, O3ThreadContext< class >::cpu, FullO3CPU< Impl >::decode, FullO3CPU< Impl >::decodeQueue, DPRINTF, fatal, FullO3CPU< Impl >::fetch, FullO3CPU< Impl >::fetchQueue, FullO3CPU< Impl >::freeList, FullSystem, FullO3CPU< Impl >::globalSeqNum, FullO3CPU< Impl >::icachePort, FullO3CPU< Impl >::iew, FullO3CPU< Impl >::iewQueue, FullO3CPU< Impl >::isa, FullO3CPU< Impl >::lastActivatedCycle, name(), AlphaISA::NumCCRegs, AlphaISA::NumFloatRegs, AlphaISA::NumIntRegs, panic, FullO3CPU< Impl >::regFile, FullO3CPU< Impl >::rename, FullO3CPU< Impl >::renameMap, FullO3CPU< Impl >::renameQueue, FullO3CPU< Impl >::rob, FullO3CPU< Impl >::Running, FullO3CPU< Impl >::scoreboard, FullO3CPU< Impl >::SwitchedOut, O3ThreadContext< class >::thread, FullO3CPU< Impl >::thread, FullO3CPU< Impl >::tids, FullO3CPU< Impl >::timeBuffer, and AlphaISA::ZeroReg.

|

inline |

| FullO3CPU< Impl >::ListIt FullO3CPU< Impl >::addInst | ( | DynInstPtr & | inst | ) |

| void FullO3CPU< Impl >::cleanUpRemovedInsts | ( | ) |

|

override |

|

override |

Resumes execution after a drain.

Definition at line 1132 of file cpu.cc.

References ThreadContext::Active, DPRINTF, ArmISA::i, Running, and ArmISA::status.

|

private |

Perform sanity checks after a drain.

This method is called from drain() when it has determined that the CPU is fully drained when gem5 is compiled with the NDEBUG macro undefined. The intention of this method is to do more extensive tests than the isDrained() method to weed out any draining bugs.

| void FullO3CPU< Impl >::dumpInsts | ( | ) |

|

inline |

|

inlineoverride |

Gets a free thread id.

Use if thread ids change across system.

Definition at line 1655 of file cpu.cc.

References InvalidThreadID.

|

inlineoverride |

|

inline |

HW return from error interrupt.

Definition at line 900 of file cpu.cc.

References AlphaISA::MISCREG_LOCKFLAG, and NoFault.

|

override |

Initialize the CPU.

Definition at line 599 of file cpu.cc.

References ThreadContext::contextId(), FullSystem, Stats::init, and AlphaISA::initCPU().

Setup CPU to insert a thread's context.

Definition at line 779 of file cpu.cc.

References ThreadContext::Active, AlphaISA::CC_Reg_Base, DPRINTF, AlphaISA::FP_Reg_Base, FullSystem, AlphaISA::NumCCRegs, AlphaISA::NumFloatRegs, AlphaISA::NumIntRegs, ThreadContext::pcState(), ThreadContext::setStatus(), and ArmISA::system.

| void FullO3CPU< Impl >::instDone | ( | ThreadID | tid, |

| DynInstPtr & | inst | ||

| ) |

Function to tell the CPU that an instruction has completed.

Definition at line 1434 of file cpu.cc.

References ArmISA::system.

|

private |

|

inline |

|

inline |

|

inline |

| CCReg FullO3CPU< Impl >::readCCReg | ( | int | reg_idx | ) |

| FloatReg FullO3CPU< Impl >::readFloatReg | ( | int | reg_idx | ) |

| FloatRegBits FullO3CPU< Impl >::readFloatRegBits | ( | int | reg_idx | ) |

| uint64_t FullO3CPU< Impl >::readIntReg | ( | int | reg_idx | ) |

|

override |

|

override |

Registers statistics.

Definition at line 427 of file cpu.cc.

References name(), PseudoInst::quiesceCycles(), BaseO3CPU::regStats(), Stats::sum(), and Stats::total.

| void FullO3CPU< Impl >::removeFrontInst | ( | DynInstPtr & | inst | ) |

| void FullO3CPU< Impl >::removeInstsUntil | ( | const InstSeqNum & | seq_num, |

| ThreadID | tid | ||

| ) |

Remove all of a thread's context from CPU.

Definition at line 834 of file cpu.cc.

References AlphaISA::CC_Reg_Base, DPRINTF, AlphaISA::FP_Reg_Base, AlphaISA::NumCCRegs, AlphaISA::NumFloatRegs, and AlphaISA::NumIntRegs.

|

override |

| void FullO3CPU< Impl >::setCCReg | ( | int | reg_idx, |

| TheISA::CCReg | val | ||

| ) |

| void FullO3CPU< Impl >::setFloatReg | ( | int | reg_idx, |

| TheISA::FloatReg | val | ||

| ) |

| void FullO3CPU< Impl >::setFloatRegBits | ( | int | reg_idx, |

| TheISA::FloatRegBits | val | ||

| ) |

| void FullO3CPU< Impl >::setIntReg | ( | int | reg_idx, |

| uint64_t | val | ||

| ) |

Definition at line 915 of file cpu.cc.

References PAL::bpt, PAL::bugchk, exitSimLoop(), PAL::halt, MipsISA::halt, System::numSystemsRunning, and ArmISA::system.

|

override |

|

override |

Takes over from another CPU.

Definition at line 1174 of file cpu.cc.

References FullO3CPU< Impl >::globalSeqNum, and takeOverFrom().

|

inline |

| void FullO3CPU< Impl >::tick | ( | ) |

Count the Total Instructions Committed in the CPU.

Definition at line 681 of file cpu.cc.

References ArmISA::i, X86ISA::size(), and Stats::total.

Count the Total Ops (including micro ops) committed in the CPU.

Definition at line 694 of file cpu.cc.

References ArmISA::i, X86ISA::size(), and Stats::total.

| void FullO3CPU< Impl >::trap | ( | const Fault & | fault, |

| ThreadID | tid, | ||

| const StaticInstPtr & | inst | ||

| ) |

|

private |

Check if the pipeline has drained and signal drain done.

This method checks if a drain has been requested and if the CPU has drained successfully (i.e., there are no instructions in the pipeline). If the CPU has drained, it deschedules the tick event and signals the drain manager.

|

inlineprivate |

|

override |

| void FullO3CPU< Impl >::updateThreadPriority | ( | ) |

|

override |

Definition at line 1196 of file cpu.cc.

References fatal, and ArmISA::system.

| void FullO3CPU< Impl >::wakeCPU | ( | ) |

Definition at line 1642 of file cpu.cc.

References DPRINTF, ArmISA::status, ThreadContext::Suspended, and PseudoInst::wakeCPU().

|

inline |

|

friend |

Overall CPU status.

Definition at line 126 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

Active Threads List.

Definition at line 559 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU(), and FullO3CPU< O3CPUImpl >::numActiveThreads().

|

private |

The activity recorder; used to tell if the CPU has any activity remaining or if it can go to idle and deschedule itself.

Definition at line 618 of file cpu.hh.

Referenced by FullO3CPU< O3CPUImpl >::activateStage(), FullO3CPU< O3CPUImpl >::activityThisCycle(), and FullO3CPU< O3CPUImpl >::deactivateStage().

| Stats::Scalar FullO3CPU< Impl >::ccRegfileReads |

| Stats::Scalar FullO3CPU< Impl >::ccRegfileWrites |

Pointer to the checker, which can dynamically verify instruction results at run time.

This can be set to NULL if it is not being used.

Definition at line 655 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

|

protected |

The commit stage.

Definition at line 541 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

|

protected |

The commit rename map.

Definition at line 553 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| Stats::Vector FullO3CPU< Impl >::committedInsts |

| Stats::Vector FullO3CPU< Impl >::committedOps |

| Stats::Formula FullO3CPU< Impl >::cpi |

|

protected |

Data port.

Note that it has to appear after the iew stages

Definition at line 570 of file cpu.hh.

Referenced by FullO3CPU< O3CPUImpl >::getDataPort().

|

protected |

The decode stage.

Definition at line 532 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| TimeBuffer<DecodeStruct> FullO3CPU< Impl >::decodeQueue |

The decode stage's instruction queue.

Definition at line 605 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| TheISA::TLB* FullO3CPU< Impl >::dtb |

Definition at line 123 of file cpu.hh.

Referenced by FullO3CPU< O3CPUImpl >::demapDataPage(), and FullO3CPU< O3CPUImpl >::demapPage().

|

protected |

The fetch stage.

Definition at line 529 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU(), and FullO3CPU< Impl >::IcachePort::recvReqRetry().

| TimeBuffer<FetchStruct> FullO3CPU< Impl >::fetchQueue |

The fetch stage's instruction queue.

Definition at line 602 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| Stats::Scalar FullO3CPU< Impl >::fpRegfileReads |

| Stats::Scalar FullO3CPU< Impl >::fpRegfileWrites |

|

protected |

| InstSeqNum FullO3CPU< Impl >::globalSeqNum |

The global sequence number counter.

Definition at line 649 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU(), FullO3CPU< O3CPUImpl >::getAndIncrementInstSeq(), and FullO3CPU< Impl >::takeOverFrom().

|

protected |

Instruction port.

Note that it has to appear after the fetch stage.

Definition at line 567 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU(), and FullO3CPU< O3CPUImpl >::getInstPort().

| Stats::Scalar FullO3CPU< Impl >::idleCycles |

|

protected |

The issue/execute/writeback stages.

Definition at line 538 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU(), FullO3CPU< O3CPUImpl >::read(), and FullO3CPU< O3CPUImpl >::write().

| TimeBuffer<IEWStruct> FullO3CPU< Impl >::iewQueue |

The IEW stage's instruction queue.

Definition at line 611 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| int FullO3CPU< Impl >::instcount |

| std::list<DynInstPtr> FullO3CPU< Impl >::instList |

| Stats::Scalar FullO3CPU< Impl >::intRegfileReads |

| Stats::Scalar FullO3CPU< Impl >::intRegfileWrites |

| Stats::Formula FullO3CPU< Impl >::ipc |

|

protected |

Definition at line 564 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| TheISA::TLB* FullO3CPU< Impl >::itb |

Definition at line 122 of file cpu.hh.

Referenced by FullO3CPU< O3CPUImpl >::demapInstPage(), and FullO3CPU< O3CPUImpl >::demapPage().

The cycle that the CPU was last activated by a new thread.

Definition at line 670 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| Stats::Scalar FullO3CPU< Impl >::miscRegfileReads |

| Stats::Scalar FullO3CPU< Impl >::miscRegfileWrites |

| ProbePointArg<std::pair<DynInstPtr, PacketPtr> >* FullO3CPU< Impl >::ppDataAccessComplete |

| ProbePointArg<PacketPtr>* FullO3CPU< Impl >::ppInstAccessComplete |

| Stats::Scalar FullO3CPU< Impl >::quiesceCycles |

|

protected |

The register file.

Definition at line 544 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| bool FullO3CPU< Impl >::removeInstsThisCycle |

|

protected |

The dispatch stage.

Definition at line 535 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

|

protected |

The rename map.

Definition at line 550 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| TimeBuffer<RenameStruct> FullO3CPU< Impl >::renameQueue |

The rename stage's instruction queue.

Definition at line 608 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

|

protected |

The re-order buffer.

Definition at line 556 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

|

protected |

Integer Register Scoreboard.

Definition at line 562 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| std::vector<Thread *> FullO3CPU< Impl >::thread |

Pointers to all of the threads in the CPU.

Definition at line 661 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU(), and FullO3CPU< O3CPUImpl >::tcBase().

The tick event used for scheduling CPU ticks.

Definition at line 215 of file cpu.hh.

Referenced by FullO3CPU< O3CPUImpl >::scheduleTickEvent(), and FullO3CPU< O3CPUImpl >::unscheduleTickEvent().

| std::vector<ThreadID> FullO3CPU< Impl >::tids |

Available thread ids in the cpu.

Definition at line 676 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| TimeBuffer<TimeStruct> FullO3CPU< Impl >::timeBuffer |

The main time buffer to do backwards communication.

Definition at line 599 of file cpu.hh.

Referenced by FullO3CPU< Impl >::FullO3CPU().

| Stats::Scalar FullO3CPU< Impl >::timesIdled |

| Stats::Formula FullO3CPU< Impl >::totalCpi |

| Stats::Formula FullO3CPU< Impl >::totalIpc |