|

gem5

|

|

gem5

|

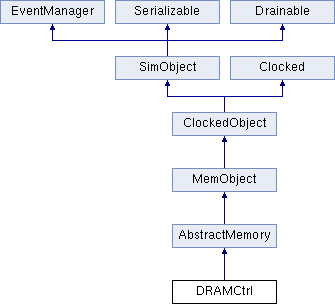

The DRAM controller is a single-channel memory controller capturing the most important timing constraints associated with a contemporary DRAM. More...

#include <dram_ctrl.hh>

Classes | |

| class | Bank |

| A basic class to track the bank state, i.e. More... | |

| class | BurstHelper |

| A burst helper helps organize and manage a packet that is larger than the DRAM burst size. More... | |

| struct | Command |

| Simple structure to hold the values needed to keep track of commands for DRAMPower. More... | |

| class | DRAMPacket |

| A DRAM packet stores packets along with the timestamp of when the packet entered the queue, and also the decoded address. More... | |

| class | MemoryPort |

| class | Rank |

| Rank class includes a vector of banks. More... | |

| class | RankDumpCallback |

Public Member Functions | |

| void | regStats () override |

| Register Statistics. More... | |

| DRAMCtrl (const DRAMCtrlParams *p) | |

| DrainState | drain () override |

| Notify an object that it needs to drain its state. More... | |

| virtual BaseSlavePort & | getSlavePort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a slave port with a given name and index. More... | |

| virtual void | init () override |

| Initialise this memory. More... | |

| virtual void | startup () override |

| startup() is the final initialization call before simulation. More... | |

| virtual void | drainResume () override |

| Resume execution after a successful drain. More... | |

| bool | allRanksDrained () const |

| Return true once refresh is complete for all ranks and there are no additional commands enqueued. More... | |

Public Member Functions inherited from AbstractMemory Public Member Functions inherited from AbstractMemory | |

| AbstractMemory (const Params *p) | |

| virtual | ~AbstractMemory () |

| bool | isNull () const |

| See if this is a null memory that should never store data and always return zero. More... | |

| void | setBackingStore (uint8_t *pmem_addr) |

| Set the host memory backing store to be used by this memory controller. More... | |

| const std::list< LockedAddr > & | getLockedAddrList () const |

| Get the list of locked addresses to allow checkpointing. More... | |

| void | addLockedAddr (LockedAddr addr) |

| Add a locked address to allow for checkpointing. More... | |

| System * | system () const |

| read the system pointer Implemented for completeness with the setter More... | |

| void | system (System *sys) |

| Set the system pointer on this memory This can't be done via a python parameter because the system needs pointers to all the memories and the reverse would create a cycle in the object graph. More... | |

| const Params * | params () const |

| AddrRange | getAddrRange () const |

| Get the address range. More... | |

| uint64_t | size () const |

| Get the memory size. More... | |

| Addr | start () const |

| Get the start address. More... | |

| bool | isConfReported () const |

| Should this memory be passed to the kernel and part of the OS physical memory layout. More... | |

| bool | isInAddrMap () const |

| Some memories are used as shadow memories or should for other reasons not be part of the global address map. More... | |

| bool | isKvmMap () const |

| When shadow memories are in use, KVM may want to make one or the other, but cannot map both into the guest address space. More... | |

| void | access (PacketPtr pkt) |

| Perform an untimed memory access and update all the state (e.g. More... | |

| void | functionalAccess (PacketPtr pkt) |

| Perform an untimed memory read or write without changing anything but the memory itself. More... | |

Public Member Functions inherited from MemObject Public Member Functions inherited from MemObject | |

| const Params * | params () const |

| MemObject (const Params *params) | |

| virtual BaseMasterPort & | getMasterPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a master port with a given name and index. More... | |

Public Member Functions inherited from ClockedObject Public Member Functions inherited from ClockedObject | |

| ClockedObject (const ClockedObjectParams *p) | |

| const Params * | params () const |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

| Enums::PwrState | pwrState () const |

| std::string | pwrStateName () const |

| std::vector< double > | pwrStateWeights () const |

| Returns the percentage residency for each power state. More... | |

| void | computeStats () |

| Record stats values like state residency by computing the time difference from previous update. More... | |

| void | pwrState (Enums::PwrState) |

| void | regStats () override |

| Register statistics for this object. More... | |

Public Member Functions inherited from SimObject Public Member Functions inherited from SimObject | |

| const Params * | params () const |

| SimObject (const Params *_params) | |

| virtual | ~SimObject () |

| virtual const std::string | name () const |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| virtual void | resetStats () |

| Reset statistics associated with this object. More... | |

| virtual void | regProbePoints () |

| Register probe points for this object. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. More... | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from EventManager Public Member Functions inherited from EventManager | |

| EventManager (EventManager &em) | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick)-1) |

| void | setCurTick (Tick newVal) |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from Drainable Public Member Functions inherited from Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Public Member Functions inherited from Clocked Public Member Functions inherited from Clocked | |

| void | updateClockPeriod () const |

| Update the tick to the current tick. More... | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. More... | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. More... | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. More... | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| Tick | recvAtomic (PacketPtr pkt) |

| void | recvFunctional (PacketPtr pkt) |

| bool | recvTimingReq (PacketPtr pkt) |

Protected Member Functions inherited from AbstractMemory Protected Member Functions inherited from AbstractMemory | |

| bool | checkLockedAddrList (PacketPtr pkt) |

| void | trackLoadLocked (PacketPtr pkt) |

| bool | writeOK (PacketPtr pkt) |

Protected Member Functions inherited from Drainable Protected Member Functions inherited from Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Protected Member Functions inherited from Clocked Protected Member Functions inherited from Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. More... | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. More... | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. More... | |

Private Types | |

| enum | BusState { READ = 0, WRITE } |

| Bus state used to control the read/write switching and drive the scheduling of the next request. More... | |

| enum | PowerState { PWR_IDLE = 0, PWR_REF, PWR_SREF, PWR_PRE_PDN, PWR_ACT, PWR_ACT_PDN } |

| The power state captures the different operational states of the DRAM and interacts with the bus read/write state machine, and the refresh state machine. More... | |

| enum | RefreshState { REF_IDLE = 0, REF_DRAIN, REF_PD_EXIT, REF_SREF_EXIT, REF_PRE, REF_START, REF_RUN } |

| The refresh state is used to control the progress of the refresh scheduling. More... | |

Private Member Functions | |

| void | processNextReqEvent () |

| Bunch of things requires to setup "events" in gem5 When event "respondEvent" occurs for example, the method processRespondEvent is called; no parameters are allowed in these methods. More... | |

| void | processRespondEvent () |

| bool | readQueueFull (unsigned int pktCount) const |

| Check if the read queue has room for more entries. More... | |

| bool | writeQueueFull (unsigned int pktCount) const |

| Check if the write queue has room for more entries. More... | |

| void | addToReadQueue (PacketPtr pkt, unsigned int pktCount) |

| When a new read comes in, first check if the write q has a pending request to the same address. If not, decode the address to populate rank/bank/row, create one or mutliple "dram_pkt", and push them to the back of the read queue. More... | |

| void | addToWriteQueue (PacketPtr pkt, unsigned int pktCount) |

| Decode the incoming pkt, create a dram_pkt and push to the back of the write queue. More... | |

| void | doDRAMAccess (DRAMPacket *dram_pkt) |

| Actually do the DRAM access - figure out the latency it will take to service the req based on bank state, channel state etc and then update those states to account for this request. Based on this, update the packet's "readyTime" and move it to the response q from where it will eventually go back to the outside world. More... | |

| void | accessAndRespond (PacketPtr pkt, Tick static_latency) |

| When a packet reaches its "readyTime" in the response Q, use the "access()" method in AbstractMemory to actually create the response packet, and send it back to the outside world requestor. More... | |

| DRAMPacket * | decodeAddr (PacketPtr pkt, Addr dramPktAddr, unsigned int size, bool isRead) |

| Address decoder to figure out physical mapping onto ranks, banks, and rows. More... | |

| bool | chooseNext (std::deque< DRAMPacket * > &queue, Tick extra_col_delay) |

| The memory schduler/arbiter - picks which request needs to go next, based on the specified policy such as FCFS or FR-FCFS and moves it to the head of the queue. More... | |

| bool | reorderQueue (std::deque< DRAMPacket * > &queue, Tick extra_col_delay) |

| For FR-FCFS policy reorder the read/write queue depending on row buffer hits and earliest bursts available in DRAM. More... | |

| std::pair< uint64_t, bool > | minBankPrep (const std::deque< DRAMPacket * > &queue, Tick min_col_at) const |

| Find which are the earliest banks ready to issue an activate for the enqueued requests. More... | |

| void | activateBank (Rank &rank_ref, Bank &bank_ref, Tick act_tick, uint32_t row) |

| Keep track of when row activations happen, in order to enforce the maximum number of activations in the activation window. More... | |

| void | prechargeBank (Rank &rank_ref, Bank &bank_ref, Tick pre_at, bool trace=true) |

| Precharge a given bank and also update when the precharge is done. More... | |

| void | printQs () const |

| Used for debugging to observe the contents of the queues. More... | |

| Addr | burstAlign (Addr addr) const |

| Burst-align an address. More... | |

| void | updatePowerStats (Rank &rank_ref) |

| This function increments the energy when called. More... | |

Static Private Member Functions | |

| static bool | sortTime (const Command &cmd, const Command &cmd_next) |

| Function for sorting Command structures based on timeStamp. More... | |

Additional Inherited Members | |

Public Types inherited from AbstractMemory Public Types inherited from AbstractMemory | |

| typedef AbstractMemoryParams | Params |

Public Types inherited from MemObject Public Types inherited from MemObject | |

| typedef MemObjectParams | Params |

Public Types inherited from ClockedObject Public Types inherited from ClockedObject | |

| typedef ClockedObjectParams | Params |

| Parameters of ClockedObject. More... | |

Public Types inherited from SimObject Public Types inherited from SimObject | |

| typedef SimObjectParams | Params |

Static Public Member Functions inherited from SimObject Static Public Member Functions inherited from SimObject | |

| static void | serializeAll (CheckpointOut &cp) |

| Serialize all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Get the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| static void | unserializeGlobals (CheckpointIn &cp) |

Static Public Attributes inherited from Serializable Static Public Attributes inherited from Serializable | |

| static int | ckptCount = 0 |

| static int | ckptMaxCount = 0 |

| static int | ckptPrevCount = -1 |

Protected Attributes inherited from AbstractMemory Protected Attributes inherited from AbstractMemory | |

| AddrRange | range |

| uint8_t * | pmemAddr |

| const bool | confTableReported |

| const bool | inAddrMap |

| const bool | kvmMap |

| std::list< LockedAddr > | lockedAddrList |

| Stats::Vector | bytesRead |

| Number of total bytes read from this memory. More... | |

| Stats::Vector | bytesInstRead |

| Number of instruction bytes read from this memory. More... | |

| Stats::Vector | bytesWritten |

| Number of bytes written to this memory. More... | |

| Stats::Vector | numReads |

| Number of read requests. More... | |

| Stats::Vector | numWrites |

| Number of write requests. More... | |

| Stats::Vector | numOther |

| Number of other requests. More... | |

| Stats::Formula | bwRead |

| Read bandwidth from this memory. More... | |

| Stats::Formula | bwInstRead |

| Read bandwidth from this memory. More... | |

| Stats::Formula | bwWrite |

| Write bandwidth from this memory. More... | |

| Stats::Formula | bwTotal |

| Total bandwidth from this memory. More... | |

| System * | _system |

| Pointor to the System object. More... | |

Protected Attributes inherited from ClockedObject Protected Attributes inherited from ClockedObject | |

| Enums::PwrState | _currPwrState |

| To keep track of the current power state. More... | |

| Tick | prvEvalTick |

| Stats::Scalar | numPwrStateTransitions |

| Stats::Distribution | pwrStateClkGateDist |

| Stats::Vector | pwrStateResidencyTicks |

Protected Attributes inherited from SimObject Protected Attributes inherited from SimObject | |

| const SimObjectParams * | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from EventManager Protected Attributes inherited from EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

The DRAM controller is a single-channel memory controller capturing the most important timing constraints associated with a contemporary DRAM.

For multi-channel memory systems, the controller is combined with a crossbar model, with the channel address interleaving taking part in the crossbar.

As a basic design principle, this controller model is not cycle callable, but instead uses events to: 1) decide when new decisions can be made, 2) when resources become available, 3) when things are to be considered done, and 4) when to send things back. Through these simple principles, the model delivers high performance, and lots of flexibility, allowing users to evaluate the system impact of a wide range of memory technologies, such as DDR3/4, LPDDR2/3/4, WideIO1/2, HBM and HMC.

For more details, please see Hansson et al, "Simulating DRAM controllers for future system architecture exploration", Proc. ISPASS, 2014. If you use this model as part of your research please cite the paper.

The low-power functionality implements a staggered powerdown similar to that described in "Optimized Active and Power-Down Mode Refresh Control in 3D-DRAMs" by Jung et al, VLSI-SoC, 2014.

Definition at line 96 of file dram_ctrl.hh.

|

private |

Bus state used to control the read/write switching and drive the scheduling of the next request.

| Enumerator | |

|---|---|

| READ | |

| WRITE | |

Definition at line 146 of file dram_ctrl.hh.

|

private |

The power state captures the different operational states of the DRAM and interacts with the bus read/write state machine, and the refresh state machine.

PWR_IDLE : The idle state in which all banks are closed From here can transition to: PWR_REF, PWR_ACT, PWR_PRE_PDN

PWR_REF : Auto-refresh state. Will transition when refresh is complete based on power state prior to PWR_REF From here can transition to: PWR_IDLE, PWR_PRE_PDN, PWR_SREF

PWR_SREF : Self-refresh state. Entered after refresh if previous state was PWR_PRE_PDN From here can transition to: PWR_IDLE

PWR_PRE_PDN : Precharge power down state From here can transition to: PWR_REF, PWR_IDLE

PWR_ACT : Activate state in which one or more banks are open From here can transition to: PWR_IDLE, PWR_ACT_PDN

PWR_ACT_PDN : Activate power down state From here can transition to: PWR_ACT

| Enumerator | |

|---|---|

| PWR_IDLE | |

| PWR_REF | |

| PWR_SREF | |

| PWR_PRE_PDN | |

| PWR_ACT | |

| PWR_ACT_PDN | |

Definition at line 233 of file dram_ctrl.hh.

|

private |

The refresh state is used to control the progress of the refresh scheduling.

When normal operation is in progress the refresh state is idle. Once tREFI has elasped, a refresh event is triggered to start the following STM transitions which are used to issue a refresh and return back to normal operation

REF_IDLE : IDLE state used during normal operation From here can transition to: REF_DRAIN

REF_SREF_EXIT : Exiting a self-refresh; refresh event scheduled after self-refresh exit completes From here can transition to: REF_DRAIN

REF_DRAIN : Drain state in which on going accesses complete. From here can transition to: REF_PD_EXIT

REF_PD_EXIT : Evaluate pwrState and issue wakeup if needed Next state dependent on whether banks are open From here can transition to: REF_PRE, REF_START

REF_PRE : Close (precharge) all open banks From here can transition to: REF_START

REF_START : Issue refresh command and update DRAMPower stats From here can transition to: REF_RUN

REF_RUN : Refresh running, waiting for tRFC to expire From here can transition to: REF_IDLE, REF_SREF_EXIT

| Enumerator | |

|---|---|

| REF_IDLE | |

| REF_DRAIN | |

| REF_PD_EXIT | |

| REF_SREF_EXIT | |

| REF_PRE | |

| REF_START | |

| REF_RUN | |

Definition at line 272 of file dram_ctrl.hh.

| DRAMCtrl::DRAMCtrl | ( | const DRAMCtrlParams * | p | ) |

Definition at line 60 of file dram_ctrl.cc.

References activationLimit, DRAMCtrl::Rank::actTicks, ArmISA::b, bankGroupArch, bankGroupsPerRank, DRAMCtrl::Rank::banks, banksPerRank, burstSize, ceilLog2(), columnsPerRowBuffer, deviceSize, devicesPerRank, DPRINTF, fatal, fatal_if(), ArmISA::i, isPowerOf2(), DRAMCtrl::Rank::rank, ranks, ranksPerChannel, READ, rowBufferSize, rowsPerBank, AbstractMemory::size(), tBURST, tCCD_L, tREFI, tRFC, tRP, tRRD, tRRD_L, ULL, and warn.

When a packet reaches its "readyTime" in the response Q, use the "access()" method in AbstractMemory to actually create the response packet, and send it back to the outside world requestor.

| pkt | The packet from the outside world |

| static_latency | Static latency to add before sending the packet |

Definition at line 892 of file dram_ctrl.cc.

References AbstractMemory::access(), curTick(), DPRINTF, Packet::getAddr(), Packet::headerDelay, Packet::isResponse(), Packet::needsResponse(), Packet::payloadDelay, pendingDelete, port, and QueuedSlavePort::schedTimingResp().

Referenced by addToReadQueue(), addToWriteQueue(), and processRespondEvent().

|

private |

Keep track of when row activations happen, in order to enforce the maximum number of activations in the activation window.

The method updates the time that the banks become available based on the current limits.

| rank_ref | Reference to the rank |

| bank_ref | Reference to the bank |

| act_tick | Time when the activation takes place |

| row | Index of the row |

Definition at line 929 of file dram_ctrl.cc.

References DRAMCtrl::Rank::activateEvent, activationLimit, DRAMCtrl::Rank::actTicks, DRAMCtrl::Bank::bank, DRAMCtrl::Bank::bankgr, bankGroupArch, DRAMCtrl::Rank::banks, banksPerRank, DRAMCtrl::Bank::bytesAccessed, DRAMCtrl::Rank::cmdList, DRAMCtrl::Bank::colAllowedAt, divCeil(), DPRINTF, ArmISA::i, ArmISA::j, DRAMCtrl::Bank::NO_ROW, DRAMCtrl::Rank::numBanksActive, DRAMCtrl::Bank::openRow, panic, DRAMCtrl::Bank::preAllowedAt, DRAMCtrl::Rank::rank, ranks, EventManager::reschedule(), DRAMCtrl::Bank::rowAccesses, EventManager::schedule(), tCK, timeStampOffset, tRAS, tRCD, tRRD, tRRD_L, and tXAW.

Referenced by doDRAMAccess().

|

private |

When a new read comes in, first check if the write q has a pending request to the same address. If not, decode the address to populate rank/bank/row, create one or mutliple "dram_pkt", and push them to the back of the read queue.

\ If this is the only read request in the system, schedule an event to start servicing it.

| pkt | The request packet from the outside world |

| pktCount | The number of DRAM bursts the pkt translate to. If pkt size is larger then one full burst, then pktCount is greater than one. |

Definition at line 421 of file dram_ctrl.cc.

References accessAndRespond(), addr, avgRdQLen, burstAlign(), DRAMCtrl::DRAMPacket::burstHelper, burstSize, DRAMCtrl::BurstHelper::burstsServiced, bytesReadWrQ, ceilLog2(), curTick(), decodeAddr(), DPRINTF, frontendLatency, Packet::getAddr(), Packet::getSize(), isInWriteQueue, Packet::isWrite(), nextReqEvent, MipsISA::p, DRAMCtrl::DRAMPacket::rankRef, rdQLenPdf, readBursts, DRAMCtrl::Rank::readEntries, readPktSize, readQueue, readQueueFull(), respQueue, EventManager::schedule(), Event::scheduled(), servicedByWrQ, AbstractMemory::size(), and writeQueue.

Referenced by recvTimingReq().

|

private |

Decode the incoming pkt, create a dram_pkt and push to the back of the write queue.

the write q length is more than the threshold specified by the user, ie the queue is beginning to get full, stop reads, and start draining writes.

| pkt | The request packet from the outside world |

| pktCount | The number of DRAM bursts the pkt translate to. If pkt size is larger then one full burst, then pktCount is greater than one. |

Definition at line 517 of file dram_ctrl.cc.

References accessAndRespond(), addr, avgWrQLen, burstAlign(), burstSize, ceilLog2(), curTick(), decodeAddr(), DPRINTF, frontendLatency, Packet::getAddr(), Packet::getSize(), isInWriteQueue, Packet::isWrite(), mergedWrBursts, nextReqEvent, DRAMCtrl::DRAMPacket::rankRef, EventManager::schedule(), Event::scheduled(), AbstractMemory::size(), writeBufferSize, writeBursts, DRAMCtrl::Rank::writeEntries, writePktSize, writeQueue, and wrQLenPdf.

Referenced by recvTimingReq().

| bool DRAMCtrl::allRanksDrained | ( | ) | const |

Return true once refresh is complete for all ranks and there are no additional commands enqueued.

(only evaluated when draining) This will ensure that all banks are closed, power state is IDLE, and power stats have been updated

Definition at line 2668 of file dram_ctrl.cc.

References MipsISA::r, and ranks.

Referenced by drain(), processNextReqEvent(), and processRespondEvent().

Burst-align an address.

| addr | The potentially unaligned address |

Definition at line 853 of file dram_ctrl.hh.

References burstSize.

Referenced by addToReadQueue(), addToWriteQueue(), and processNextReqEvent().

|

private |

The memory schduler/arbiter - picks which request needs to go next, based on the specified policy such as FCFS or FR-FCFS and moves it to the head of the queue.

Prioritizes accesses to the same rank as previous burst unless controller is switching command type.

| queue | Queued requests to consider |

| extra_col_delay | Any extra delay due to a read/write switch |

Definition at line 755 of file dram_ctrl.cc.

References DPRINTF, ArmISA::i, memSchedPolicy, panic, DRAMCtrl::DRAMPacket::rank, ranks, and reorderQueue().

Referenced by processNextReqEvent().

|

private |

Address decoder to figure out physical mapping onto ranks, banks, and rows.

This function is called multiple times on the same system packet if the pakcet is larger than burst of the memory. The dramPktAddr is used for the offset within the packet.

| pkt | The packet from the outside world |

| dramPktAddr | The starting address of the DRAM packet |

| size | The size of the DRAM packet in bytes |

| isRead | Is the request for a read or a write to DRAM |

Definition at line 315 of file dram_ctrl.cc.

References addr, addrMapping, banksPerRank, burstSize, channels, columnsPerRowBuffer, columnsPerStripe, DPRINTF, DRAMCtrl::Bank::NO_ROW, panic, ranks, ranksPerChannel, and rowsPerBank.

Referenced by addToReadQueue(), and addToWriteQueue().

|

private |

Actually do the DRAM access - figure out the latency it will take to service the req based on bank state, channel state etc and then update those states to account for this request. Based on this, update the packet's "readyTime" and move it to the response q from where it will eventually go back to the outside world.

| pkt | The DRAM packet created from the outside world pkt |

Definition at line 1077 of file dram_ctrl.cc.

References DRAMCtrl::Bank::actAllowedAt, activateBank(), activeRank, DRAMCtrl::DRAMPacket::addr, DRAMCtrl::DRAMPacket::bank, DRAMCtrl::Bank::bankgr, bankGroupArch, DRAMCtrl::DRAMPacket::bankId, DRAMCtrl::DRAMPacket::bankRef, banksPerRank, burstSize, busBusyUntil, DRAMCtrl::Bank::bytesAccessed, bytesReadDRAM, bytesWritten, DRAMCtrl::Rank::cmdList, DRAMCtrl::Bank::colAllowedAt, curTick(), divCeil(), DPRINTF, DRAMCtrl::DRAMPacket::entryTime, ArmISA::i, DRAMCtrl::Rank::inLowPowerState, DRAMCtrl::DRAMPacket::isRead, ArmISA::j, maxAccessesPerRow, nextReqTime, DRAMCtrl::Bank::NO_ROW, DRAMCtrl::Bank::openRow, MipsISA::p, pageMgmt, perBankRdBursts, perBankWrBursts, DRAMCtrl::Bank::preAllowedAt, prechargeBank(), PWR_SREF, DRAMCtrl::Rank::pwrState, DRAMCtrl::DRAMPacket::rank, DRAMCtrl::DRAMPacket::rankRef, ranks, ranksPerChannel, readQueue, readRowHits, readsThisTime, DRAMCtrl::DRAMPacket::readyTime, DRAMCtrl::DRAMPacket::row, DRAMCtrl::Bank::rowAccesses, DRAMCtrl::Rank::scheduleWakeUpEvent(), tBURST, tCCD_L, tCK, tCL, tCS, timeStampOffset, totBusLat, totMemAccLat, totQLat, tRCD, tRP, tRTP, tWR, tXP, writeQueue, writeRowHits, and writesThisTime.

Referenced by processNextReqEvent().

|

overridevirtual |

Notify an object that it needs to drain its state.

If the object does not need further simulation to drain internal buffers, it returns DrainState::Drained and automatically switches to the Drained state. If the object needs more simulation, it returns DrainState::Draining and automatically enters the Draining state. Other return values are invalid.

Implements Drainable.

Definition at line 2634 of file dram_ctrl.cc.

References allRanksDrained(), curTick(), DPRINTF, Drained, Draining, nextReqEvent, PWR_SREF, MipsISA::r, ranks, readQueue, respQueue, EventManager::schedule(), Event::scheduled(), tXS, and writeQueue.

|

overridevirtual |

Resume execution after a successful drain.

Reimplemented from Drainable.

Definition at line 2681 of file dram_ctrl.cc.

References isTimingMode, System::isTimingMode(), MipsISA::r, ranks, startup(), and AbstractMemory::system().

|

overridevirtual |

Get a slave port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic base master port.

| if_name | Port name |

| idx | Index in the case of a VectorPort |

Reimplemented from MemObject.

Definition at line 2624 of file dram_ctrl.cc.

References MemObject::getSlavePort(), and port.

|

overridevirtual |

Initialise this memory.

Reimplemented from AbstractMemory.

Definition at line 200 of file dram_ctrl.cc.

References addrMapping, channels, columnsPerRowBuffer, columnsPerStripe, fatal, AddrRange::granularity(), AbstractMemory::init(), AddrRange::interleaved(), BaseSlavePort::isConnected(), SimObject::name(), port, AbstractMemory::range, rowBufferSize, SlavePort::sendRangeChange(), AddrRange::stripes(), and AbstractMemory::system().

|

private |

Find which are the earliest banks ready to issue an activate for the enqueued requests.

Assumes maximum of 64 banks per DIMM Also checks if the bank is already prepped.

| queue | Queued requests to consider |

| time | of seamless burst command |

Definition at line 1547 of file dram_ctrl.cc.

References banksPerRank, curTick(), ArmISA::i, ArmISA::j, MaxTick, DRAMCtrl::Bank::NO_ROW, MipsISA::p, ranks, ranksPerChannel, replaceBits(), tRCD, and tRP.

Referenced by reorderQueue().

|

private |

Precharge a given bank and also update when the precharge is done.

This will also deal with any stats related to the accesses to the open page.

| rank_ref | The rank to precharge |

| bank_ref | The bank to precharge |

| pre_at | Time when the precharge takes place |

| trace | Is this an auto precharge then do not add to trace |

Definition at line 1029 of file dram_ctrl.cc.

References DRAMCtrl::Bank::actAllowedAt, DRAMCtrl::Bank::bank, DRAMCtrl::Bank::bytesAccessed, bytesPerActivate, DRAMCtrl::Rank::cmdList, divCeil(), DPRINTF, DRAMCtrl::Bank::NO_ROW, DRAMCtrl::Rank::numBanksActive, DRAMCtrl::Bank::openRow, DRAMCtrl::Rank::outstandingEvents, DRAMCtrl::Bank::preAllowedAt, DRAMCtrl::Rank::prechargeEvent, DRAMCtrl::Rank::rank, EventManager::reschedule(), Stats::DistBase< Derived, Stor >::sample(), EventManager::schedule(), tCK, timeStampOffset, and tRP.

Referenced by doDRAMAccess().

|

private |

Used for debugging to observe the contents of the queues.

Definition at line 584 of file dram_ctrl.cc.

References DPRINTF, ArmISA::i, readQueue, respQueue, and writeQueue.

|

private |

Bunch of things requires to setup "events" in gem5 When event "respondEvent" occurs for example, the method processRespondEvent is called; no parameters are allowed in these methods.

Definition at line 1290 of file dram_ctrl.cc.

References activeRank, DRAMCtrl::DRAMPacket::addr, allRanksDrained(), burstAlign(), burstSize, busBusyUntil, busState, busStateNext, chooseNext(), curTick(), doDRAMAccess(), DPRINTF, Draining, Drainable::drainState(), DRAMCtrl::Rank::isAvailable(), isInWriteQueue, minWritesPerSwitch, nextReqEvent, nextReqTime, DRAMCtrl::Rank::outstandingEvents, port, PWR_SREF, MipsISA::r, DRAMCtrl::DRAMPacket::rank, DRAMCtrl::DRAMPacket::rankRef, ranks, ranksPerChannel, rdPerTurnAround, READ, readQueue, readsThisTime, DRAMCtrl::DRAMPacket::readyTime, EventManager::reschedule(), respondEvent, respQueue, retryWrReq, Stats::DistBase< Derived, Stor >::sample(), EventManager::schedule(), Event::scheduled(), SlavePort::sendRetryReq(), Drainable::signalDrainDone(), DRAMCtrl::DRAMPacket::size, tCL, tCS, tRTW, tWTR, tXS, WRITE, writeBufferSize, DRAMCtrl::Rank::writeDoneEvent, DRAMCtrl::Rank::writeEntries, writeHighThreshold, writeLowThreshold, writeQueue, writesThisTime, and wrPerTurnAround.

|

private |

Definition at line 661 of file dram_ctrl.cc.

References accessAndRespond(), DRAMCtrl::Rank::activateEvent, allRanksDrained(), backendLatency, DRAMCtrl::BurstHelper::burstCount, DRAMCtrl::DRAMPacket::burstHelper, DRAMCtrl::BurstHelper::burstsServiced, curTick(), DPRINTF, Draining, Drainable::drainState(), frontendLatency, DRAMCtrl::Rank::lowPowerEntryReady(), DRAMCtrl::Rank::outstandingEvents, DRAMCtrl::DRAMPacket::pkt, port, DRAMCtrl::Rank::powerDownSleep(), DRAMCtrl::Rank::prechargeEvent, PWR_ACT_PDN, PWR_IDLE, PWR_PRE_PDN, PWR_SREF, DRAMCtrl::Rank::pwrState, DRAMCtrl::DRAMPacket::rank, DRAMCtrl::DRAMPacket::rankRef, DRAMCtrl::Rank::readEntries, readQueue, REF_IDLE, DRAMCtrl::Rank::refreshState, respondEvent, respQueue, retryRdReq, EventManager::schedule(), Event::scheduled(), SlavePort::sendRetryReq(), Drainable::signalDrainDone(), and writeQueue.

|

private |

Check if the read queue has room for more entries.

| pktCount | The number of entries needed in the read queue |

Definition at line 296 of file dram_ctrl.cc.

References DPRINTF, readBufferSize, readQueue, and respQueue.

Referenced by addToReadQueue(), and recvTimingReq().

Definition at line 276 of file dram_ctrl.cc.

References AbstractMemory::access(), Packet::cacheResponding(), Packet::cmdString(), DPRINTF, Packet::getAddr(), Packet::hasData(), panic_if(), tCL, tRCD, and tRP.

|

protected |

Definition at line 2617 of file dram_ctrl.cc.

References AbstractMemory::functionalAccess().

|

protected |

Definition at line 600 of file dram_ctrl.cc.

References addToReadQueue(), addToWriteQueue(), burstSize, bytesReadSys, bytesWrittenSys, Packet::cacheResponding(), Packet::cmdString(), curTick(), divCeil(), DPRINTF, Packet::getAddr(), Packet::getSize(), Packet::isRead(), Packet::isWrite(), numRdRetry, numWrRetry, ArmISA::offset, panic_if(), prevArrival, readQueueFull(), readReqs, retryRdReq, retryWrReq, AbstractMemory::size(), totGap, writeQueueFull(), and writeReqs.

|

overridevirtual |

Register Statistics.

Reimplemented from AbstractMemory.

Definition at line 2358 of file dram_ctrl.cc.

References avgBusLat, avgGap, avgMemAccLat, avgQLat, avgRdBW, avgRdBWSys, avgRdQLen, avgWrBW, avgWrBWSys, avgWrQLen, banksPerRank, burstSize, busUtil, busUtilRead, busUtilWrite, bytesPerActivate, bytesReadDRAM, bytesReadSys, bytesReadWrQ, bytesWritten, bytesWrittenSys, ceilLog2(), Stats::DataWrap< Derived, InfoProxyType >::desc(), Stats::DataWrap< Derived, InfoProxyType >::flags(), SimClock::Frequency, Stats::VectorBase< Derived, Stor >::init(), Stats::Histogram::init(), maxAccessesPerRow, mergedWrBursts, SimObject::name(), Stats::DataWrap< Derived, InfoProxyType >::name(), neitherReadNorWrite, Stats::nozero, numRdRetry, numWrRetry, pageHitRate, peakBW, perBankRdBursts, perBankWrBursts, Stats::DataWrap< Derived, InfoProxyType >::precision(), MipsISA::r, ranks, ranksPerChannel, rdPerTurnAround, rdQLenPdf, readBufferSize, readBursts, readPktSize, readReqs, readRowHitRate, readRowHits, AbstractMemory::regStats(), servicedByWrQ, simSeconds, tBURST, totBusLat, totGap, totMemAccLat, totQLat, writeBufferSize, writeBursts, writePktSize, writeReqs, writeRowHitRate, writeRowHits, wrPerTurnAround, and wrQLenPdf.

|

private |

For FR-FCFS policy reorder the read/write queue depending on row buffer hits and earliest bursts available in DRAM.

| queue | Queued requests to consider |

| extra_col_delay | Any extra delay due to a read/write switch |

Definition at line 796 of file dram_ctrl.cc.

References DRAMCtrl::DRAMPacket::bankId, DRAMCtrl::DRAMPacket::bankRef, bits(), busBusyUntil, DRAMCtrl::Bank::colAllowedAt, curTick(), DPRINTF, ArmISA::i, DRAMCtrl::Rank::isAvailable(), minBankPrep(), DRAMCtrl::Bank::openRow, DRAMCtrl::DRAMPacket::rankRef, DRAMCtrl::DRAMPacket::row, and tCL.

Referenced by chooseNext().

|

inlinestaticprivate |

Function for sorting Command structures based on timeStamp.

Definition at line 1072 of file dram_ctrl.hh.

References DRAMCtrl::Command::timeStamp.

Referenced by DRAMCtrl::Rank::flushCmdList().

|

overridevirtual |

startup() is the final initialization call before simulation.

All state is initialized (including unserialized state, if any, such as the curTick() value), so this is the appropriate place to schedule initial event(s) for objects that need them.

Reimplemented from SimObject.

Definition at line 252 of file dram_ctrl.cc.

References busBusyUntil, curTick(), divCeil(), isTimingMode, System::isTimingMode(), MipsISA::r, ranks, AbstractMemory::system(), tCK, tCL, timeStampOffset, tRCD, tREFI, and tRP.

Referenced by drainResume().

|

private |

This function increments the energy when called.

If stats are dumped periodically, note accumulated energy values will appear in the stats (even if the stats are reset). This is a result of the energy values coming from DRAMPower, and there is currently no support for resetting the state.

| rank | Currrent rank |

Referenced by DRAMCtrl::Rank::computeStats(), DRAMCtrl::Rank::processRefreshEvent(), and DRAMCtrl::Rank::suspend().

|

private |

Check if the write queue has room for more entries.

| pktCount | The number of entries needed in the write queue |

Definition at line 307 of file dram_ctrl.cc.

References DPRINTF, writeBufferSize, and writeQueue.

Referenced by recvTimingReq().

|

private |

Definition at line 937 of file dram_ctrl.hh.

Referenced by activateBank(), and DRAMCtrl().

|

private |

Definition at line 1043 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and processNextReqEvent().

|

private |

Definition at line 944 of file dram_ctrl.hh.

Referenced by decodeAddr(), and init().

|

private |

Definition at line 1015 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1037 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1016 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1014 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1019 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1021 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1029 of file dram_ctrl.hh.

Referenced by addToReadQueue(), and regStats().

|

private |

Definition at line 1020 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1022 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1030 of file dram_ctrl.hh.

Referenced by addToWriteQueue(), and regStats().

|

private |

Pipeline latency of the backend and PHY.

Along with the frontend contribution, this latency is added to reads serviced by the DRAM.

Definition at line 965 of file dram_ctrl.hh.

Referenced by processRespondEvent().

|

private |

Definition at line 902 of file dram_ctrl.hh.

Referenced by activateBank(), doDRAMAccess(), and DRAMCtrl().

|

private |

Definition at line 901 of file dram_ctrl.hh.

Referenced by DRAMCtrl().

|

private |

Definition at line 903 of file dram_ctrl.hh.

Referenced by activateBank(), decodeAddr(), doDRAMAccess(), DRAMCtrl(), minBankPrep(), and regStats().

|

private |

Definition at line 893 of file dram_ctrl.hh.

|

private |

Definition at line 896 of file dram_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), burstAlign(), decodeAddr(), doDRAMAccess(), DRAMCtrl(), processNextReqEvent(), recvTimingReq(), and regStats().

|

private |

Till when has the main data bus been spoken for already?

Definition at line 970 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), processNextReqEvent(), reorderQueue(), and startup().

|

private |

Definition at line 151 of file dram_ctrl.hh.

Referenced by processNextReqEvent().

|

private |

Definition at line 154 of file dram_ctrl.hh.

Referenced by DRAMCtrl::Rank::forceSelfRefreshExit(), and processNextReqEvent().

|

private |

Definition at line 1024 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1025 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1026 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1004 of file dram_ctrl.hh.

Referenced by prechargeBank(), and regStats().

|

private |

Definition at line 987 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 990 of file dram_ctrl.hh.

Referenced by recvTimingReq(), and regStats().

|

private |

Definition at line 988 of file dram_ctrl.hh.

Referenced by addToReadQueue(), and regStats().

|

private |

Definition at line 989 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 991 of file dram_ctrl.hh.

Referenced by recvTimingReq(), and regStats().

|

private |

Definition at line 904 of file dram_ctrl.hh.

Referenced by decodeAddr(), and init().

|

private |

Definition at line 898 of file dram_ctrl.hh.

Referenced by decodeAddr(), DRAMCtrl(), and init().

|

private |

Definition at line 899 of file dram_ctrl.hh.

Referenced by decodeAddr(), and init().

|

private |

Definition at line 892 of file dram_ctrl.hh.

|

private |

Definition at line 894 of file dram_ctrl.hh.

|

private |

The following are basic design parameters of the memory controller, and are initialized based on parameter values.

The rowsPerBank is determined based on the capacity, number of ranks and banks, the burst size, and the row buffer size.

Definition at line 891 of file dram_ctrl.hh.

Referenced by DRAMCtrl().

|

private |

Definition at line 895 of file dram_ctrl.hh.

Referenced by DRAMCtrl().

|

private |

Pipeline latency of the controller frontend.

The frontend contribution is added to writes (that complete when they are in the write buffer) and reads that are serviced the write buffer.

Definition at line 958 of file dram_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), and processRespondEvent().

|

private |

To avoid iterating over the write queue to check for overlapping transactions, maintain a set of burst addresses that are currently queued.

Since we merge writes to the same location we never have more than one address to the same burst address.

Definition at line 868 of file dram_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), and processNextReqEvent().

|

private |

Remeber if the memory system is in timing mode.

Definition at line 134 of file dram_ctrl.hh.

Referenced by drainResume(), and startup().

|

private |

Max column accesses (read and write) per row, before forefully closing it.

Definition at line 951 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Memory controller configuration initialized based on parameter values.

Definition at line 943 of file dram_ctrl.hh.

Referenced by chooseNext().

|

private |

Definition at line 993 of file dram_ctrl.hh.

Referenced by addToWriteQueue(), and regStats().

|

private |

Definition at line 910 of file dram_ctrl.hh.

Referenced by processNextReqEvent().

|

private |

Definition at line 994 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 688 of file dram_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), drain(), and processNextReqEvent().

|

private |

The soonest you have to start thinking about the next request is the longest access time that can occur before busBusyUntil.

Assuming you need to precharge, open a new row, and access, it is tRP + tRCD + tCL.

Definition at line 980 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and processNextReqEvent().

|

private |

Definition at line 997 of file dram_ctrl.hh.

Referenced by recvTimingReq(), and regStats().

|

private |

Definition at line 998 of file dram_ctrl.hh.

Referenced by recvTimingReq(), and regStats().

|

private |

Definition at line 1040 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 945 of file dram_ctrl.hh.

Referenced by doDRAMAccess().

|

private |

Definition at line 1023 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call.

Definition at line 1052 of file dram_ctrl.hh.

Referenced by accessAndRespond().

|

private |

Definition at line 995 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 996 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Our incoming port, for a multi-ported controller add a crossbar in front of it.

Definition at line 129 of file dram_ctrl.hh.

Referenced by accessAndRespond(), getSlavePort(), init(), processNextReqEvent(), and processRespondEvent().

|

private |

Definition at line 972 of file dram_ctrl.hh.

Referenced by recvTimingReq().

|

private |

Vector of ranks.

Definition at line 883 of file dram_ctrl.hh.

Referenced by activateBank(), allRanksDrained(), chooseNext(), decodeAddr(), doDRAMAccess(), drain(), drainResume(), DRAMCtrl(), minBankPrep(), processNextReqEvent(), regStats(), and startup().

|

private |

Definition at line 900 of file dram_ctrl.hh.

Referenced by decodeAddr(), doDRAMAccess(), DRAMCtrl(), minBankPrep(), processNextReqEvent(), and regStats().

|

private |

Definition at line 1005 of file dram_ctrl.hh.

Referenced by processNextReqEvent(), and regStats().

|

private |

Definition at line 1002 of file dram_ctrl.hh.

Referenced by addToReadQueue(), and regStats().

|

private |

Definition at line 906 of file dram_ctrl.hh.

Referenced by readQueueFull(), and regStats().

|

private |

Definition at line 985 of file dram_ctrl.hh.

Referenced by addToReadQueue(), and regStats().

|

private |

Definition at line 1000 of file dram_ctrl.hh.

Referenced by addToReadQueue(), and regStats().

|

private |

The controller's main read and write queues.

Definition at line 858 of file dram_ctrl.hh.

Referenced by addToReadQueue(), doDRAMAccess(), drain(), printQs(), processNextReqEvent(), processRespondEvent(), and readQueueFull().

|

private |

Definition at line 983 of file dram_ctrl.hh.

Referenced by recvTimingReq(), and regStats().

|

private |

Definition at line 1035 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1033 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 912 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and processNextReqEvent().

|

private |

Definition at line 691 of file dram_ctrl.hh.

Referenced by processNextReqEvent(), and processRespondEvent().

|

private |

Response queue where read packets wait after we're done working with them, but it's not time to send the response yet.

The responses are stored seperately mostly to keep the code clean and help with events scheduling. For all logical purposes such as sizing the read queue, this and the main read queue need to be added together.

Definition at line 878 of file dram_ctrl.hh.

Referenced by addToReadQueue(), drain(), printQs(), processNextReqEvent(), processRespondEvent(), and readQueueFull().

|

private |

Remember if we have to retry a request when available.

Definition at line 139 of file dram_ctrl.hh.

Referenced by processRespondEvent(), and recvTimingReq().

|

private |

Definition at line 140 of file dram_ctrl.hh.

Referenced by processNextReqEvent(), and recvTimingReq().

|

private |

Definition at line 897 of file dram_ctrl.hh.

Referenced by DRAMCtrl(), and init().

|

private |

Definition at line 905 of file dram_ctrl.hh.

Referenced by decodeAddr(), and DRAMCtrl().

|

private |

Definition at line 992 of file dram_ctrl.hh.

Referenced by addToReadQueue(), and regStats().

|

private |

Definition at line 922 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), DRAMCtrl(), and regStats().

|

private |

Definition at line 923 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and DRAMCtrl().

|

private |

Basic memory timing parameters initialized based on parameter values.

Definition at line 918 of file dram_ctrl.hh.

Referenced by activateBank(), doDRAMAccess(), prechargeBank(), and startup().

|

private |

Definition at line 925 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), processNextReqEvent(), recvAtomic(), reorderQueue(), and startup().

|

private |

Definition at line 921 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and processNextReqEvent().

|

private |

Definition at line 1046 of file dram_ctrl.hh.

Referenced by activateBank(), doDRAMAccess(), prechargeBank(), and startup().

|

private |

Definition at line 1011 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 999 of file dram_ctrl.hh.

Referenced by recvTimingReq(), and regStats().

|

private |

Definition at line 1010 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 1009 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 927 of file dram_ctrl.hh.

Referenced by activateBank().

|

private |

Definition at line 924 of file dram_ctrl.hh.

Referenced by activateBank(), doDRAMAccess(), minBankPrep(), recvAtomic(), and startup().

|

private |

Definition at line 931 of file dram_ctrl.hh.

Referenced by DRAMCtrl(), and startup().

|

private |

Definition at line 930 of file dram_ctrl.hh.

Referenced by DRAMCtrl().

|

private |

Definition at line 926 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), DRAMCtrl(), minBankPrep(), prechargeBank(), recvAtomic(), and startup().

|

private |

Definition at line 932 of file dram_ctrl.hh.

Referenced by activateBank(), and DRAMCtrl().

|

private |

Definition at line 933 of file dram_ctrl.hh.

Referenced by activateBank(), and DRAMCtrl().

|

private |

Definition at line 929 of file dram_ctrl.hh.

Referenced by doDRAMAccess().

|

private |

Definition at line 920 of file dram_ctrl.hh.

Referenced by processNextReqEvent().

|

private |

Definition at line 928 of file dram_ctrl.hh.

Referenced by doDRAMAccess().

|

private |

Definition at line 919 of file dram_ctrl.hh.

Referenced by processNextReqEvent().

|

private |

Definition at line 934 of file dram_ctrl.hh.

Referenced by activateBank().

|

private |

Definition at line 935 of file dram_ctrl.hh.

Referenced by doDRAMAccess().

|

private |

Definition at line 936 of file dram_ctrl.hh.

Referenced by drain(), and processNextReqEvent().

|

private |

Definition at line 907 of file dram_ctrl.hh.

Referenced by addToWriteQueue(), processNextReqEvent(), regStats(), and writeQueueFull().

|

private |

Definition at line 986 of file dram_ctrl.hh.

Referenced by addToWriteQueue(), and regStats().

|

private |

Definition at line 908 of file dram_ctrl.hh.

Referenced by processNextReqEvent().

|

private |

Definition at line 909 of file dram_ctrl.hh.

Referenced by processNextReqEvent().

|

private |

Definition at line 1001 of file dram_ctrl.hh.

Referenced by addToWriteQueue(), and regStats().

|

private |

Definition at line 859 of file dram_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), doDRAMAccess(), drain(), printQs(), processNextReqEvent(), processRespondEvent(), and writeQueueFull().

|

private |

Definition at line 984 of file dram_ctrl.hh.

Referenced by recvTimingReq(), and regStats().

|

private |

Definition at line 1036 of file dram_ctrl.hh.

Referenced by regStats().

|

private |

Definition at line 1034 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and regStats().

|

private |

Definition at line 911 of file dram_ctrl.hh.

Referenced by doDRAMAccess(), and processNextReqEvent().

|

private |

Definition at line 1006 of file dram_ctrl.hh.

Referenced by processNextReqEvent(), and regStats().

|

private |

Definition at line 1003 of file dram_ctrl.hh.

Referenced by addToWriteQueue(), and regStats().