|

gem5

|

|

gem5

|

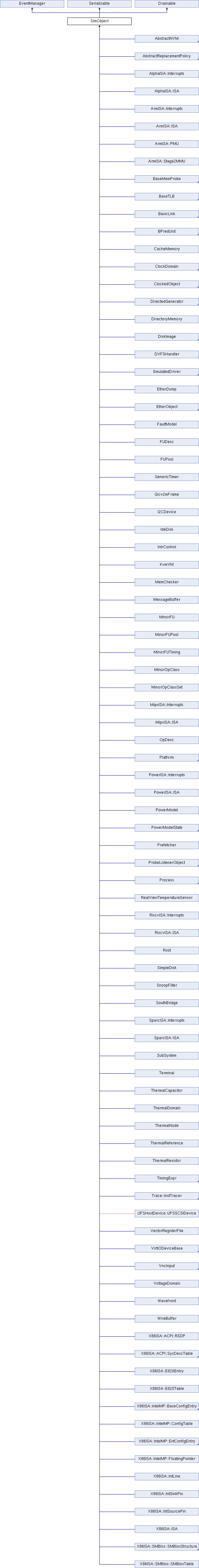

Abstract superclass for simulation objects. More...

#include <sim_object.hh>

Public Types | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| const Params * | params () const |

| SimObject (const Params *_params) | |

| virtual | ~SimObject () |

| virtual const std::string | name () const |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. More... | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. More... | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. More... | |

| virtual void | regStats () |

| Register statistics for this object. More... | |

| virtual void | resetStats () |

| Reset statistics associated with this object. More... | |

| virtual void | regProbePoints () |

| Register probe points for this object. More... | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. More... | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. More... | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. More... | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. More... | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. More... | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

Public Member Functions inherited from EventManager Public Member Functions inherited from EventManager | |

| EventManager (EventManager &em) | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick)-1) |

| void | setCurTick (Tick newVal) |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Member Functions inherited from Drainable Public Member Functions inherited from Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. More... | |

| virtual void | notifyFork () |

| Notify a child process of a fork. More... | |

Static Public Member Functions | |

| static void | serializeAll (CheckpointOut &cp) |

| Serialize all SimObjects in the system. More... | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. More... | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Get the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| static void | unserializeGlobals (CheckpointIn &cp) |

Protected Attributes | |

| const SimObjectParams * | _params |

| Cached copy of the object parameters. More... | |

Protected Attributes inherited from EventManager Protected Attributes inherited from EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. More... | |

Private Types | |

| typedef std::vector< SimObject * > | SimObjectList |

Private Attributes | |

| ProbeManager * | probeManager |

| Manager coordinates hooking up probe points with listeners. More... | |

Static Private Attributes | |

| static SimObjectList | simObjectList |

| List of all instantiated simulation objects. More... | |

Additional Inherited Members | |

Static Public Attributes inherited from Serializable Static Public Attributes inherited from Serializable | |

| static int | ckptCount = 0 |

| static int | ckptMaxCount = 0 |

| static int | ckptPrevCount = -1 |

Protected Member Functions inherited from Drainable Protected Member Functions inherited from Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. More... | |

| void | signalDrainDone () const |

| Signal that an object is drained. More... | |

Abstract superclass for simulation objects.

Represents things that correspond to physical components and can be specified via the config file (CPUs, caches, etc.).

SimObject initialization is controlled by the instantiate method in src/python/m5/simulate.py. There are slightly different initialization paths when starting the simulation afresh and when loading from a checkpoint. After instantiation and connecting ports, simulate.py initializes the object using the following call sequence:

Definition at line 94 of file sim_object.hh.

| typedef SimObjectParams SimObject::Params |

Definition at line 110 of file sim_object.hh.

|

private |

Definition at line 97 of file sim_object.hh.

| SimObject::SimObject | ( | const Params * | _params | ) |

Definition at line 58 of file sim_object.cc.

References probeManager, and simObjectList.

|

virtual |

Definition at line 68 of file sim_object.cc.

References probeManager.

|

inlineoverridevirtual |

Provide a default implementation of the drain interface for objects that don't need draining.

Implements Drainable.

Definition at line 184 of file sim_object.hh.

References Drained.

|

static |

Find the SimObject with the given name and return a pointer to it.

Primarily used for interactive debugging. Argument is char* rather than std::string to make it callable from gdb.

Definition at line 179 of file sim_object.cc.

References ArmISA::i, name(), and simObjectList.

Referenced by LdsState::releaseSpace(), and LdsState::reserveSpace().

| ProbeManager * SimObject::getProbeManager | ( | ) |

Get the probe manager for this object.

Definition at line 131 of file sim_object.cc.

References probeManager.

Referenced by ArmISA::PMU::EventType::create(), BPredUnit::pmuProbePoint(), CommMonitor::regProbePoints(), PowerModel::regProbePoints(), ArmISA::TLB::regProbePoints(), and ThermalDomain::setSubSystem().

|

virtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented in DRAMCtrl, ArmISA::TableWalker, IGbE, BaseCache, BaseXBar, CoherentXBar, Bridge, SerialLink, Wavefront, ComputeUnit, DistEtherLink, TrafficGen, X86ISA::Interrupts, ArmISA::TLB, AbstractMemory, DRAMSim2, SimpleMemory, DmaDevice, Shader, RubyPort, EnergyCtrl, ExternalSlave, ExternalMaster, PioDevice, System, RubyTester, X86ISA::I82094AA, Tsunami, SimPoint, CommMonitor, MemCheckerMonitor, GarnetExtLink, RubyDirectedTester, RubyPortProxy, AddrMapper, Router, Network, AbstractController, Switch, GarnetSyntheticTraffic, WireBuffer, DMASequencer, Pc, GarnetNetwork, NetworkInterface, NoMaliGpu, CacheMemory, EtherDump, GarnetIntLink, BasicLink, SimpleNetwork, DirectoryMemory, and BasicRouter.

Definition at line 74 of file sim_object.cc.

Referenced by CxxConfigManager::instantiate().

|

virtual |

initState() is called on each SimObject when not restoring from a checkpoint.

This provides a hook for state initializations that are only required for a "cold start".

Reimplemented in System, GenericArmSystem, TrafficGen, X86ISA::I386Process, ArmSystem, Sparc64Process, LinuxAlphaSystem, X86ISA::X86_64Process, Root, Sparc32Process, X86System, ArmLinuxProcess64, LinuxArmSystem, ArmProcess64, ArmFreebsdProcess64, FreebsdArmSystem, ArmLinuxProcess32, ArmProcess32, Process, ArmFreebsdProcess32, LinuxX86System, AlphaSystem, SparcProcess, RiscvProcess, SparcSystem, PowerProcess, MipsProcess, AlphaProcess, and PowerLinuxProcess.

Definition at line 92 of file sim_object.cc.

Referenced by CxxConfigManager::initState().

|

virtual |

loadState() is called on each SimObject when restoring from a checkpoint.

The default implementation simply calls unserialize() if there is a corresponding section in the checkpoint. However, objects can override loadState() to get other behaviors, e.g., doing other programmed initializations after unserialize(), or complaining if no checkpoint section is found.

| cp | Checkpoint to restore the state from. |

Reimplemented in MuxingKvmGic, Root, and AlphaProcess.

Definition at line 79 of file sim_object.cc.

References DPRINTF, name(), CheckpointIn::sectionExists(), and Serializable::unserializeSection().

Referenced by AlphaProcess::loadState(), Root::loadState(), and MuxingKvmGic::loadState().

|

inlinevirtual |

Invalidate the contents of memory buffers.

When the switching to hardware virtualized CPU models, we need to make sure that we don't have any cached state in the system that might become stale when we return. This method is used to flush all such state back to main memory.

This does not cause any dirty state to be written back to memory.

Reimplemented in Cache, BaseCache, and BaseTLB.

Definition at line 207 of file sim_object.hh.

|

inlinevirtual |

Write back dirty buffers to memory using functional writes.

After returning, an object implementing this method should have written all its dirty data back to memory. This method is typically used to prepare a system with caches for checkpointing.

Reimplemented in Cache, BaseCache, and RubySystem.

Definition at line 194 of file sim_object.hh.

|

inlinevirtual |

Reimplemented in Pl111, ElasticTrace, and SimpleTrace.

Definition at line 117 of file sim_object.hh.

References params().

Referenced by Terminal::accept(), VncServer::accept(), Cache::access(), ArmISA::PMU::addEventProbe(), ProbeManager::addListener(), CxxConfigManager::bindMasterPort(), CxxConfigManager::bindPort(), NetworkInterface::calculateVC(), DVFSHandler::clkPeriodAtPerfLevel(), SrcClockDomain::clockPeriod(), RealViewOsc::clockPeriod(), CoherentXBar::CoherentXBar(), CommMonitor::CommMonitor(), MemTest::completeRequest(), connectPorts(), CpuLocalTimer::CpuLocalTimer(), DistEtherLink::DistEtherLink(), Pl111::dmaDone(), FUPool::dump(), DVFSHandler::DVFSHandler(), IdeController::EndBitUnion(), MessageBuffer::enqueue(), EtherLink::EtherLink(), EtherSwitch::EtherSwitch(), X86ISA::GpuTLB::exitCallback(), find(), BaseXBar::findPort(), Cache::functionalAccess(), GarnetSyntheticTraffic::GarnetSyntheticTraffic(), System::getMasterId(), MemObject::getMasterPort(), ComputeUnit::getMasterPort(), MemObject::getSlavePort(), GpuDispatcher::GpuDispatcher(), X86ISA::GpuTLB::GpuTLB(), Cache::handleFill(), Cache::handleSnoop(), IGbE::IGbE(), FetchStage::init(), LocalMemPipeline::init(), ScheduleStage::init(), GlobalMemPipeline::init(), ScoreboardCheckStage::init(), ExecStage::init(), System::init(), PioDevice::init(), ExternalMaster::init(), ExternalSlave::init(), DmaDevice::init(), DRAMSim2::init(), TrafficGen::init(), CoherentXBar::init(), BaseCache::init(), DRAMCtrl::init(), Process::initState(), LinuxArmSystem::LinuxArmSystem(), Terminal::listen(), VncServer::listen(), loadState(), MathExprPowerModel::MathExprPowerModel(), MemTraceProbe::MemTraceProbe(), SimpleTrace::name(), CopyEngine::CopyEngineChannel::name(), ElasticTrace::name(), VirtIOConsole::TermRecvQueue::name(), BaseXBar::Layer< MasterPort, SlavePort >::name(), X86ISA::Walker::WalkerState::name(), VirtIOConsole::TermTransQueue::name(), VirtIO9PBase::FSQueue::name(), VirtIOBlock::RequestQueue::name(), BaseRemoteGDB::name(), DRAMCtrl::Rank::name(), ArmISA::TableWalker::WalkerState::name(), NoncoherentXBar::NoncoherentXBar(), TrafficGen::noProgress(), MemTest::noRequest(), MemTest::noResponse(), TrafficGen::parseConfig(), VoltageDomain::perfLevel(), SrcClockDomain::perfLevel(), BasicRouter::print(), SimpleExtLink::print(), BasicLink::print(), GarnetIntLink::print(), SimpleIntLink::print(), GarnetExtLink::print(), Prefetcher::print(), MessageBuffer::print(), CacheMemory::print(), System::printSystems(), Linux::DebugPrintkEvent::process(), HDLcd::pxlFrameDone(), IsaFake::read(), PciDevice::readConfig(), IdeDisk::readDisk(), CacheMemory::recordCacheContents(), NoncoherentXBar::recvAtomic(), CoherentXBar::recvAtomic(), CoherentXBar::recvAtomicSnoop(), NoncoherentXBar::recvFunctional(), SimpleMemory::recvFunctional(), SerialLink::SerialLinkSlavePort::recvFunctional(), DRAMSim2::recvFunctional(), Bridge::BridgeSlavePort::recvFunctional(), CoherentXBar::recvFunctional(), CoherentXBar::recvFunctionalSnoop(), EtherSwitch::Interface::recvPacket(), BaseXBar::recvRangeChange(), MemCheckerMonitor::recvTimingResp(), AddrMapper::recvTimingResp(), Cache::recvTimingResp(), CoherentXBar::recvTimingSnoopReq(), StackDistProbe::regStats(), SimpleNetwork::regStats(), MemFootprintProbe::regStats(), Sequencer::regStats(), EtherDevice::regStats(), Switch::regStats(), MemTest::regStats(), BPredUnit::regStats(), CommMonitor::regStats(), AbstractController::regStats(), PowerModelState::regStats(), AlphaISA::TLB::regStats(), RubySystem::regStats(), ThermalDomain::regStats(), HDLcd::regStats(), Router::regStats(), GarnetNetwork::regStats(), GPUCoalescer::regStats(), RiscvISA::TLB::regStats(), Prefetcher::regStats(), MipsISA::TLB::regStats(), Process::regStats(), ClockDomain::regStats(), MessageBuffer::regStats(), QueuedPrefetcher::regStats(), CacheMemory::regStats(), VoltageDomain::regStats(), PowerModel::regStats(), BasePrefetcher::regStats(), TLBCoalescer::regStats(), FlashDevice::regStats(), BaseTags::regStats(), FALRU::regStats(), BaseXBar::Layer< SrcType, DstType >::regStats(), PowerISA::TLB::regStats(), SnoopFilter::regStats(), CopyEngine::regStats(), X86ISA::GpuTLB::regStats(), TrafficGen::regStats(), ClockedObject::regStats(), IdeDisk::regStats(), Sinic::Device::regStats(), AbstractMemory::regStats(), Wavefront::regStats(), System::regStats(), ArmISA::TLB::regStats(), ComputeUnit::regStats(), CoherentXBar::regStats(), BaseCache::regStats(), BaseXBar::regStats(), DRAMCtrl::Rank::regStats(), ArmISA::TableWalker::regStats(), UFSHostDevice::regStats(), DRAMCtrl::regStats(), ProbeManager::removeListener(), TrafficGen::resolveFile(), RubyDirectedTester::RubyDirectedTester(), RubyPort::RubyPort(), RubyTester::RubyTester(), VoltageDomain::sanitiseVoltages(), RubySystem::serialize(), CowDiskImage::serialize(), serializeAll(), WireBuffer::setDescription(), ConditionRegisterState::setParent(), VecRegisterState::setParent(), LdsState::setParent(), ArmISA::TLB::setTestInterface(), SrcClockDomain::SrcClockDomain(), LinuxArmSystem::startup(), VoltageDomain::startup(), GarnetSyntheticTraffic::tick(), MemTest::tick(), TLBCoalescer::TLBCoalescer(), DrainManager::tryDrain(), RubyPort::trySendRetries(), TrafficGen::update(), DerivedClockDomain::updateClockPeriod(), ArmISA::PMU::updateCounter(), VncInput::VncInput(), VoltageDomain::voltage(), DVFSHandler::voltageAtPerfLevel(), VoltageDomain::VoltageDomain(), IsaFake::write(), PciDevice::writeConfig(), and IdeDisk::writeDisk().

|

inline |

Definition at line 111 of file sim_object.hh.

References _params.

Referenced by VirtIO9PSocket::connectSocket(), name(), RawDiskImage::notifyFork(), CowDiskImage::notifyFork(), BaseMemProbe::regProbeListeners(), StackDistProbe::regStats(), PowerModelState::regStats(), ThermalDomain::regStats(), ClockDomain::regStats(), VoltageDomain::regStats(), PowerModel::regStats(), VirtIO9PDiod::startDiod(), and MathExprPowerModel::startup().

|

virtual |

Register probe listeners for this object.

No probe listeners by default, so do nothing in base.

Reimplemented in ElasticTrace, SimPoint, BaseMemProbe, and SimpleTrace.

Definition at line 126 of file sim_object.cc.

Referenced by CxxConfigManager::instantiate().

|

virtual |

Register probe points for this object.

No probe points by default, so do nothing in base.

Reimplemented in ArmISA::TLB, PowerModel, CommMonitor, and BPredUnit.

Definition at line 118 of file sim_object.cc.

Referenced by CxxConfigManager::instantiate().

|

virtual |

Register statistics for this object.

Reimplemented in DRAMCtrl, UFSHostDevice, ArmISA::TableWalker, Cache, BaseXBar, BaseCache, CoherentXBar, ComputeUnit, ArmISA::TLB, System, Wavefront, AbstractMemory, Sinic::Device, IdeDisk, ClockedObject, TrafficGen, X86ISA::GpuTLB, TickedObject, NoncoherentXBar, CopyEngine, SnoopFilter, ElasticTrace, PowerISA::TLB, FALRU, BaseTags, FlashDevice, TLBCoalescer, BasePrefetcher, PowerModel, VoltageDomain, CacheMemory, QueuedPrefetcher, MessageBuffer, ClockDomain, Process, MipsISA::TLB, RiscvISA::TLB, Prefetcher, GPUCoalescer, GarnetNetwork, Router, HDLcd, ThermalDomain, RubySystem, AlphaISA::TLB, MathExprPowerModel, PowerModelState, AbstractController, CommMonitor, BPredUnit, MemTest, Switch, EtherDevice, Sequencer, MemFootprintProbe, SimpleNetwork, and StackDistProbe.

Definition at line 105 of file sim_object.cc.

Referenced by CxxConfigManager::instantiate(), StackDistProbe::regStats(), MemFootprintProbe::regStats(), BPredUnit::regStats(), AlphaISA::TLB::regStats(), ThermalDomain::regStats(), RiscvISA::TLB::regStats(), Prefetcher::regStats(), MipsISA::TLB::regStats(), Process::regStats(), ClockDomain::regStats(), CacheMemory::regStats(), VoltageDomain::regStats(), FlashDevice::regStats(), PowerISA::TLB::regStats(), ElasticTrace::regStats(), SnoopFilter::regStats(), ClockedObject::regStats(), IdeDisk::regStats(), Wavefront::regStats(), and ArmISA::TLB::regStats().

|

virtual |

Reset statistics associated with this object.

Reimplemented in Sinic::Device, GPUCoalescer, Router, RubySystem, AbstractController, Switch, and Sequencer.

Definition at line 110 of file sim_object.cc.

Referenced by Sinic::Device::resetStats().

|

inlineoverridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

| cp | Checkpoint state |

Implements Serializable.

Reimplemented in System, TickedObject, and VoltageDomain.

Definition at line 209 of file sim_object.hh.

Referenced by SrcClockDomain::serialize().

|

static |

Serialize all SimObjects in the system.

Definition at line 140 of file sim_object.cc.

References name(), Serializable::serializeSection(), and simObjectList.

Referenced by Serializable::serializeAll().

|

virtual |

startup() is the final initialization call before simulation.

All state is initialized (including unserialized state, if any, such as the curTick() value), so this is the appropriate place to schedule initial event(s) for objects that need them.

Reimplemented in DRAMCtrl, VirtIO9PSocket, VirtIO9PDiod, SrcClockDomain, DistEtherLink, RealViewOsc, DRAMSim2, MuxingKvmGic, ThermalModel, TsunamiIO, MaltaIO, EnergyCtrl, X86ISA::I8254, VoltageDomain, AlphaBackdoor, RubySystem, LinuxArmSystem, MathExprPowerModel, X86ISA::Cmos, CommMonitor, FreebsdArmSystem, and AlphaSystem.

Definition at line 97 of file sim_object.cc.

Referenced by MuxingKvmGic::startup(), and CxxConfigManager::startup().

|

inlineoverridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

| cp | Checkpoint state |

Implements Serializable.

Reimplemented in System, TickedObject, and VoltageDomain.

Definition at line 210 of file sim_object.hh.

Referenced by SrcClockDomain::unserialize().

|

protected |

Cached copy of the object parameters.

Definition at line 107 of file sim_object.hh.

Referenced by BasicRouter::params(), SimpleExtLink::params(), BasicLink::params(), X86ISA::I8237::params(), RiscvISA::Interrupts::params(), PowerISA::Interrupts::params(), MipsISA::Interrupts::params(), EtherObject::params(), MmDisk::params(), BadDevice::params(), DumbTOD::params(), EtherSwitch::params(), BaseGic::params(), Uart::params(), MemCheckerMonitor::params(), FaultModel::params(), EtherDevice::params(), X86ISA::Speaker::params(), AmbaFake::params(), IsaFake::params(), Network::params(), SouthBridge::params(), MemObject::params(), X86ISA::ISA::params(), SparcISA::Interrupts::params(), AlphaISA::Interrupts::params(), SimpleIntLink::params(), AbstractController::params(), EtherTapBase::params(), TsunamiPChip::params(), RealView::params(), CommMonitor::params(), BasicExtLink::params(), X86ISA::I8254::params(), ArmISA::Interrupts::params(), EtherBus::params(), BasicIntLink::params(), Sinic::Base::params(), MaltaCChip::params(), X86ISA::I8259::params(), X86ISA::I82094AA::params(), TsunamiCChip::params(), Uart8250::params(), Root::params(), Trace::ArmNativeTrace::params(), PL031::params(), AlphaBackdoor::params(), params(), MaltaIO::params(), RiscvISA::ISA::params(), PowerISA::ISA::params(), PioDevice::params(), TsunamiIO::params(), AlphaISA::ISA::params(), Iob::params(), Sp804::params(), IdeController::params(), EtherDevBase::params(), Pl050::params(), BasicPioDevice::params(), EtherLink::params(), EtherTapStub::params(), RealViewCtrl::params(), MipsISA::ISA::params(), CpuLocalTimer::params(), X86ISA::IntSinkPin::params(), CopyEngine::params(), X86ISA::IntSourcePin::params(), X86ISA::Walker::params(), VGic::params(), X86ISA::Interrupts::params(), SparcISA::ISA::params(), DistEtherLink::params(), X86ISA::IntLine::params(), X86ISA::I8042::params(), ClockedObject::params(), AbstractMemory::params(), LdsState::params(), NSGigE::params(), Pl390::params(), Pl111::params(), ArmISA::ISA::params(), ArmISA::TLB::params(), IGbE::params(), and ArmISA::TableWalker::params().

|

private |

Manager coordinates hooking up probe points with listeners.

Definition at line 103 of file sim_object.hh.

Referenced by getProbeManager(), SimObject(), and ~SimObject().

|

staticprivate |

List of all instantiated simulation objects.

Definition at line 100 of file sim_object.hh.

Referenced by find(), serializeAll(), and SimObject().