|

gem5

|

|

gem5

|

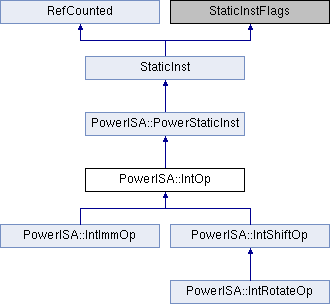

We provide a base class for integer operations and then inherit for several other classes. More...

#include <integer.hh>

Protected Member Functions | |

| IntOp (const char *mnem, MachInst _machInst, OpClass __opClass) | |

| Constructor. More... | |

| uint32_t | makeCRField (int32_t a, int32_t b, uint32_t xerSO) const |

| uint32_t | makeCRField (uint32_t a, uint32_t b, uint32_t xerSO) const |

| std::string | generateDisassembly (Addr pc, const SymbolTable *symtab) const |

| Internal function to generate disassembly string. More... | |

Protected Member Functions inherited from PowerISA::PowerStaticInst Protected Member Functions inherited from PowerISA::PowerStaticInst | |

| PowerStaticInst (const char *mnem, MachInst _machInst, OpClass __opClass) | |

| uint32_t | insertCRField (uint32_t cr, uint32_t bf, uint32_t value) const |

| void | printReg (std::ostream &os, int reg) const |

| Print a register name for disassembly given the unique dependence tag number (FP or int). More... | |

| std::string | generateDisassembly (Addr pc, const SymbolTable *symtab) const |

| Internal function to generate disassembly string. More... | |

| void | advancePC (PowerISA::PCState &pcState) const |

Protected Member Functions inherited from StaticInst Protected Member Functions inherited from StaticInst | |

| StaticInst (const char *_mnemonic, ExtMachInst _machInst, OpClass __opClass) | |

| Constructor. More... | |

Protected Attributes | |

| bool | rcSet |

| bool | oeSet |

| uint32_t | sh |

Protected Attributes inherited from StaticInst Protected Attributes inherited from StaticInst | |

| std::bitset< Num_Flags > | flags |

| Flag values for this instruction. More... | |

| OpClass | _opClass |

| See opClass(). More... | |

| int8_t | _numSrcRegs |

| See numSrcRegs(). More... | |

| int8_t | _numDestRegs |

| See numDestRegs(). More... | |

| RegIndex | _destRegIdx [MaxInstDestRegs] |

| See destRegIdx(). More... | |

| RegIndex | _srcRegIdx [MaxInstSrcRegs] |

| See srcRegIdx(). More... | |

| const char * | mnemonic |

| Base mnemonic (e.g., "add"). More... | |

| std::string * | cachedDisassembly |

| String representation of disassembly (lazily evaluated via disassemble()). More... | |

| int8_t | _numFPDestRegs |

| The following are used to track physical register usage for machines with separate int & FP reg files. More... | |

| int8_t | _numIntDestRegs |

| int8_t | _numCCDestRegs |

Additional Inherited Members | |

Public Types inherited from StaticInst Public Types inherited from StaticInst | |

| enum | { MaxInstSrcRegs = TheISA::MaxInstSrcRegs, MaxInstDestRegs = TheISA::MaxInstDestRegs } |

| typedef TheISA::ExtMachInst | ExtMachInst |

| Binary extended machine instruction type. More... | |

| typedef TheISA::RegIndex | RegIndex |

| Logical register index type. More... | |

Public Member Functions inherited from StaticInst Public Member Functions inherited from StaticInst | |

| int8_t | numCCDestRegs () const |

| Number of coprocesor destination regs. More... | |

| void | setFirstMicroop () |

| void | setLastMicroop () |

| void | setDelayedCommit () |

| void | setFlag (Flags f) |

| OpClass | opClass () const |

| Operation class. Used to select appropriate function unit in issue. More... | |

| RegIndex | destRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th destination reg. More... | |

| RegIndex | srcRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th source reg. More... | |

| virtual const StaticInstPtr & | eaCompInst () const |

| Memory references only: returns "fake" instruction representing the effective address part of the memory operation. More... | |

| virtual const StaticInstPtr & | memAccInst () const |

| Memory references only: returns "fake" instruction representing the memory access part of the memory operation. More... | |

| virtual | ~StaticInst () |

| virtual Fault | execute (ExecContext *xc, Trace::InstRecord *traceData) const =0 |

| virtual Fault | eaComp (ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual Fault | initiateAcc (ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual Fault | completeAcc (Packet *pkt, ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual void | advancePC (TheISA::PCState &pcState) const =0 |

| virtual StaticInstPtr | fetchMicroop (MicroPC upc) const |

| Return the microop that goes with a particular micropc. More... | |

| virtual TheISA::PCState | branchTarget (const TheISA::PCState &pc) const |

| Return the target address for a PC-relative branch. More... | |

| virtual TheISA::PCState | branchTarget (ThreadContext *tc) const |

| Return the target address for an indirect branch (jump). More... | |

| bool | hasBranchTarget (const TheISA::PCState &pc, ThreadContext *tc, TheISA::PCState &tgt) const |

| Return true if the instruction is a control transfer, and if so, return the target address as well. More... | |

| virtual const std::string & | disassemble (Addr pc, const SymbolTable *symtab=0) const |

| Return string representation of disassembled instruction. More... | |

| void | printFlags (std::ostream &outs, const std::string &separator) const |

| Print a separator separated list of this instruction's set flag names on the given stream. More... | |

| std::string | getName () |

| Return name of machine instruction. More... | |

| int8_t | numSrcRegs () const |

| Number of source registers. More... | |

| int8_t | numDestRegs () const |

| Number of destination registers. More... | |

| int8_t | numFPDestRegs () const |

| Number of floating-point destination regs. More... | |

| int8_t | numIntDestRegs () const |

| Number of integer destination regs. More... | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isCC () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isCondDelaySlot () const |

| bool | isThreadSync () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isMemBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isIprAccess () const |

| bool | isUnverifiable () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isMicroBranch () const |

Public Member Functions inherited from RefCounted Public Member Functions inherited from RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. More... | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. More... | |

| void | incref () |

| Increment the reference count. More... | |

| void | decref () |

| Decrement the reference count and destroy the object if all references are gone. More... | |

Public Attributes inherited from StaticInst Public Attributes inherited from StaticInst | |

| const ExtMachInst | machInst |

| The binary machine instruction. More... | |

Static Public Attributes inherited from StaticInst Static Public Attributes inherited from StaticInst | |

| static StaticInstPtr | nullStaticInstPtr |

| Pointer to a statically allocated "null" instruction object. More... | |

We provide a base class for integer operations and then inherit for several other classes.

These specialise for instructions using immediate values and also rotate instructions. We also need to have versions that consider the Rc and OE bits. Base class for integer operations.

Definition at line 51 of file integer.hh.

|

inlineprotected |

Constructor.

Definition at line 62 of file integer.hh.

|

protectedvirtual |

Internal function to generate disassembly string.

Implements StaticInst.

Reimplemented in PowerISA::IntRotateOp, PowerISA::IntShiftOp, and PowerISA::IntImmOp.

Definition at line 37 of file integer.cc.

References ccprintf(), and ArmISA::ss.

|

inlineprotected |

Definition at line 70 of file integer.hh.

References ArmISA::c.

|

inlineprotected |

Definition at line 83 of file integer.hh.

References ArmISA::c.

|

protected |

Definition at line 56 of file integer.hh.

|

protected |

Definition at line 55 of file integer.hh.

|

protected |

Definition at line 59 of file integer.hh.