|

gem5

|

|

gem5

|

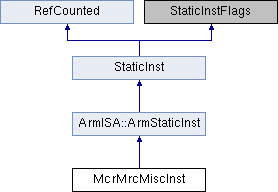

Certain mrc/mcr instructions act as nops or flush the pipe based on what register the instruction is trying to access. More...

#include <pseudo.hh>

Public Member Functions | |

| McrMrcMiscInst (const char *_mnemonic, ExtMachInst _machInst, uint64_t _iss, MiscRegIndex _miscReg) | |

| Fault | execute (ExecContext *xc, Trace::InstRecord *traceData) const |

| std::string | generateDisassembly (Addr pc, const SymbolTable *symtab) const |

| Internal function to generate disassembly string. More... | |

Public Member Functions inherited from ArmISA::ArmStaticInst Public Member Functions inherited from ArmISA::ArmStaticInst | |

| virtual void | annotateFault (ArmFault *fault) |

Public Member Functions inherited from StaticInst Public Member Functions inherited from StaticInst | |

| int8_t | numCCDestRegs () const |

| Number of coprocesor destination regs. More... | |

| void | setFirstMicroop () |

| void | setLastMicroop () |

| void | setDelayedCommit () |

| void | setFlag (Flags f) |

| OpClass | opClass () const |

| Operation class. Used to select appropriate function unit in issue. More... | |

| RegIndex | destRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th destination reg. More... | |

| RegIndex | srcRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th source reg. More... | |

| virtual const StaticInstPtr & | eaCompInst () const |

| Memory references only: returns "fake" instruction representing the effective address part of the memory operation. More... | |

| virtual const StaticInstPtr & | memAccInst () const |

| Memory references only: returns "fake" instruction representing the memory access part of the memory operation. More... | |

| virtual | ~StaticInst () |

| virtual Fault | eaComp (ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual Fault | initiateAcc (ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual Fault | completeAcc (Packet *pkt, ExecContext *xc, Trace::InstRecord *traceData) const |

| virtual void | advancePC (TheISA::PCState &pcState) const =0 |

| virtual StaticInstPtr | fetchMicroop (MicroPC upc) const |

| Return the microop that goes with a particular micropc. More... | |

| virtual TheISA::PCState | branchTarget (const TheISA::PCState &pc) const |

| Return the target address for a PC-relative branch. More... | |

| virtual TheISA::PCState | branchTarget (ThreadContext *tc) const |

| Return the target address for an indirect branch (jump). More... | |

| bool | hasBranchTarget (const TheISA::PCState &pc, ThreadContext *tc, TheISA::PCState &tgt) const |

| Return true if the instruction is a control transfer, and if so, return the target address as well. More... | |

| virtual const std::string & | disassemble (Addr pc, const SymbolTable *symtab=0) const |

| Return string representation of disassembled instruction. More... | |

| void | printFlags (std::ostream &outs, const std::string &separator) const |

| Print a separator separated list of this instruction's set flag names on the given stream. More... | |

| std::string | getName () |

| Return name of machine instruction. More... | |

| int8_t | numSrcRegs () const |

| Number of source registers. More... | |

| int8_t | numDestRegs () const |

| Number of destination registers. More... | |

| int8_t | numFPDestRegs () const |

| Number of floating-point destination regs. More... | |

| int8_t | numIntDestRegs () const |

| Number of integer destination regs. More... | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isCC () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isCondDelaySlot () const |

| bool | isThreadSync () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isMemBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isIprAccess () const |

| bool | isUnverifiable () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isMicroBranch () const |

Public Member Functions inherited from RefCounted Public Member Functions inherited from RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. More... | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. More... | |

| void | incref () |

| Increment the reference count. More... | |

| void | decref () |

| Decrement the reference count and destroy the object if all references are gone. More... | |

Private Attributes | |

| uint64_t | iss |

| MiscRegIndex | miscReg |

Additional Inherited Members | |

Public Types inherited from StaticInst Public Types inherited from StaticInst | |

| enum | { MaxInstSrcRegs = TheISA::MaxInstSrcRegs, MaxInstDestRegs = TheISA::MaxInstDestRegs } |

| typedef TheISA::ExtMachInst | ExtMachInst |

| Binary extended machine instruction type. More... | |

| typedef TheISA::RegIndex | RegIndex |

| Logical register index type. More... | |

Public Attributes inherited from StaticInst Public Attributes inherited from StaticInst | |

| const ExtMachInst | machInst |

| The binary machine instruction. More... | |

Static Public Attributes inherited from StaticInst Static Public Attributes inherited from StaticInst | |

| static StaticInstPtr | nullStaticInstPtr |

| Pointer to a statically allocated "null" instruction object. More... | |

Protected Member Functions inherited from ArmISA::ArmStaticInst Protected Member Functions inherited from ArmISA::ArmStaticInst | |

| int32_t | shift_rm_imm (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| int32_t | shift_rm_rs (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| bool | shift_carry_imm (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| bool | shift_carry_rs (uint32_t base, uint32_t shamt, uint32_t type, uint32_t cfval) const |

| int64_t | shiftReg64 (uint64_t base, uint64_t shiftAmt, ArmShiftType type, uint8_t width) const |

| int64_t | extendReg64 (uint64_t base, ArmExtendType type, uint64_t shiftAmt, uint8_t width) const |

| ArmStaticInst (const char *mnem, ExtMachInst _machInst, OpClass __opClass) | |

| void | printReg (std::ostream &os, int reg) const |

| Print a register name for disassembly given the unique dependence tag number (FP or int). More... | |

| void | printMnemonic (std::ostream &os, const std::string &suffix="", bool withPred=true, bool withCond64=false, ConditionCode cond64=COND_UC) const |

| void | printTarget (std::ostream &os, Addr target, const SymbolTable *symtab) const |

| void | printCondition (std::ostream &os, unsigned code, bool noImplicit=false) const |

| void | printMemSymbol (std::ostream &os, const SymbolTable *symtab, const std::string &prefix, const Addr addr, const std::string &suffix) const |

| void | printShiftOperand (std::ostream &os, IntRegIndex rm, bool immShift, uint32_t shiftAmt, IntRegIndex rs, ArmShiftType type) const |

| void | printExtendOperand (bool firstOperand, std::ostream &os, IntRegIndex rm, ArmExtendType type, int64_t shiftAmt) const |

| void | printDataInst (std::ostream &os, bool withImm) const |

| void | printDataInst (std::ostream &os, bool withImm, bool immShift, bool s, IntRegIndex rd, IntRegIndex rn, IntRegIndex rm, IntRegIndex rs, uint32_t shiftAmt, ArmShiftType type, uint64_t imm) const |

| void | advancePC (PCState &pcState) const |

| std::string | generateDisassembly (Addr pc, const SymbolTable *symtab) const |

| Internal function to generate disassembly string. More... | |

| Fault | disabledFault () const |

| Fault | advSIMDFPAccessTrap64 (ExceptionLevel el) const |

| Trap an access to Advanced SIMD or FP registers due to access control bits. More... | |

| Fault | checkFPAdvSIMDTrap64 (ThreadContext *tc, CPSR cpsr) const |

| Check an Advaned SIMD access against CPTR_EL2 and CPTR_EL3. More... | |

| Fault | checkFPAdvSIMDEnabled64 (ThreadContext *tc, CPSR cpsr, CPACR cpacr) const |

| Check an Advaned SIMD access against CPACR_EL1, CPTR_EL2, and CPTR_EL3. More... | |

| Fault | checkAdvSIMDOrFPEnabled32 (ThreadContext *tc, CPSR cpsr, CPACR cpacr, NSACR nsacr, FPEXC fpexc, bool fpexc_check, bool advsimd) const |

| Check if a VFP/SIMD access from aarch32 should be allowed. More... | |

| CPSR | getPSTATEFromPSR (ThreadContext *tc, CPSR cpsr, CPSR spsr) const |

| Get the new PSTATE from a SPSR register in preparation for an exception return. More... | |

Protected Member Functions inherited from StaticInst Protected Member Functions inherited from StaticInst | |

| StaticInst (const char *_mnemonic, ExtMachInst _machInst, OpClass __opClass) | |

| Constructor. More... | |

Static Protected Member Functions inherited from ArmISA::ArmStaticInst Static Protected Member Functions inherited from ArmISA::ArmStaticInst | |

| template<int width> | |

| static bool | saturateOp (int32_t &res, int64_t op1, int64_t op2, bool sub=false) |

| static bool | satInt (int32_t &res, int64_t op, int width) |

| template<int width> | |

| static bool | uSaturateOp (uint32_t &res, int64_t op1, int64_t op2, bool sub=false) |

| static bool | uSatInt (int32_t &res, int64_t op, int width) |

| static uint32_t | cpsrWriteByInstr (CPSR cpsr, uint32_t val, SCR scr, NSACR nsacr, uint8_t byteMask, bool affectState, bool nmfi, ThreadContext *tc) |

| static uint32_t | spsrWriteByInstr (uint32_t spsr, uint32_t val, uint8_t byteMask, bool affectState) |

| template<class XC > | |

| static Addr | readPC (XC *xc) |

| template<class XC > | |

| static void | setNextPC (XC *xc, Addr val) |

| template<class T > | |

| static T | cSwap (T val, bool big) |

| template<class T , class E > | |

| static T | cSwap (T val, bool big) |

| template<class XC > | |

| static void | setIWNextPC (XC *xc, Addr val) |

| template<class XC > | |

| static void | setAIWNextPC (XC *xc, Addr val) |

Protected Attributes inherited from ArmISA::ArmStaticInst Protected Attributes inherited from ArmISA::ArmStaticInst | |

| bool | aarch64 |

| uint8_t | intWidth |

Protected Attributes inherited from StaticInst Protected Attributes inherited from StaticInst | |

| std::bitset< Num_Flags > | flags |

| Flag values for this instruction. More... | |

| OpClass | _opClass |

| See opClass(). More... | |

| int8_t | _numSrcRegs |

| See numSrcRegs(). More... | |

| int8_t | _numDestRegs |

| See numDestRegs(). More... | |

| RegIndex | _destRegIdx [MaxInstDestRegs] |

| See destRegIdx(). More... | |

| RegIndex | _srcRegIdx [MaxInstSrcRegs] |

| See srcRegIdx(). More... | |

| const char * | mnemonic |

| Base mnemonic (e.g., "add"). More... | |

| std::string * | cachedDisassembly |

| String representation of disassembly (lazily evaluated via disassemble()). More... | |

| int8_t | _numFPDestRegs |

| The following are used to track physical register usage for machines with separate int & FP reg files. More... | |

| int8_t | _numIntDestRegs |

| int8_t | _numCCDestRegs |

Certain mrc/mcr instructions act as nops or flush the pipe based on what register the instruction is trying to access.

This inst/class exists so that we can still check for hyp traps, as the normal nop instruction does not.

| McrMrcMiscInst::McrMrcMiscInst | ( | const char * | _mnemonic, |

| ExtMachInst | _machInst, | ||

| uint64_t | _iss, | ||

| MiscRegIndex | _miscReg | ||

| ) |

Definition at line 186 of file pseudo.cc.

References StaticInst::flags, iss, and miscReg.

|

virtual |

Implements StaticInst.

Definition at line 196 of file pseudo.cc.

References ArmISA::EC_TRAPPED_CP15_MCR_MRC, iss, StaticInst::machInst, ArmISA::mcrMrc15TrapToHyp(), miscReg, ArmISA::MISCREG_CPSR, ArmISA::MISCREG_DCCMVAC, ArmISA::MISCREG_HCPTR, ArmISA::MISCREG_HCR, ArmISA::MISCREG_HDCR, ArmISA::MISCREG_HSTR, ArmISA::MISCREG_SCR, NoFault, and ExecContext::readMiscReg().

|

virtual |

Internal function to generate disassembly string.

Implements StaticInst.

Definition at line 219 of file pseudo.cc.

References csprintf(), and StaticInst::mnemonic.

|

private |

Definition at line 127 of file pseudo.hh.

Referenced by execute(), and McrMrcMiscInst().

|

private |

Definition at line 128 of file pseudo.hh.

Referenced by execute(), and McrMrcMiscInst().